LDPC FEC成为无线回程的首选技术

描述

不断增加的数据速率与有限的频谱相结合,需要 LDPC FEC 等技术来帮助跟上步伐。

在过去的几年里,无线行业对使用低密度奇偶校验 (LDPC) 码的前向纠错 (FEC) 的兴趣激增。在每秒千兆位传输速率和信道容量物理限制的时代,每一个有用的信息比特都有自己的价值。LDPC FEC 已被证明是一种有效的系统组件,可以以非常高的成本提高传输鲁棒性。在这种情况下,电信网络的每个元素都必须高效设计,这将具体适用于无线数据传输,它具有与频谱资源的可用性相关的限制。

理论最大信道容量遵循 Claude Shannon 早在 1948 年引入的著名定理。根据他的定理,存在使噪声信道中的操作能够任意接近理论信道容量的代码。从那以后,这个公式引起了很多人的兴趣和围绕搜索能够在香农容量附近进行操作的代码的实际工作。

有趣的是,1963 年 Robert G. Gallager 在他的开创性博士论文 Low Density Parity Check Codes 中已经提出了这种高效的代码。大约在这个时候,引入了 Reed-Solomon 和 Bose-Chaudhuri-Hocquenghem (BCH) 码,早在 Turbo 码出现之前。然而,LDPC FEC通过使用码字比特估计的多次迭代以及相当大的矩阵需要很高的计算复杂度,因此在提出这些代码时,他们没有找到任何实际的实现。

LDPC 码是线性的,具有稀疏奇偶校验矩阵。这些属于设计用于在奇偶校验矩阵的行和列中包含低密度“1”的块代码类。使用稀疏分布的奇偶校验架构背后的意图是应用概率独立的 XOR 计算,奇偶校验值的估计值在奇偶校验矩阵的每一行中聚合,并且每次后续迭代都会改进估计值。在估计收敛并纠正所有错误之前可能需要数十次迭代。然而,确切的迭代次数由代码设计者根据特定代码需要在其中运行的系统的应用程序和规范来确定。在确定满足特定系统规范所需的最小迭代次数之前,可以进行许多权衡。现代 LDPC FEC 使用软判决算法,进一步提高解码器增益。

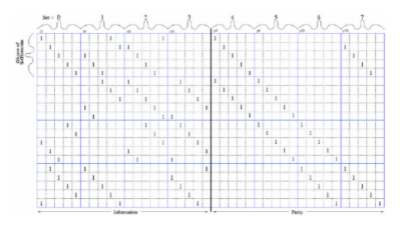

随着更大的块长度N,纠错能力的置信度增加。但是,它通过增加奇偶校验矩阵的大小来增加计算复杂性,从而增加估计每个位所需的计算次数(图 1)。

图 1:示例 LDPC 奇偶校验矩阵。

使用大块和迭代的另一个问题是延迟增加,因为这些计算是逐块进行的。由于处理和内存资源有限,这将成为在延迟敏感的应用程序(例如语音通信)中使用 LDPC 码的关键约束。另一个例子是 3GPP-LTE 中的混合自动重复请求 (HARQ) 传播时间要求,它将往返时间限制为 5 ms,而基带用户设备处理引入的延迟将消耗该延迟预算的很大一部分。随着新的 Cloud RAN 架构和无线被考虑用于前传,这种延迟预算对于规划无线调制解调器中使用的 FEC 的设计限制变得至关重要,这通常是整个信号处理链中最大的延迟贡献者。

在 2003 年引入 DVB-S2 卫星广播标准后,在无线通信中采用 LDPC FEC 的实际商业突破发生了。在之前的 DVB 标准中使用的卷积编码上,使用 LDPC FEC 将阈值增益提高了大约 3dB,并能够迁移到更高的频谱效率。七到八年后,LDPC FEC 开始进入无线回程链路,随着 3G 的出现以及随后的数据流量爆炸和回程瓶颈挑战,更高的频谱效率已成为重要的设计目标。现在,它已成为回程无线链路设计的事实标准。

由于与 50 年前相同的限制,强大的 LDPC FEC 码的设计仍然是一项复杂的任务。自然地,可以实现这些代码的硬件平台在此期间实现了巨大的飞跃,即使计算能力大大增加,设计也必须具有功率和成本效益,并与大多数其他功能模块集成在一起。负责沟通。此外,带宽需求已显着增加,现在我们需要能够处理更高的吞吐量。因此,在设计 LDPC 码时,需要在确定架构时在无数不同的优化练习之间取得平衡,以保持低延迟、低功耗和低成本的良好性能。

与 DSP 不同,FPGA 为 LDPC 编码器和解码器所需的计算类型提供了高度并行的结构。该 IP 具有高度可配置性,允许用户选择不同级别的并行度来优化解码器大小,还可以定制解决方案以支持各种通道带宽。LDPC FEC 具有可扩展性,支持窄微波波段(3.5 至 112 MHz)到真正宽的毫米波段(250 Hz 至 1,000 MHz)。所谓的多层编码技术简化了 LDPC FEC 架构,并保持代码库的大小和功耗在低端 FPGA 平台上可行。

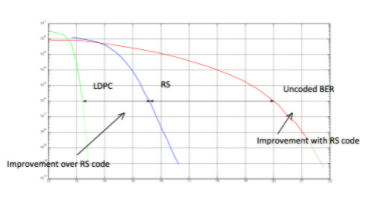

Xilinx 的 FEC 代码中使用的特殊 X 解码算法已经以较少的迭代次数实现了显着的 SNR 增益,从而导致更好的解码器延迟。图 2 展示了 LDPC FEC 码与 RS FEC 相比的示例性能。平均而言,根据码率、码字长度和迭代次数,相对于 RS 码有 2 到 4 dB 的改进。下面的示例在高数据速率下使用低编码开销。

图 2:基于 RS 和 LDPC FEC 的 BER 与 SRN 性能。

FEC 通常与同一 FPGA 上的无线调制解调器和数据包处理模块一起实现,以从完整的基带集成中受益。通常,由于与平台无关的设计实践和传统的 ASIC 转换,这些设计往往太大而无法从采用价格合理的 FPGA 中受益。Xilinx 的 1+Gbps LDPC FEC 编码器和解码器 SmartCORE IP 解决了这一设计挑战,支持将 FEC IP 与调制解调器和数据包处理一起使用。

LDPC 的研究将继续进行,我们可以期待这些代码在不同的通信场景中会发现更多的适用性。我们很可能会看到在新一代 CMTS 和数据中心系统中采用低密度奇偶校验技术。但它们可能会出现在未来的 5G 标准中,其中正在审查更高频率和单载波波形的使用。

审核编辑:郭婷

-

FEC前向纠错技术:让无线传输“自我修复”的通信卫士2026-01-09 1335

-

蓝牙Mesh模块组网时无线回程影响速率吗?2024-05-23 2141

-

什么是前向纠错(FEC)?FEC最全解析2023-01-13 7752

-

什么是FEC技术?FEC方案的性能主要由哪些因素决定?2021-05-24 3458

-

如何利用5G WiFi波束成形和LDPC技术提高无线连接性能?2021-05-21 1510

-

TrueAdvantage无线接入解决方案实现向真正回程融合升级2020-06-03 1528

-

基于5G WiFi波束成形和LDPC技术提高无线连接性能2019-06-13 2359

-

小型蜂窝的无线回程容量解决方案2018-11-27 3933

-

Halow技术能否成为智能家居通信首选2018-11-14 2460

-

技术简介:MACOM无线回程产品组合和解决方案2018-09-05 2084

-

为有线网络建立无线回程2017-06-16 1995

-

高速通用LDPC码译码技术2013-07-26 1069

-

Xilinx收购无线回程解决方案商Modesat Communications2012-09-18 805

全部0条评论

快来发表一下你的评论吧 !