影响PCB阻抗的主要因素 PCB设计50欧姆阻抗控制的原因

描述

为什么很多工程师用 50Ohm PCB 传输线,有些时候这则成为 PCB 布线的默认设置。为什么不是 60 Ohm 或者 70 Ohm?

在线宽固定的情况下,有三个主要因素影响PCB的阻抗。

第一,到PCB传输线最近的电磁干扰层的影响正比于PCB传输线到最近的参考平面的距离,越小的距离就越小的辐射。

第二,串扰也随传输线的厚度有则明显的变化,减少一半的传输线厚度将减少传输线串扰。

第三,越小的距离产生越小的阻抗,这个有利于减少容性负载的影响。所有的三个因素鼓励设计者去设计传输线更加靠近参考平面。阻止传输线厚度降为0的主要原因是大部分的芯片不可能很好的驱动小于50 Ohm的传输线,除了Rambus 27Ω,旧的国家BTL联盟17Ω。

并不是所有的用50Ω做阻抗控制都是最好的。如:旧NMOS8080处理器工作频率100Khz的时候没有电磁干扰和串扰以及容性负载的问题,同时在任何时候他也不可能驱动50Ω的传输线.就这个处理器而言,由于高的阻抗将减小驱动电源,故我们必须使用我们能制造出来的最薄的,最高的阻抗的传输线.

同时我们也要考虑机械问题(制程问题)。如,在高密度多层板的高压合夹层空间下,70Ω的传输线在现在微小印刷技术下很难被制造出来,在这种情况下,你也许会转而用50Ω的传输线,50Ω的传输线允许用比70Ω更宽的线宽,从而使电路板存在可制造性。

那同轴电缆线的阻抗又如何呢?在射频的世界里,考量的问题点与印刷电路板又有不同,至今射频工业还是关注与相似阻抗的同轴电缆线,根据国际电工协会出版物78(1967), 75Ω是一个非常容易被接受的同轴阻抗标准,因为你能更加容易的匹配几种比较流行的天线结构。它同时定义了50Ω的实心聚乙烯线的结构,即给出了固定的外层屏蔽层的直径,同时给出了固定的介电常数2.2。因为在50Ω先可以减小传输过程中的趋肤效应。

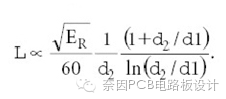

同时你可以从物理学定理上证明50Ω同轴电缆线阻抗的优越性。电缆趋肤效应损失为L(每单位长度上)正比于趋肤效应电阻R(每单位长度)除以电缆的特性阻抗Z。电缆总的趋肤电阻为外层屏蔽层电阻加上内层传输线电阻之和。在高频下,屏蔽层的串接趋肤电阻反比与它的直径d2。内层传输线的串联趋肤电阻反比与它的直径d1.则总的串接电阻正比于(1/d2+1/d1).结合上述因素,相互介电常数ER,屏蔽层直径d2 为给定的固定值,你能下面这个公式来最小化趋肤效应的损失,

在任何初级电磁场电磁波课本里,你都能找到如下的公式:Z0 表示为d2, d1, 和ER:的公式

将公式2代入公式1,则可得公式三如下

从公式三分离常数项((√ER/60 )(1/d2)),变量((1+d2/d1)/ln(d2/d1))决定趋肤损失最小化的点,仔细检查公式三,发现最小损失的点只与d2/d1 的比有关,与ER 和固定的d2都无关。

将L作为自变量d2/d1的一个函数,一个可操作的结构显示最小损失点为d2/d1=53.5911.假设一个固体的聚乙烯绝缘体的介电常数为2.25,相当于波的传播速度为光的66%。d2/d1=53.5911.用于公式二可得传输线的特性阻抗为51.1Ω,很久以前,无线电工程师坚决的仅仅使同轴线的阻抗达到更方便的50Ω。这不意味你就必须用50Ω。如,如果你设计了一个75Ω的传输线,此线有相同的外层屏蔽层直径和介电常数,其趋肤损失仅增加了12%,不同的介电常数材料的可以优化d2/d1的值,从而产生优化的阻抗。

原文标题:为什么很多PCB传输线的阻抗都是50欧姆

文章出处:【微信公众号:奈因PCB电路板设计】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

PCB设计阻抗不连续的原因及解决方法2024-03-21 1874

-

pcb板阻抗控制是指什么?pcb怎么做阻抗?2024-01-17 5479

-

PCB上常用50Ω阻抗的主要原因2023-04-14 1581

-

PCB为什么常用50Ω阻抗?6大原因2023-04-06 2573

-

请问PCB价格的主要因素有哪些?2021-04-21 1980

-

PCB设计为何控制50欧姆阻抗?2020-01-15 11644

-

PCB设计中的阻抗控制和叠层设计问题分析2019-08-08 5410

-

走线选择50欧姆阻抗有以下原因2019-05-31 2427

-

分析影响PCB阻抗的主要因素和阻抗影响不同程度2019-01-18 24259

-

基于PCB设计的阻抗控制实现2018-10-14 2050

-

PCB设计中为什么特性阻抗线只有50欧姆和100欧姆两个值?2011-11-28 6297

-

PCB加工中影响阻抗因素2006-04-16 2632

全部0条评论

快来发表一下你的评论吧 !