PT32x00x电源控制器简介

电子说

描述

3 电源控制(PWR)

3.1 综述

PWR 列举了芯片内部与电源相关的所有资源,包括内部的电源电压调节器、可编程的电源电压监测器、低功耗模式。

3.2 特性

l 集成的电源调节器,提供 3 路内部电源、均可通过 ADC 内部通道进行访问:

u BG1v5 1.5V 精度 5%

u BG1v2 1.2V 精度 5%

u BG1v0 1.0V 精度 0.5%

l 多挡位、支持复位或中断的可编程电源电压检测器

l 在低功耗模式下,提供两种低功耗模式:

u 睡眠模式

u 深度睡眠模式

l 深度睡眠下、典型功耗仅为 0.8uA

3.3 电源调节器

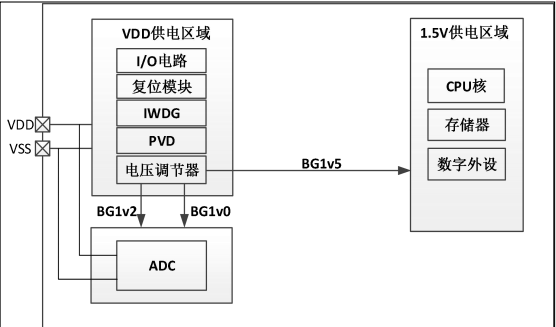

PT32x00x 支持在超宽电压范围内工作、工作电压(VDD)详见《PT32x00x 数据手册》。通过内置的电源调节器提供内部所需的 1.5V 电源 BG1v5、1.2V 参考电源 BG1v2 以及 1.0V 参考电源 BG1v0。所有的内部电源均可通过 ADC 内部通道进行访问、详见 ADC(控制寄存器 ADC_CR)的”CHS”位描述。

3.3.1 电源调节器

复位后电源调节器总是使能的。根据系统运行状态、它以 2 种不同的模式工作。

1.运行模式:调节器以正常功耗模式提供 BG1v5、BG1v2、BG1v0 三路电源;BG1v5 作为核 心电源共给内部 CPU、存储器和数字外设,并且与 BG1v2、BG1v0 一起接入 ADC 的内部模拟通道中.

2.低功耗模式:提供睡眠和深度睡眠两种低功耗模式,电源调节器将递进的关闭片内电源、时钟、外设,以使系统功耗大大降低。

3.3.2 电源复位条件

PT32x00x 内部有一个完整的上电复位(PUR)和掉电复位(PDR)电路,当 VDD 电压达到工作电压时系统就能正常工作。 当 VDD 低于指定的限位电压 VPUR/VPDR时,系统保持为复位状态。

3.3.3 可编程的电源电压监测器(PVD)

用户可以利用 PVD 对 VDD 电压进行监测,(电源电压监测器配置寄存器 PWR_PVDR)中的”PLS”位用于设定 PVD 监控 VDD 电压的阈值。通过将(PWR_PVDR 寄存器)中的 PVDE 位置’1’以使能 PVD。

PVD 事件支持用户通过复位和中断两种形式进行访问,其对应的中断事件在内部被连接到 NVIC 的第 20 号中断,如果该中断在系统中断使

能寄存器 ISER 中被使能,一旦发生该事件、NVIC 就会响应 PVD 的中断请求。PVD 事件的触发/解除机制由硬件自动控制,当 VDD 下降到”PLS 位”所设定的阈值时,PVD 中断被触发,当 VDD 上升到 PVDUV 时,PVD 中断被解除。这一特性可用于用于执行紧急关闭任务。

3.4 低功耗模式

系统或电源复位以后,系统处于运行模式。当系统无需继续运行时,可以利用多种低功耗模式来节省功耗;例如等待某个外部事件时,用户可以根据最低电源消耗、唤醒时间和可用的唤醒源等条件,选定一个最佳的低功耗模式。

PT32x00x 提供了两种低功耗模式:

l 睡眠状态(Cortex™-M0 内核停止,但包括 Cortex-M0 核心的外设在内的所有外设,如 NVIC、SysTick 等仍在运行,IFMC 无法访问)

l 深度睡眠状态(除 LSI 外的所有时钟均已停止工作,相关的片内电源以及外设被强制关闭)。此外,在运行模式下,还可以通过以下方式降低功耗:

l 失能未被使用的时钟源

l 失能未被使用但已被使能的外设。

l 将不使用的 GPIO 做内部下拉处理

3.4.1 进入低功耗模式

通过将配置系统控制寄存器(SCR)中的 SLP 位置’1’以选定系统进入低功耗模式时、系统处于睡眠状态还是深度睡眠状态。系统进入低功耗模式有两种方法:

l 执行 WFI 或 WFE 指令以进入低功耗模式

l 将系统控制寄存器(SCR)中的 SOE 位置’1’,当系统从最低优先级的中断处理程序中退出时,立即进入低功耗模式

注意:进入低功耗模式前,应该将所有未使用到的管脚配置为下拉输入,并清除所有管脚的复用功能可使系统功耗得到最大优化。

3.4.2 睡眠状态

表 3-1 罗列了系统处于睡眠状态时、片内资源的工作状态。如需优化功耗、在进入睡眠状态前,用户可手动关闭无需在低功耗模式下工作的外设以降低功耗。

3.4.3 深度睡眠状态

表 3-1 罗列了系统处于深度睡眠状态时、片内资源的工作状态。在深度睡眠状态下,只有 LSI 时钟挂载的外设可以正常运行,内核的寄存器、内存的信息仍保存,程序在唤醒后仍从上一次停止处执行;除表 3-1 所罗列的在深度睡眠状态下被强制关闭外设外,其他外设均不会被强制关闭,在运行模式下使能的外设、在进入深度睡眠前应该手动关闭以避免额外功耗;如需进一步的优化功耗,可将 LSI 时钟关闭,但 LSI 时钟挂载外设将无法工作,此时、低功耗

模式的唤醒仅支持外部中断唤醒。

注意:GPIO 外部中断唤醒深度睡眠时,仅支持双沿中断、高电平中断和低电平中断。

3.4.4 唤醒方式

当系统处于低功耗模式时,如果是睡眠状态,根据进入低功耗模式的指令,有相应的唤醒方式:

l WFI 指令:任意一个被 NVIC 响应的外设中断都能将系统从睡眠模式唤醒。

l WFE 指令:包括所有中断在内、所有内核支持的事件特别地、当(系统控制寄存器 SCR)的”SWC”位为’1’时:所有中断或事件均可唤醒。

注意:使用 WFE 唤醒睡眠状态,需要在(中断挂起清除寄存器 ICPR)中清除相应的挂起标志。

如果是深度睡眠状态,根据进入低功耗模式的方法,有相应的唤醒方式:

l WFI 指令:LSI 时钟挂载外设的中断或者外部中断

l WFE 指令:LSI 时钟挂载外设的中断、外部中断、复位事件或调试模式请求事件特别地、当(系统控制寄存器 SCR)的”SWC”位为’1’时:LSI 时钟挂载外设的中断、外部中断、复位事件或者调试模式请求事件均可唤醒。

审核编辑:汤梓红

-

PT32L007x系列微控制器2025-11-19 1295

-

PT32Y003/X003系列32位通用微控制器2026-01-04 481

-

基于实时时钟芯片X1228的电源控制器设计2009-05-12 613

-

MSP430x11x混合信号微控制器特性和功能描述2009-06-29 928

-

PT8A351X系列智能电熨斗控制器的应用设计2010-03-05 3001

-

MSP430X13X,MSP430X14X混合信号微控制器2017-09-21 741

-

TMS320x280x/2801x增强控制器区域网络(eCAN)2018-04-12 1174

-

STM32F030x4/x6/x8微控制器手册2023-03-13 1053

-

MSP430x43x MSP430x43x1 MSP430x44x混合信号微控制器数据表2024-08-06 1104

-

CC3x00电源管理优化和措施2024-09-26 430

-

UCC25661x-Q1:高性能LLC控制器的技术解析与应用指南2026-03-01 834

-

MSP430x43x/44x系列混合信号微控制器深度剖析2026-03-06 1364

-

深入剖析MSP430F15x/16x/161x混合信号微控制器2026-03-09 759

-

深入解析 MSP430F524x 和 MSP430F523x 混合信号微控制器2026-04-21 416

-

VICOR PI354x-00 ZVS调节器:高效电源解决方案2026-04-27 371

全部0条评论

快来发表一下你的评论吧 !