明明设计的是高带宽,差点加工成开路

电子说

描述

作者:一博科技高速先生成员 黄刚

有没有感觉最近只看到了东哥的文章,是不是一度以为我们**了呢。没有啦,在这里还是要郑重的和广大的粉丝们解释下,高速先生这段时间一直在积累一些很有趣的素材,学习一些新的技术,以便给大家看到更多富有启发性的文章,这不我们又来了吗!

说回正题哈,作为我们高速先生的主业也就是SI,其实一直以来我们都很关心设计和加工出来的差异,尤其对于高速信号来说,高速先生只有在加工误差比较小的情况下,才能去很好的完成一些仿真和测试的拟合。刚好高速先生正在研究一些适合112G的超高宽带传输的设计,PCB设计完加工回来后,高速先生立马投入到了紧张的测试中,结果就有了本文开头那一幕的感慨。。。

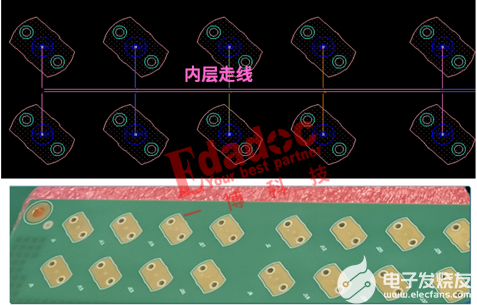

当我们测试到一对带1.85同轴连接器的内层走线时,测出了让我们意想不到的结果。设计就是一对差分线,我们主要是看看一款高速板材的损耗和加上同轴连接器后,链路的带宽和线性度能去到多高频率。

我们首先关注下同轴连接器位置的阻抗和差分线的阻抗,第一反应,感觉还是不错的,尤其是走线,整个链路的阻抗都在±5%以内,虽然不能算特别优秀,但是心理至少能接受的那种。

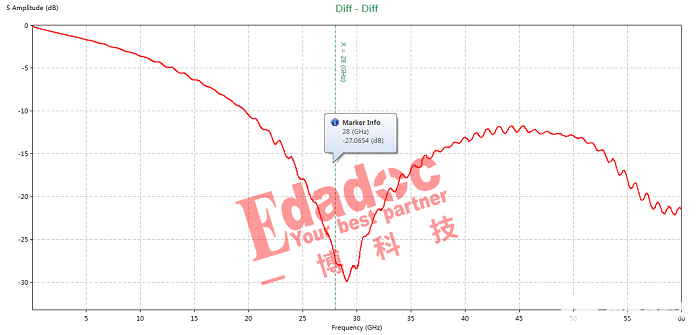

然而当我们测到插损曲线的时候,整个人都不好了,这啥啊这,居然平平无奇的一对差分走线会有那么大的谐振点,在28GHz的位置就和开路没什么两样啦!

于是我们首先怀疑的是设计,看看是不是在PCB设计上犯了一些很低级的错误,结果查了设计文件,压根就没问题嘛,线宽线距,等长都没问题啊!

这就奇怪了,一开始高速先生是怀疑是不是漏了背钻,因此毕竟是3mm的板子,我们这对差分线走到了很靠上的层,但是从差分的TDR阻抗就已经排除了我们的想法,因为全链路上都没有一些很低的阻抗点,如果是漏背钻的话,肯定会在阻抗上看出问题的!

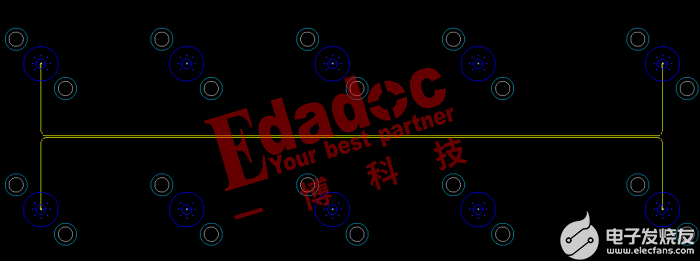

那到底是什么问题呢?于是我们把重点放在差分线P和N单端延时差的问题,于是我们把这对差分的P和N分别给一个阶跃信号,来从时域上看看它们的延时到底有没有差别。结果让高速先生大跌眼镜,P和N之间的延时差居然有0.17?不对,1.7?也不对,是17.5ps!!!

如果你对ps这个单位没什么概念的话,高速先生转成mil你就知道有多夸张了,就是大概100mil的长度差,也就是说,设计上是完全等长的两根线,加工出来居然有100mil的长度差,最关键的是走线长度还不到3inch。

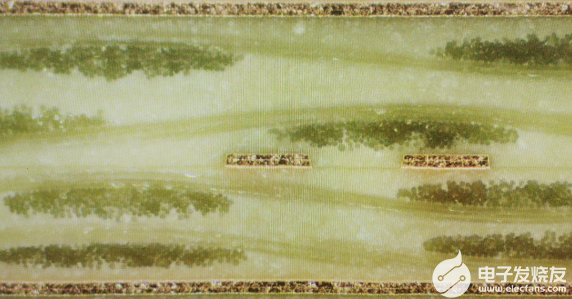

通过上面的测试和分析,其实高速先生大概率想到了是玻纤效应影响造成的,具体什么是玻纤效应,就不在这里展开了,可以翻看之前很多期的文章都有提到哈。于是我们把板子拿到板厂做了下切片,以便更好的和我们的预想贴合。不一会,切片图就出来了,果然,就是这个问题了。

可能有部分的粉丝没看过PCB切片图,其实就是在和走线垂直的剖面切开,用高倍显微镜来看切面的画面。就像本文的这张切片图一样,可以看到差分走线刚好一根走在了玻纤的交叠区域(右),另外一根走线窗口处(左),而且不知道算是多大分之一概率的机会,上下都各有两张pp(core也是两张pp组成),而且pp也还是扁平布的情况下,依然无法阻挡差分的P和N处于比较一致的状态。另外只要是知道了玻璃布和胶的介电常数差异,你就会明白这种情况有多严重了。

要不就这样结尾了,高速先生已经哭倒在实验室了。。。

问题来了

从设计到加工环节,大家觉得有什么细节的方法可以改善玻纤效应吗?

审核编辑:符乾江

-

OPA365芯片明明增益带宽50MHz,为什么噪声密度曲线只到100KHz,后面频率就没了呢?2024-08-21 309

-

什么是带宽?带宽是越宽越好吗?#硬声创作季电子学习 2023-02-09

-

高带宽、高频发送器参考设计2015-05-11 2438

-

高增益与高带宽怎么兼得2018-09-20 1894

-

高增益与高带宽怎么兼得?2018-09-21 2583

-

恢复高带宽探头测量的信心2019-08-05 1360

-

怎么才能判断高带宽测量探头的质量?2019-08-08 1889

-

STM32明明是32位的CPU却将定时器设计成16位的2021-09-09 1212

-

从设计到加工环节,大家觉得有什么细节的方法可以改善玻纤效应吗?2022-06-30 32494

-

如何解决厚铜PCB加工过程中的开路或短路问题?2023-04-11 857

-

N76E003 I/O口接一个10K的电阻到10v的电源,设置成开路输出模式并设置输出高,会有电流流过电阻吗?2023-06-26 575

-

高带宽实时示波器芯片组2009-12-18 724

-

HBM高带宽内存是什么2018-11-10 35353

-

开路电压是什么_开路电压怎么求2020-08-14 59589

-

为什么电路带宽不能设计成无穷大?2023-09-20 1738

全部0条评论

快来发表一下你的评论吧 !