JESD204C标准的介绍和新功能

描述

许多行业的数据密集型应用程序继续推动快速有效地交付有效负载数据的界限。5G 通信网络在基础设施及其连接组件中采用需要更多带宽的系统。在航空航天和国防工业中,这意味着在雷达应用和复杂数据分析仪器中可以在更短的时间内处理更多信息。相关地,对带宽快速扩展的测试和分析转化为电子测试设备对更高速度和容量的需求。

对数据不断增长的需求导致 JEDEC 固态技术协会需要引入最新的 JESD204 标准,用于数据转换器和逻辑器件之间的高速串行链路。该标准的 B 修订版于 2011 年发布,将串行链路数据速率推至 12.5 Gbps,并确保从一个电源周期到下一个电源周期的确定性延迟,同时满足当时基于转换器的应用的更高带宽要求。该标准的最新版本 JESD204C 于 2017 年底发布,以继续支持这一和下一代多千兆数据处理系统的性能要求的上升趋势。JESD204C 小组委员会为新版标准制定了四个高级目标:增加通道速率以支持更高带宽应用程序的需求,提高有效载荷传递的效率,并提供改进的链路稳健性。此外,他们希望编写一个比 JESD204B 更清晰的规范,同时修复该版本标准中的一些错误。还希望提供与 JESD204B 向后兼容的选项。完整的 JESD204C 规范可通过杰德克。

这本由两部分组成的入门读物作为对 JESD204C 标准的介绍,重点介绍了与 JESD204B 的区别,并详细介绍了旨在满足前述目标的关键新功能,并在提供各种所需的带宽能力的同时提供更友好的用户界面的行业。本系列的第一部分提供了这些差异和新功能的高级视图。第 2 部分将深入探讨最重要的新功能。

总结 JESD204C 的变化

JESD204C 规范经过组织以提高可读性和清晰度,它包括五个主要部分。“简介和通用要求”部分涵盖了适用于所有实施层的要求。物理层、传输层和每个数据链路层(8b/10b、64b/66b 和 64b/80b)的部分涵盖了专门适用于这些实施层的要求。整个标准中引入了几个新术语,主要与新的 64b/66b 和 64b/80b 链路层以及这些链路层的新同步过程相关。虽然传输层在 JESD204B 中保持不变,但物理层发生了相当大的变化。上述变化,

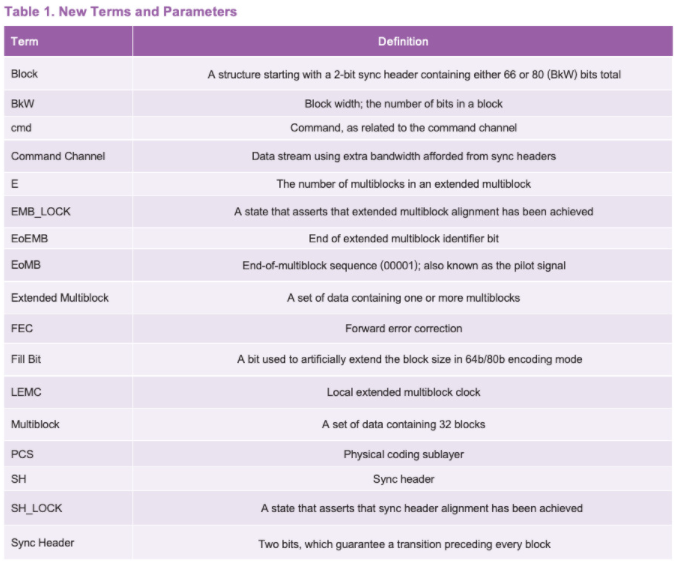

新术语

JESD204C 中引入了几个新术语和配置参数,主要用于描述与 64b/66b 和 64b/80b 链路层相关的功能。表 1 列出了最相关的术语和参数以及每个的简要说明。这些将在以下部分中进一步描述。

传输层

对于 JESD204C,传输层与 JESD204B 保持不变。在传输层中组装的数据帧以 8 字节块的形式通过链路发送。对标准的这一部分进行了组织、文本和图形的更改,以提供更高的清晰度。

由于 64 位编码方案的性质,在某些配置中,帧边界不会与块边界对齐(帧可能不完全包含八个八位字节)。这方面的细节和影响将在本系列的第 2 部分中介绍。

数据链路层

如前所述,该标准有两个主要部分涵盖不同的数据链路层方案。来自 JESD204 标准先前版本的 8b/10b 编码方案,包括使用 SYNC~ 引脚和使用 K.28 字符进行同步、通道对齐和错误监控,作为向后兼容的选项保持不变。但是,从长远来看,大多数应用程序可能会使用 JESD204C 中添加的新 64 位编码方案之一。64b/66b 方案将提供最高效率并基于 IEEE 802.3。虽然它被称为编码,但实际上并没有进行任何编码(类似于 8b/10b)。该方案只是将两个标头位添加到 64 位有效负载数据中。既然是这样,加扰是强制性的,以保持直流平衡并确保足够的转换密度,以便 JESD204C 接收器中的时钟和数据恢复 (CDR) 电路能够可靠地恢复时钟。这将在本系列的第 2 部分。还添加了 64b/80b 选项,该选项保持与 8b/10b 方案相同的时钟比率,同时允许使用前向纠错等新功能。这两种 64 位编码方案都不兼容 JESD204B 中使用的 8b/10b 编码。

物理层

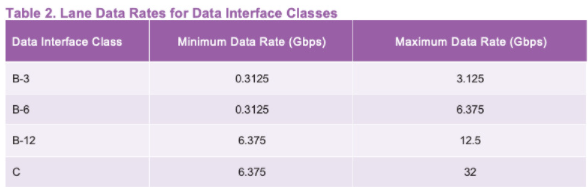

JESD204C 已将通道速率的上限提高到 32 Gbps,同时保持早期版本中建立的 312.5 Mbps 的下限。JESD204B 中的上限为 12.5 Gbps。虽然没有严格禁止,但不建议对高于 16 Gbps 的通道速率使用 8b/10b 编码,也不建议对低于 6 Gbps 的通道速率使用 64b 方案。

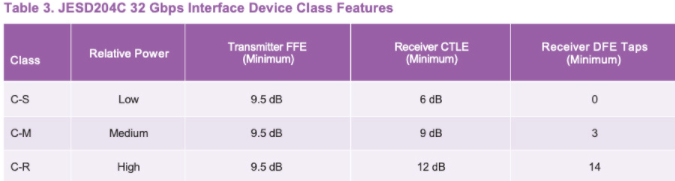

JESD204C 引入了两类类来定义物理接口的特性。表 2 列出了与每个类别相关的车道速率。表 3 列出了 C 类中的信道类型以及相关的加重和均衡特性。

JESD204C 还引入了 JESD204 通道工作裕度 (JCOM) 的概念,用于确认符合 C 类 PHY 层标准。这种工作裕度计算补充了应用本标准和之前的标准修订版中描述的 B 类 PHY 层实现的眼图模板。

时钟和同步

JESD204C 将保留 JESD204B 中定义的 SYSREF 和器件时钟的使用。然而,当使用任一 64 位编码方案时,SYSREF 不是对齐 LMFC,而是用于对齐本地扩展多块计数器 (LEMC),以提供确定性延迟和多芯片同步的机制。

64 位编码方案的同步过程与 JESD204B 中使用的完全不同。SYNC 信号已被消除,同步初始化和错误报告现在将在应用层软件中处理。因此,没有代码组同步 (CGS) 或初始通道对齐序列 (ILAS)。同步标头同步、扩展多块同步和扩展多块对齐是用于描述同步过程的与同步相关的新术语。这些同步阶段中的每一个都是使用 32 位同步字实现的。这将在本系列的第 2 部分中详细讨论。

请注意,对于 8b/10b 编码,SYNC 引脚和 ILAS 都被保留。

确定性延迟和多芯片同步

如上所述,实现确定性延迟和多芯片同步的机制在 JESD204B 中基本保持不变。当使用 64 位编码方案之一时,没有子类 2 选项。相反,仅支持子类 1 操作,并且 SYSREF 信号用于在 JESD204 子系统中的所有设备上对齐 LEMC。

前向纠错

为了实现以更高通道速率提供更强大链路的目标,JESD204C 中包含了 FEC 选项。该算法基于防火规范,可能对仪表应用特别有用。这是一项可选功能,仅在使用 64 位编码方案之一时可用。

火灾代码是纠正单脉冲错误的循环代码。循环码的优点是它们的码字可以表示为有限域上的多项式,而不是向量。火灾代码使用一个可以分成两个组件的综合症,以便更快地解码。

更多信息

在即将推出的 JESD204C 入门系列的第 2 部分中,我们将深入探讨 JESD204C 标准的关键要素,这些要素支持我们在开头段落中描述的问题解决技术。具体来说,64b/66b 编码方案实现的带宽效率改进与增加带宽的 32 Gbps 物理层规范一样被仔细研究。新的同步过程以及标准的可选前向纠错方面也提供了更多深度,以提高链路的鲁棒性。

审核编辑:郭婷

-

JESD204标准解析2019-06-17 3392

-

JESD204C标准值得注意的新特性2020-12-28 1601

-

JESD204C的标准和新变化2021-01-01 3027

-

JESD204C入门第2部分:新特性及其内容2019-09-12 7668

-

JESD204C入门第二部分:新特性及其内容2020-12-26 1565

-

Intel AN-916 (AD9081/AD9082 JESD204C Interoperability with Stratix 10)2021-01-30 1212

-

LTC6952:超低抖动、4.5 GHz PLL,带11个输出和JESD204B/JESD204C支持数据表2021-04-22 1190

-

LTC6953:超低抖动、4.5 GHz时钟分配器,带11个输出和JESD204B/JESD204C支持数据表2021-05-19 1112

-

JESD204C标准的新特性和问题解决方案2022-06-30 4302

-

AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet2023-10-16 73

-

TI AFE8092/AFE8030 JESD204C配置及调试手册 Part C2024-08-29 679

-

从JESD204B升级到JESD204C时的系统设计注意事项2024-09-21 1071

-

基于AFE79xx的JESD204C应用简述2024-09-27 680

-

TSW14J59EVM JESD204C数据采集和图形发生器卡2024-11-09 389

-

LTC6953具有11个输出并支持JESD204B/JESD204C协议的超低抖动、4.5GHz时钟分配器技术手册2025-04-16 1339

全部0条评论

快来发表一下你的评论吧 !