PCB Layout对热阻的影响

电子说

描述

为了满足更小的方案尺寸以降低系统成本,小型化和高功率密度成为了近年来DCDC和LDO的发展趋势,这也对方案的散热性能提出了更高的要求。本文借助业界比较成功的中压DCDC TPS543820,阐述板上POL的热阻测量方法及SOA评估方法。

PCB Layout对热阻的影响

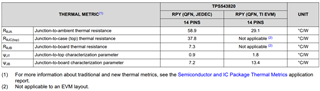

芯片的数据手册都会标注芯片的热阻参数,如下Figure 1 TPS543820 Thermal Information所示。但这个Thermal Metric的值并不能直接应用于实际项目的热评估中,因为芯片的散热好坏会受到PCB layout的直接影响,包括散热面积,铜厚,过孔数量甚至是布局都会对实际热阻造成较大影响。

Figure 1: TPS543820 Thermal Information

因此,我们需要对项目中重点电源器件进行实际热阻测量,尤其是在高温应用场景下,以避免设计问题导致的芯片可靠性降低甚至无法正常工作。

板上热阻RθJA测量

测试设备

电源

示波器

电子负载

温箱

热电偶

万用表

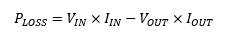

测试方法

固定输出电压(VOUT),利用电源提供输入电压电流(VIN,IIN),利用电子负载提供负载电流(IOUT),利用温箱来创造稳定的环境温(TA)。逐步缓慢的增加负载电流,同时利用示波器监测输出电压,当输出电压在超过10分钟的时间里恰好只出现了1次shutdown,那么我们认为此时芯片的结温 TJ = TSDN(thermal shutdown point)。

如Figure 2所示,芯片的TSDN可以从手册中找到,但这个点的范围比较广,下面介绍两种单颗芯片TSDN的测量方法,以得到更精确的结果。

Figure 2: TPS543820 Thermal Shutdown Spec

1)使用热电偶或红外测温仪测量恰好发生一次thermal shutdown时的壳温(Tcase),利用结温到壳温之间的特征热阻较小的特性,近似认为此时TCASE=TSDN。

2)利用PGOOD NMOS体二极管的阈值电压VTH和温度的负线性关系,保持芯片不上电,用万用表测量不同环境温度下的PGOOD和AGND之间的电压差(VTH),两点确定一条直线,绘制出此时的VTH与温度的特性曲线。再次给芯片上电,测量恰好发生一次thermal shutdown时的VTH值,即可反推出此时的PGOOD NMOS温度(TPG),由于PGOOD NMOS受到了功率MOSFET的加热,我们认为此时TPG=TSDN。

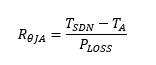

热阻计算公式

其中,

因此,我们可以求得此时板上的热阻。下面我们将介绍如何利用板上热阻进行评估SOA。

SOA评估

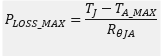

我们利用TPS543820EVM的RθJA结果进行分析,如Figure 1所示,RθJA=29.1℃/W,假设应用条件为VIN=12V, VOUT=5V, Fsw=1MHz, TA_MAX=90℃,从TPS543820数据手册6.3节中可以得到芯片推荐工作最大结温TJ=150℃,因此,可以利用下面的公式求得当前应用条件下芯片正常工作的最大功耗PLOSS_MAX:

计算得到,PLOSS_MAX=2.06W,从TPS543820数据手册中Figure 6-6中可以直接查出此时对应的输出电流为7.5A。因此,我们可以得到在当前应用条件下,芯片可以正常工作的最大输出电流为7.5A,所以该路电源应设计满足IOUT_MAX≤7.5A。

审核编辑:汤梓红

-

PCB Layout热设计指导2025-06-06 457

-

干货!PCB Layout 热设计指导2024-09-20 2598

-

什么是PCB热阻 因素有哪些2024-05-02 3860

-

影响pcb基本热阻的因素有哪些2024-01-31 2200

-

PCB Layout过孔散热设计2023-08-07 5843

-

LFPAK MOSFET热阻——PCB布局的仿真、测试和优化-AN900192023-02-17 533

-

PCB铜皮的面积和热阻是什么2023-02-16 6292

全部0条评论

快来发表一下你的评论吧 !