FPGA中实现信号延时的资源消耗

FPGA/ASIC技术

描述

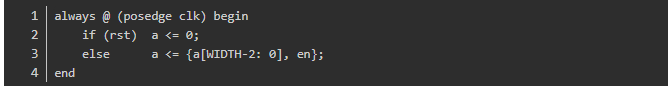

在FPGA设计中我们经常会遇到对一个信号进行延时的情况,一般只延时一个或几个CLK时,通常是直接打拍,如果要延时的CLK较多时,我们会选择移位寄存器IP核,而有时为了方便,我们常常会使用下面的方式

前段时间我临时对一个脉冲信号延时8192个CLK就使用了这种写法,当时有意识到可能会消耗较多的资源,但没想到会这么多。

不同方式实现延时的资源消耗对比

还是对一个脉冲信号延时8192个CLK,为了对比不同方式的资源消耗,我新建了一个工程

平台:Cyclone V

软件:Quartus 18.1 standard

对比了三种实现方式

计数8192个时钟,重新产生一个脉冲

移位寄存器IP核(Memory实现)

对该信号打8192拍(寄存器实现)

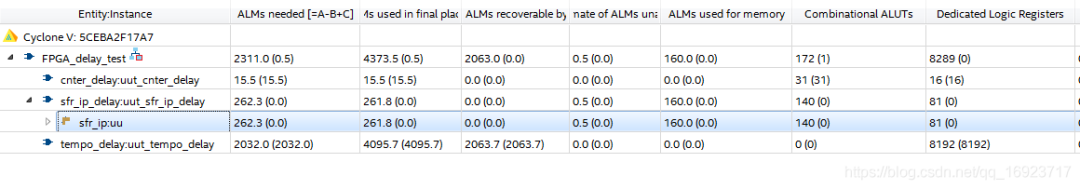

资源消耗情况如下图所示。

可以看到计数器消耗的资源是最少的,因为它相当于只存储一个bit的信息,不像其他两种方式把8192个时钟的信息都存储了,这算是一种取巧的方式,能应用的场合比较少。

打8192拍的方式使用资源最多,用了2032个ALM,ALM是Altera器件的最小逻辑单元,一个ALM包含4个寄存器。因为要打8192拍,所以可以看到这里消耗了8192个寄存器。实际上打拍并没有用到任何的组合逻辑(LUT),但是因为寄存器和LUT是绑定到ALM中的,所以一旦寄存器被消耗,同时LUT也很难应用到其他逻辑中。像这里,8192个寄存器需要2048个ALM(图中是2032),这2048个ALM中的LUT就被浪费掉了(我不是很确定,需要进一步研究,但是从资源消耗的情况来看,应当是这样的)。所以这种方式是最不经济的,除非要延时的时钟很少或者是调试代码,否则不建议总是采用这种方式。

移位寄存器IP消耗的资源相对比较适中,只使用了262个ALM,相当于是把ALM配置成了Memory,像是Xilinx器件中的SRL。实现时资源设置的是Auto,如果设置为M10K的话,是下面这样的。可以看到使用一个M10Ks的Block Memory,而ALM就只消耗了14个。实际设计时可根据芯片哪种资源余量更大选择哪种。

总结

从上面的实验可以看到,直接打拍的方式是非常浪费资源的,所以如果要延时的CLK较多,建议采用IP核的方式,在使用IP核方式时根据剩余资源选择合适的资源来实现。而在某些特殊情况,可以考虑采用计数器的方式来实现,这种方式消耗的资源最少,但是如果不是要延时特别多的CLK,则不建议,因为这种方式在时序变化时难以维护。

打拍延时是可以的,但是不要复位,像下面这样写,综合工具可以推断使用Memory来实现。经测试,这种写法与IP核的资源消耗是差不多的(还是会比ip多一点点),这样就可以很方便的实现信号delay了。xilinx的器件也是一样,不要复位。

这里综合后显示的是使用了一个M10K。还可以加上综合属性,强制使用MLAB实现。

如果一个系统里有很多这样没有复位的Memory的话,在复位系统时,需要将复位信号拉的长一点,保证复位过后的信号冲掉Memory中的残留数据,否则系统会有出错的风险。

-

FPGA程序中内存的实现方式2022-07-10 2646

-

Xilinx FPGA时钟资源概述2023-07-24 1603

-

如何在FPGA中实现高效的compressor加法树呢?2023-11-08 2984

-

基于单片机与FPGA可调延时模块的设计2019-09-25 1678

-

简谈FPGA设计中不同设计方法资源消耗对比2023-05-31 1382

-

利用FPGA延时链实现鉴相器时钟数据恢复2011-03-15 1413

-

数字信号处理的FPGA实现2015-12-23 1056

-

FPGA中丰富的布线资源2017-12-05 1090

-

利用单片机和FPGA实现系统中可延时调节模块的设计2019-04-22 4315

-

在FPGA中利用IP核实现SOC系统中的串口收发接口的设计2019-08-02 5665

-

浅析如何评估FPGA的资源2019-02-15 4412

-

如何评估FPGA的资源2020-12-28 1245

-

FPGA架构中的全局时钟资源介绍2021-03-22 15367

-

FPGA 结构分析 -IO 资源2022-12-13 3442

-

X+32和X+1谁消耗的FPGA资源多2023-09-20 1849

全部0条评论

快来发表一下你的评论吧 !