ARM架构的关键能力

描述

作者简介

十四年IT基础设施研发经验,其中包括六年Linux kernel一线研发经验,在suse,华为,星际比特(技术合伙人)等公司工作。

作为团队核心成员参与了大陆第一个Cortex-A8 SOC芯片研发,负责CPU软件验证,操作系统移植等工作。

作为华为派驻到Linaro的技术专家,主导/参与多个Linux与arm架构相关特性研发(ILP32,continuous bit hint,kernel selftest等)

在拉斯维加斯,柏林,布达佩斯和北京多次发表技术演讲

2022年6月6日,WWDC 2022,苹果推出了新的Macbook Air和Macbook Pro,最大支持24G内存和2T存储,支持8k视频,支持18-20小时的续航,价格分别是1199美元和1299美元起。二者都适用了苹果最新自研的M2芯片。

作为底软的吃瓜群众,迫不及待的想把air拆开,一探究竟,无奈囊中羞涩。只好隔着屏幕一探M2的究竟。健哥整理了M1和M2的部分特性(表格横屏查看):

| SOC | M1 | M2 |

| Architecture | ARM v8.5 | ARM v8.5 |

| CPU | 4xFirestorm 4xIcestorm | 4xAvalanche 4xBlizzard |

| Memory | 8G/16G lpddr4 | 8/16/24G lpddr5 |

| Transister | 16 billion | 20 billion |

| Product | MacBook Air/Pro 2020 | Macbok Air/pro 2022 |

| Release Date | 2020 | 2022 |

资料来源:Apple公司官网,整理人:健哥。原始表格:https://fvot4kwt4n.feishu.cn/sheets/shtcn69s9nbcvYxX0bAnDgxiAUb

M2使用了和A15一样的两个CPU IP Avalanche,Blizzard,分别作为性能核心和能效核心。二者组成大小核,会根据系统需要,选择合适的CPU,平衡性能和功耗。ARM公司官方的最新大小核技术称为DynamIQ。很遗憾,健哥暂时没有查到苹果大小核技术的更多信息,希望以后有机会向大家分享。

可以看到M2支持了更大的内存和更好的带宽。资料显示,M2使用了LPDDR5 6400,带宽可以到达100G。BTW,很多手机使用了LPDDR5,例如华为Mate P40,小米10,带宽大约在30-40G。

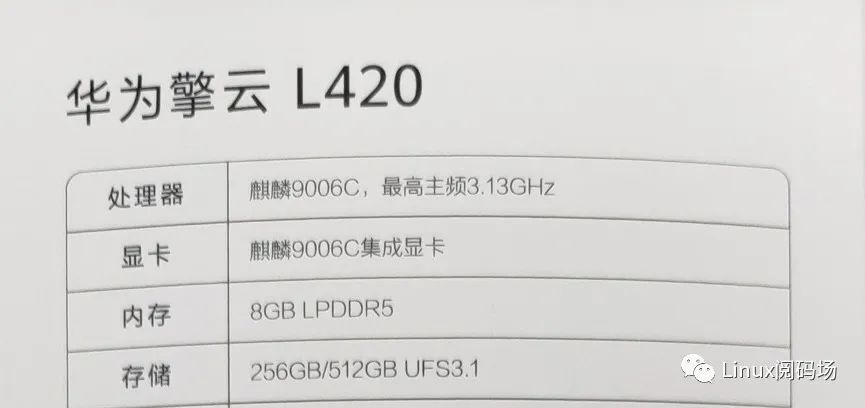

健哥查到的第一个使用LPDDR5的笔记本是华为的擎云L420,这个笔记本使用了华为麒麟9006C SOC。该芯片也采用了5nm工艺,最高频率3.13GHz。某东8+256的版本是7999元。

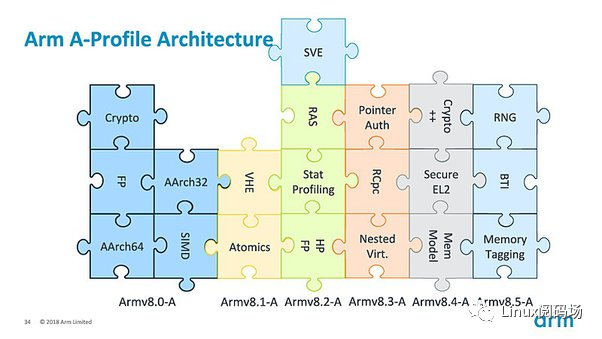

想了解一个ARM CPU,最为核心的是知道这个CPU的架构,根据网上的资料,M2的CPU是支持ARMv8.5扩展的。ARM从v8开始,除了v8,v9的大版本,还有若干小版本。目前最新的是v8.8和v9.3。虽然v8.5不是最新的ARM架构,但是v9.0除了SVE2,CCA,其余和v8.5是一样的。很多很多年之后,即使没有ARMv8a处理器了,今天学习的v8.5特性,也是未来继续跟踪ARM架构发展的很好的切入点。

从上图可以看到v8.5的主要增强有:

MTE: Memory Tagging Extension;

BTI: Branch Target Identification;

随机数生成器;

增强对PMEM的支持。

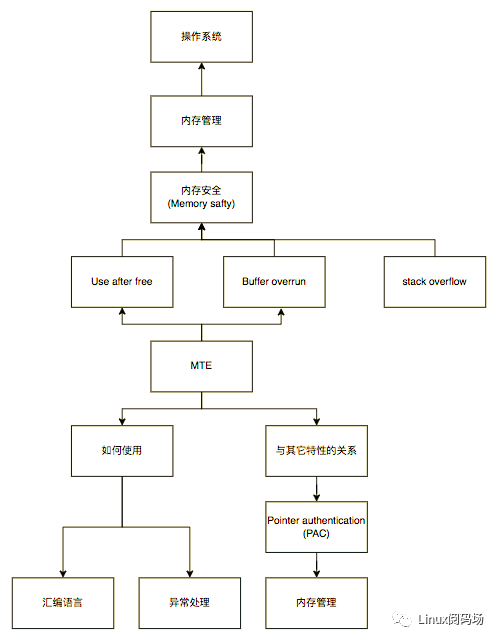

Memory Tagging Extension,顾名思义,是一个tag相关的特性。它使用了虚拟地址是不使用的位作为tag,可以用于use-after-free和buffer overrrun两个内存安全特性。

Branch Target Identification:从名字上可以看出,这是一个和跳转相关的特性,作用是在页表,PSTATE和BTI指令的配合下,检查是否发生了预期之外的跳转。如果是预期之外的跳转,会触发异常。

随机数生成器是引入了RNDR,RNDRRS两条指令。

对PMEM的支持:增加了PoDP,PoDP可以保证即使硬件故障导致了断电,Persistent memory的数据不会出错。

除了第三个特性,其它三个看起来都有点复杂,其实用健哥上次直播介绍的ARM架构三大基石(汇编,异常和内存)和三步学习方法(理解原理,阅读代码,实验验证),咱们都能化繁为简。

比如BTI特性,由三部分组成

页表中的GP位,用于设置是否是guarded page。这背后是对页表的基本理解;

BTI指令用于指定检查的规则。例如是否可以跳转的动态链接库。这背后是汇编语言的基本语法和过程调用标准(APCS64);

PSTATE.BTYPE位用于在guarded区域(上面所说guarded page的区域)的指令是否产生异常。

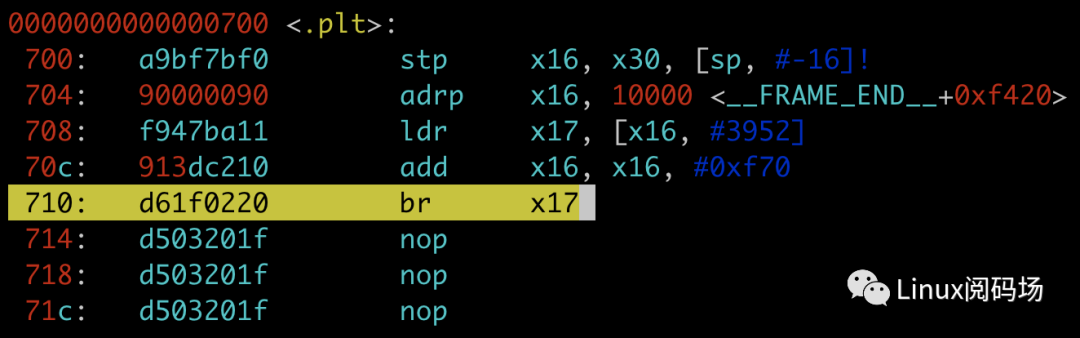

可以看到,理解BTI特性需要从汇编,异常和内存三方面配合理解。有了上面的初步了解,再结合原本plt的代码代码(下图),我们可以想象在打开BTI特性的情况下,如果是guarded区域,br指令如果访问了x16, x17之外的寄存器,会产生异常。

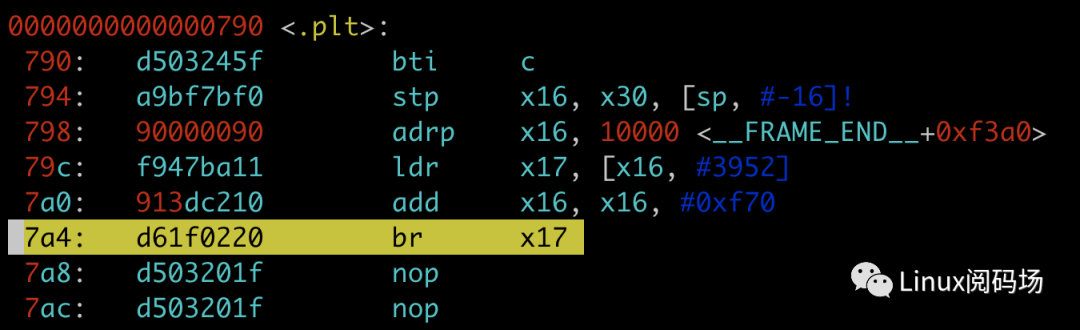

编译器使能bti后,我们的确能看到0x790行插入了bti c指令。

对于MTE也是一样的,学习MTE特性是对三大基石的巩固和提高,然后我们可以借助对于MTE的了解,更多的理解软硬件如何配合,近可以看看操作系统下为内存安全还做了哪些事情,远可以更多学习操作系统的内存管理知识,从而更深理解操作系统。

在课程中,我们会和今天一样,先从软硬件系统的整体出发到ARM CPU,然后聚焦在汇编,异常和内存三部分,每一部分都有三个学习要点,每个要点都通过原理,代码和实验三部分打通。打通之后,我们通过对于更深入特性的拆解,验证前面的学习效果。欢迎大家报名我的ARM工作坊,我带大家一起打通和爆破ARM架构的关键能力。

原文标题:Apple M2和ARMv8.5特性

文章出处:【微信公众号:Linux阅码场】欢迎添加关注!文章转载请注明出处。

-

ARM内核和架构都是什么意思,它们到底是什么关系?2016-07-24 3571

-

转:ARM内核和架构都是什么意思,它们到底是什么关系?2016-07-28 2893

-

我对ARM架构的理解2020-09-03 3695

-

ARM与RISC-V架构的区别是什么?2021-04-25 6521

-

ARM架构是什么2021-07-01 1732

-

ARMARM的架构与ARM架构的区别2021-07-16 1416

-

ARM芯片架构2021-07-28 2534

-

ARM架构2021-08-04 2440

-

ARM架构_-_介绍2016-05-24 1085

-

什么叫arm架构_X86架构与ARM架构有什么区别2018-04-24 87736

-

一文看懂arm架构和x86架构有什么区别2018-05-16 315848

-

基于ARM架构的上网本解决方案2018-12-03 643

-

ARM架构是什么 限制ARM对华为的影响2019-08-14 9393

-

为什么要使用Arm架构2019-12-16 3962

-

Arm架构科普解读 Arm架构的底层逻辑和Arm架构的顶层设计2023-02-06 8488

全部0条评论

快来发表一下你的评论吧 !