MOS的C-V曲线与衬底浓度以及GOX特性的关系

电子说

描述

KIA MOS管

使用C-V曲线查Case

随着半导体制程越来越复杂,我们最关键的参数Vt的控制越来越重要,有的时候我们的Vt如果单纯是衬底浓度影响我们自然可以通过长沟和短沟以及NMOS和PMOS是否同时变动来确定是否是GOX还是Vt_IMP的问题,其实这也是一种correlation它其实是一种逻辑思考方式,只是他是基于理论的。

本文来讨论下MOS的C-V曲线与衬底浓度以及GOX特性的关系,这样大家既可以用它来评估GOX特性,也可以用C-V曲线来判定Vt 的Case是由于什么造成的,其实同时也是为了介绍这个MOS晶体管的栅极结构的C-V特性,既有助于我们理解这个理论,又可以用实际案例来验证。

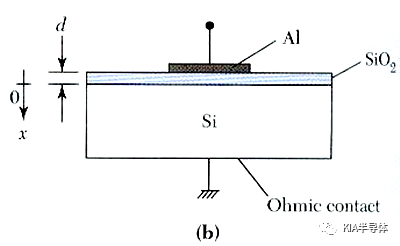

讲到MOS电容,他的结构就是Gate-Oxide-Semiconductor的夹心电容结构,其实就是高中物理讲的平板电容结构。而我们实际的平板电容的C-V特性下的电容式恒定值,因为电容公式高速我们电容只和介电常数以及厚度和面积相关,所以和电压无关。不过MOS结构的电容会随着电压的变化而变化。

MOS-Cap的电容结构很简单,忽略源漏极就只剩下Gate-Oxide-Semiconductor(Well)了。所以叫MOS,也叫MIS(Metal-Insulator-Semiconductor)。

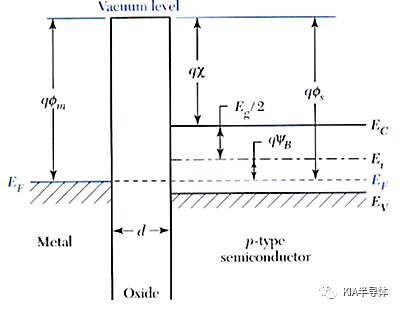

介绍这样的MOS-C的结构之前,先介绍一个概念平带电压(Vfb, Flat-Band Voltage)。当栅极无偏压时候,理想情况下金属功函数qΦm与半导体功函数qΦs的能量差应该为零,也就是金属和半导体的功函数差qΦms等于零。也就是说零偏压下,能带是平的所以叫做平带。而在栅极接正电压或负电压,则半导体一边的能带会受到下拉或上移影响而弯曲。

下面我们以PWELL (NMOS-C)为例,先讨论这样的MIS结构下的三种特性:

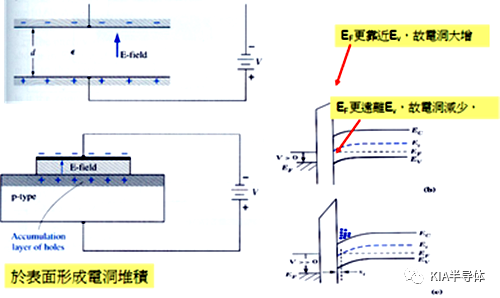

1)当栅极偏压(Vg)小于0V时候,此时沟道由于电场感应出多子空穴堆积在表面,故称之为积累区(Accumulation)。

2)当Vg>0时,此时沟道开始感生出电子,先消耗掉原来Pwell的空穴,所以称之为耗尽区(Depletion)。

3)当Vg进一步增大, Vg>>0V时,沟道已经产生过量的电子反型出N型。此时为反型区(Inversion),而沟道深度就是我们的反型区宽度。

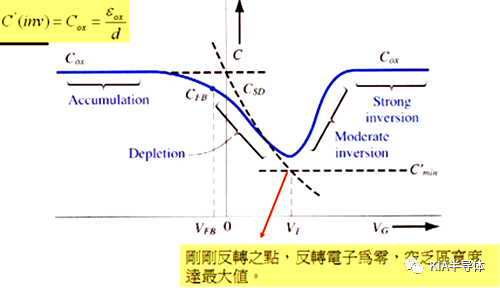

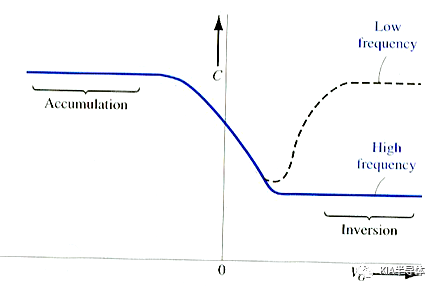

所以根据上面的介绍,我们介绍各自的电容特性,并且画出Poly-Oxide-PWELL (NMOS-C)的电容-电压(C-V)特性曲线如下图:

1) 在积累区,由于衬底是PWELL,而积累的也是P-type,所以下电极只是导电特性变好,所以所有的栅极电压全部加在GOX上,所以此时电容最大。

2)在耗尽区,随着栅极电压从积累区逐渐开始增大,沟道逐渐开始产生耗尽区,所以此时电压是加在GOX和耗尽区连个串联的电容上面,所以电容逐渐开始减小。

3)在反型区,也就是Vg大于开启电压时,此时耗尽区宽度达到最大值,所以进入强反型,这个时候的电容达到最小值。

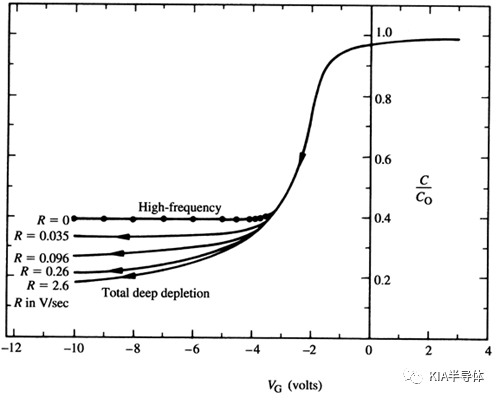

当然还有个不容忽略的问题是我们的测试电压的频率,当频率较低时,载流子的速度可以跟的上电压频率的变化,所以此时的反型区是被充电的最终还是达到GOX的厚度。

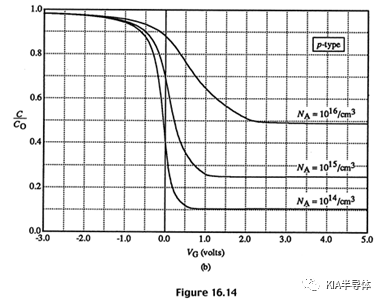

而如果是高频,载流子速度根本赶不上反型区充电速度,所以只能保持在低电容状态。而实际上这个反型区宽度与衬底浓度是有很大关系的(这个可能用Vt与衬底浓度的关系来理解,所以完全可以通过反型区高频电容特性来判断衬底浓度的变化~)

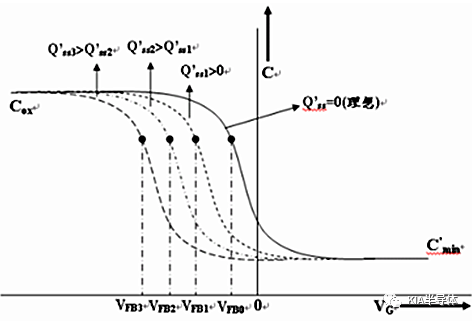

当然,上面讲的都是理论情况,也就是平带为零的情况。而实际上平带不可能为零,因为我们的金属与半导体功函数是有差的,而且氧化层本身也会有电荷。

所以实际下半导体的能带是默认已经弯曲的,所以我们一直有个平带电压测试就是使得金属与半导体的能带由弯曲还原到平带状态下的电压就叫做平带电压(Vfb),也是我们评估栅极氧化层的重要指标。

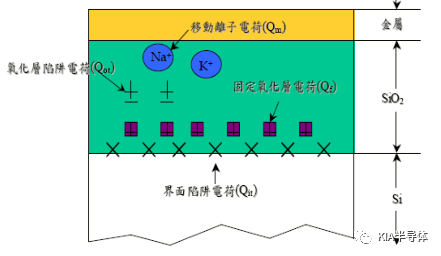

通常栅氧中,氧化层缺陷是影响它电性的主要因素,而这些缺陷主要来自以下四种:

1) 界面陷阱电荷(Qit: Interface Trapped Charge),它主要位于Si与SiO的界面处,主要由于氧化过程中未找到氧键的Si的悬挂键,它可以俘获电子或空洞,所以可以带正电或负电。

可以通过适当的回火(Anneal)或者Alloy来降低硅悬挂键的浓度,或者选用<100>晶向的硅片(知道为啥CMOS用<100>的了吧)。

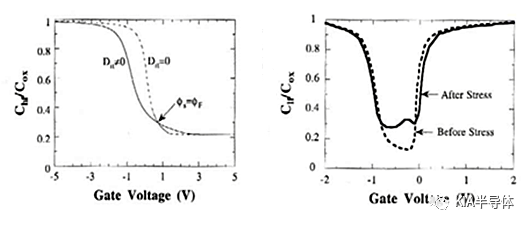

在C-V特性曲线上,高频电容与施加电压有关,Qit对高频信号不做回应所以不会改变,它只会对多余电荷的补充和消耗做出响应(dVg/dt),所以在耗尽区扭曲。

2) 氧化层固定电荷(Fixed Oxide Charge, Qf)。主要分布在距离Si/SiO2界面约2nm内,主要由于氧化过程或结束后回火条件不合理导致部分硅没有完全氧化产生硅正离子,由于这样的正离子电荷存在,所以会导致C-V曲线里面平带电压的位移。

3) 氧化层陷阱电荷(Oxide Trapped Charge, Qot)。它主要是由于离子辐射、FN隧穿、或者热载流子效应造成的缺陷捕获电子或空穴,故氧化层陷阱电荷既可以是正的也可以是负的还可以是电中性的。

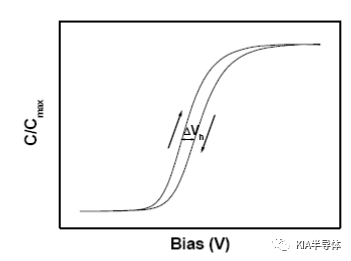

主要与氧化层品质有关,通常可以通过回火来消除俘获电荷使其变成电中性(Neutual Trap)。由于捕获电荷会由于初始加的电压为正或为负导致不同,所以可以根据高频C-V曲线的正向扫描以及反向扫描的C-V的曲线来看是否含有Qot。

这种由于初始电压不同造成的俘获载流子的不同回路称之为迟滞现象(Hysteresis Effect)。我们可以据此来判断氧化层捕获的电荷型态以及数量。

4) 可移动离子电荷(Qm, Mobile ionic Charge)。主要来自人体或纯水中的碱金属离子(Na+, K+),或者湿氧水汽里面的H+进入氧化层,或者是氧化层中缺少氧而造成O++氧空位。这个东西主要是影响平带电压(Vfb)。

以上讲的是GOX的电荷对C-V曲线的影响,当然影响C-V曲线的因素还有以下方面。

1) 频率:我们之前将高频由于载流子来不及响应,所以keep在最低了,而低频在反型区电容也是最大值,所以频率越低,反型区越向上平移。(当然实际case过程中,我们都是fix 频率比如100MHZ去测量的)。

2) 衬底浓度:这个主要是跟反型区宽度决定的,衬底浓度越高,越难反型,所以反型区宽度越窄,所以电容变大,所以电容曲线也向上移动。

再讲一个深耗尽(Deep Depletion)的概念,这个主要跟测试方法相关的。如果我们栅极电压慢慢往上扫描,如果扫描速度过快,则反型层还来不及反型并达到热平衡状态,这就是我们说的深耗尽,这种情况下耗尽区宽度会持续增加,而导致电容进一步降低。所以可以尝试减小扫描step,并优化Hold/wait time。

原文标题:使用C-V曲线查Case

文章出处:【微信公众号:KIA半导体】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

NMOS管的特性曲线(一)— 输出特性曲线详解2023-12-01 23204

-

三极管与MOS管的工作原理及特性2023-02-27 1575

-

AIN/AIGaN/GaN MIS异质结构C-V分析2023-02-14 4948

-

详解MOS管的特性曲线2022-08-29 50024

-

半导体器件C-V特性测试说明2022-05-31 876

-

半导体器件C-V特性测试方案2019-09-27 4132

-

能否提供ADS仿真中获得N-MOS FD-SOI晶体管的C-V曲线?2018-11-15 3193

-

基于C-V水平集模型的SAR图像灰度分布不均匀的改进2017-11-06 925

-

基于C-V模型的医学图像分割方法2012-05-25 825

-

半导体C-V测量基础(吉时利)2010-03-13 905

-

半导体电容-电压(C-V)测试的方法、技巧与注意事项2010-03-02 804

-

半导体C-V测量基础2009-08-27 5669

全部0条评论

快来发表一下你的评论吧 !