AXI4-Stream Video 协议和AXI_VDMA的IP核介绍

描述

本文主要介绍关于AXI4-Stream Video 协议和AXI_VDMA的IP核相关内容。为后文完成使用带有HDMI接口的显示器构建图像视频显示的测试工程做准备。

AXI4-Stream Video 协议

接口定义

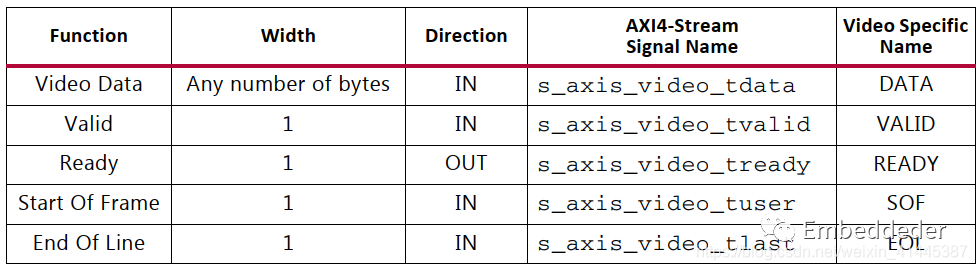

对于使用AXI4-Stream Video 协议的IP,对于接口的功能会进行拓展或者裁剪。下表列出了作为从机时,输入的接口信号名称和相关信息。

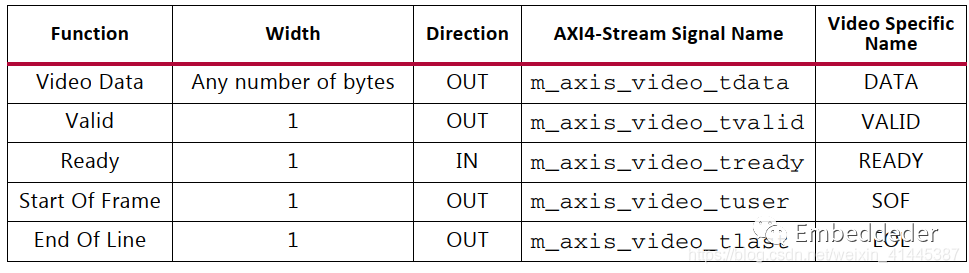

下表列出了作为主机时,输出的接口信号名称和相关信息。

这里的SOF 是用于指示起始帧的传输信号,SOF实际上是在AXI4-Stream的USER信号上进行传输的;EOL用于指示一行数据传输完成。EOL实际上是在AXI4-Stream的TLAST信号上进行传输的,用于指示一行帧数据的传输完成。在这个协议中没有行场同步的信号,所以使用SOF和EOL用于进行同步视频数据信息。TKEEP and TSTRB 这两个信号在使用AXI4-Stream视频协议的IP时不使用。当连接到需要TKEEP或TSTRB分配的IP时,可以使用默认值TKEEP=1和TSTRB = 1。TID and TDEST 在使用AXI4-Stream视频协议的IP中不使用TID和TDEST,使用默认值TID=0和TDEST=0。TUSER TUSER的第0位(TUSER[0])标记帧的开始。是唯一用于视频的AXI4-Stream信号。

AXI4-Stream Video协议时序

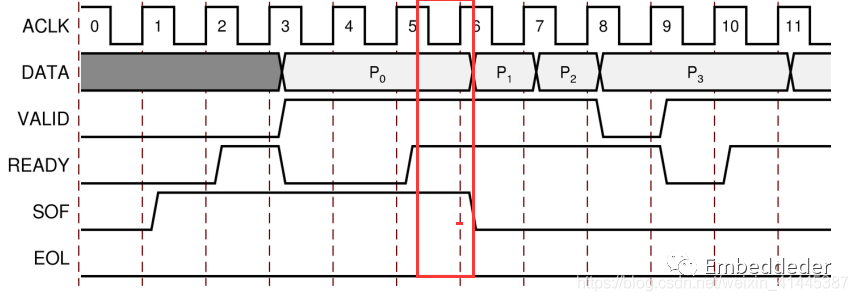

READY、VALID、ACLKEN和ARESETn信号,在ACLK上升沿时发生有效传输。在有效传输过程中,DATA只携带有效的视频数据。握手机制和AXI DMA的握手机制相同。都是通过在在ACLK上升沿时,拉高VALID、READY,进行有效的数据传输。下面给出使用握手机制信号进行一个起始帧的传输。在时序图中,在时钟上升沿,并且VALID、READY、SOF都为高电平时候表示有效数据传输。

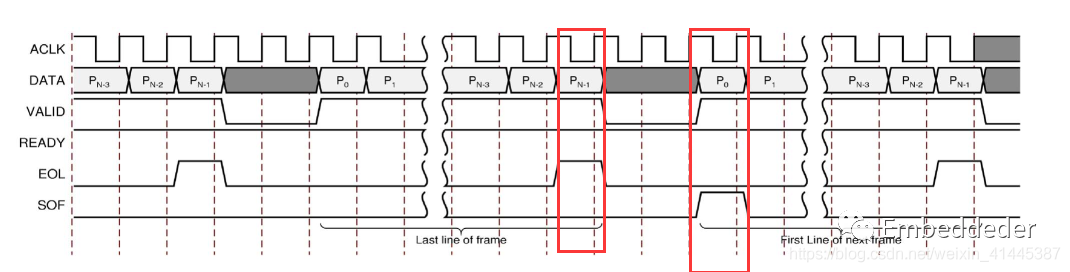

下面给出利用握手机制信号使用EOL信号进行帧传输的例子。在时序图中,在时钟上升沿,并且VALID、READY、SOF都为高电平时候表示有效数据传输表示帧数据的起始。在Pn-1也就是一行数据的最后一个进行传输时,EOL信号拉高,和LAST信号相同。当完成一帧传输的最后一个数据传输后,在下次传输时,SOF信号将会再次拉高,指示下一帧的第一个信号的传输。

AXI_VDMA IP

简介

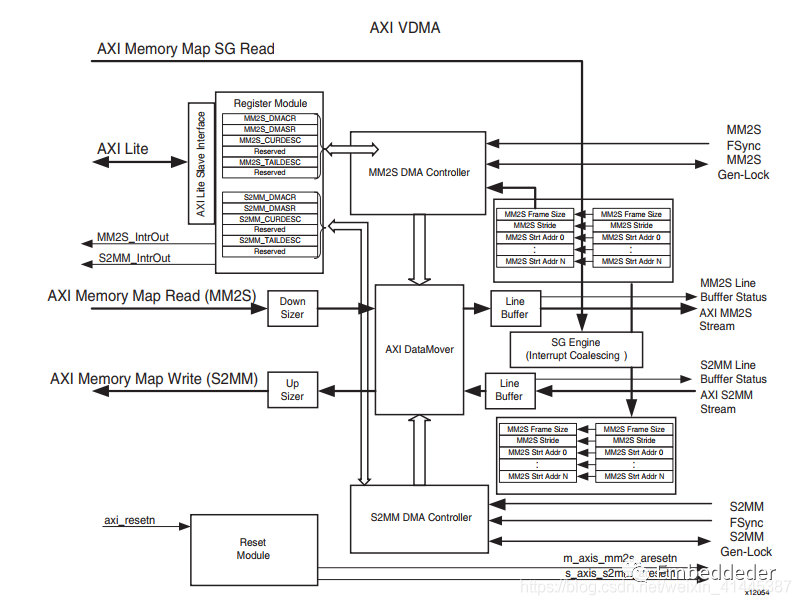

AXI VDMA IP提供了高带宽内存和内存之间的直接访问数据流视频类型的目标外设,包括支持AXI4-Stream video协议的外设。这里提到的AXI4-Stream video协议在视频IP核直接提供了一个简单、多功能、高性能、点对点的通信接口。也可以理解为AXI4-Stream 数据的一个子集。下图展示了AXI VDMA IP的框图:

AXI VDMA提供了系统内存和AXI4-Stream类型目标外设之间的高性能直接内存访问。AXI VDMA还提供分散收集(SG)功能,允许CPU将传输控制和执行转移到硬件自动化。

AXI_VDMA提供了以下的功能:

循环帧缓存区访问最多32帧缓存,并提供工具来传输视频帧的一部分或完整的视频帧。

当前帧等待能力,允许相同的视频帧数据重复传输。

独立的帧同步和独立的AXI时钟,允许每个频道在不同的帧速率和不同的像素速率上运行。为了维持两个独立功能的AXI VDMA通道之间的同步,有一个可选的Gen-Lock同步特性。Gen-Lock提供了一种将AXI VDMA从机自动同步到一个或多个AXI VDMA主机的方法,因此从机不像主机在相同的视频帧缓冲空间中操作。在这种模式下,从通道自动跳过或重复帧。您可以将任一通道配置为Gen-Lock slave或Gen-Lock master。

对于视频数据传输,AXI4-Stream端口可以配置从8位到1024位宽(8的倍数)。对于AXI4- stream端口比相关的AXI4内存映射端口窄的配置,AXI VDMA会在内存映射端升级或缩小提供全总线宽度突发的数据。它还支持异步操作模式,其中所有时钟都是异步处理的。

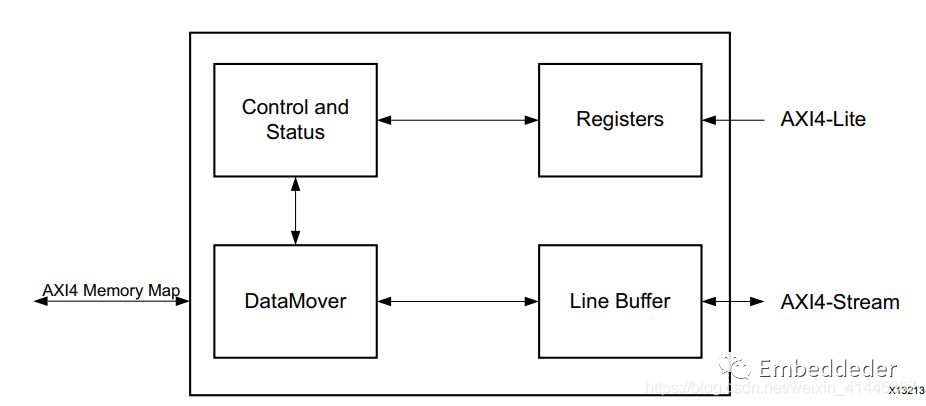

VDMA 用于将 AXI Stream 格式的数据流转换为 Memory Map 格式或将 Memory Map 格式的数据转换为 AXI Stream 数据流, 也就是说 VDMA 内核旨在提供从 AXI4 域到 AXI4-Stream 域的视频读/写传输功能,反之亦然,从而实现系统内存(主要指 DDR3) 和基于 AXI4-Stream 的目标视频 IP 之间的高速数据移动。VDMA 的框图如下图所示:

AXI4-Lite 可以对寄存器进行编程(配置),从而实现软件动态配置 VDMA 的功能。通过 AXI4-Lite 接口对寄存器进行编程后,控制/状态逻辑块会为 DataMover 生成适当的命令,以在 AXI4 主接口上启动写入和读取命令。可配置的异步 line buffer 用于在将像素数据写入 AXI4-Memory Map 接口或 AXI4-Stream 接口之前临时保存像素数据。VDMA 数据接口可以分为读、写两个通道,且写入和读取独立运行。用户可以通过写通道将 AXI-Stream类型的数据流写入系统存储器(主要指 DDR3) 。在读通道中, VDMA 使用 AXI4 主接口从系统存储器读取数据并在 AXI4-Stream 主接口上输出。可以看到, VDMA 本质上是一个数据搬运的 IP, 可以看作是为视频图像处理做特殊优化的带有帧缓冲功能的高性能 DMA, 为数据进出系统存储器提供了一种便捷的方案。

帧缓存

许多视频应用程序需要帧缓存来处理帧速率的变化或图像尺寸的变化(缩放或裁剪)。帧缓存存储器( Frame Buffer),简称帧缓存,也常被称作显存,是为显示设备(如 HDMI 显示器等)提供数据缓存的一片存储区域。一般图像输入源和图像显示的传输速率不匹配(如图像输入源传输速度较快或者图像显示端传输速度较快),这个时候需要一片存储区域来缓存输入的数据,以便显示设备读取数据,同时也方便后续对视频数据做图像处理。帧缓存的每一个存储单元对应屏幕上的一个像素,整个帧缓存对应一帧图像。比如视频输入的设备是30帧的数据,而经过视频处理后实现了60帧的视频数据显示,这时候VDMA的帧缓存功能,就可以进行动态处理帧速度的变化。

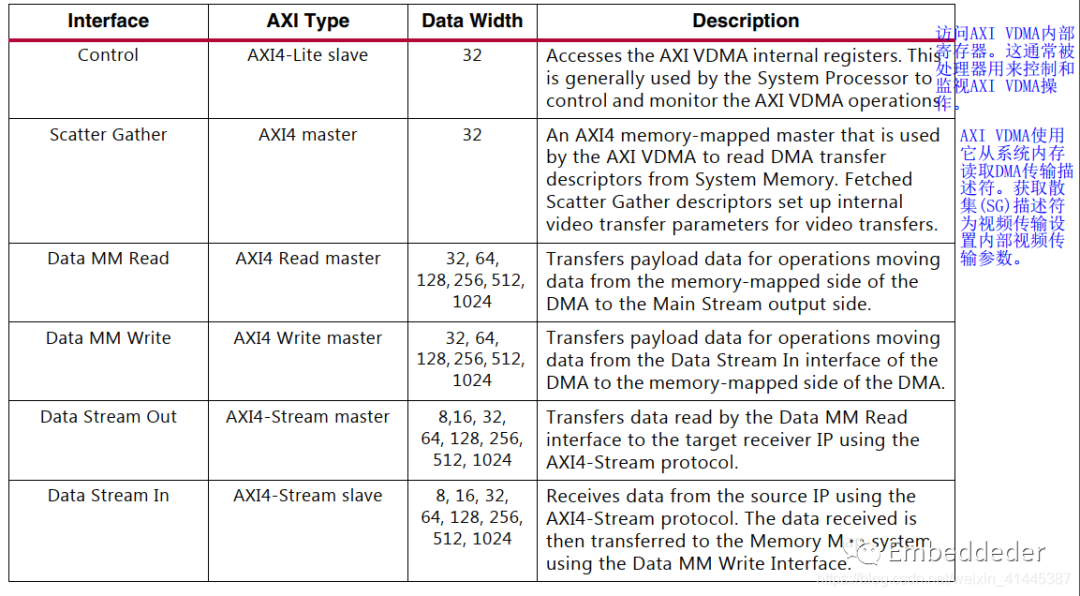

VDMA AXI4 接口

在这里插入图片描述

读写时序

读时序

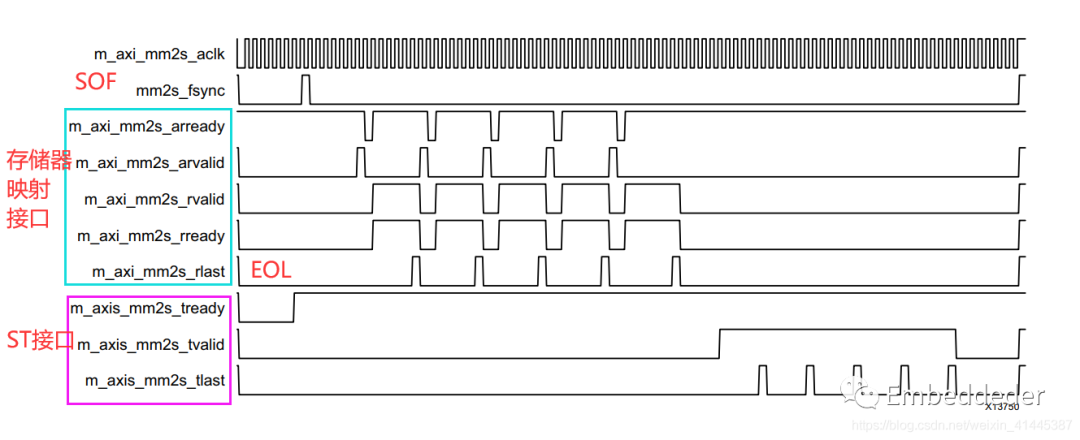

下面给出VDMA在读取数据时的时序图,并进行简单的分析,对于接口信号大致可以分为两组,一组是存储器映射接口,进行数据传输,另外一组是stream接口,将读取到的数据在line buffer里进行缓存。下图时序的大致传输过程为:

SOF拉高使能,进行帧同步。

握手信号进行握手并传输视频数据。

EOL信号拉高表示一行数据传输完成,这里LAST信号被拉高5次,也就是传输了一帧图像的五行。

传输完成的数据移动到line buffer缓存区,然后通过stream接口发送输出。

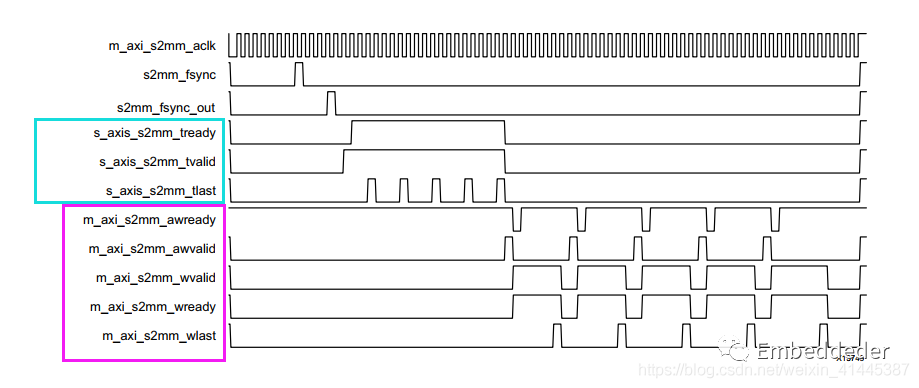

写时序

下面给出VDMA在写入数据时的时序图,并进行简单的分析,这里的流程和读取的过程刚好相反。下图时序的大致传输过程为:

SOF拉高使能,进行帧同步。

握手信号进行握手并写入视频数据。

EOL信号拉高表示一行数据传输完成,这里LAST信号被拉高5次,也就是传输了一帧图像的五行。

这里写入的数据是写完先缓存在line buffer中,然后再经过stream流数据传输到存储器映射的存储单元中。

Reference

正点原子ZYNQ开发视频教程

UG585

UG1037

PG020

原文标题:Reference

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

-

Video Frame Buffer IP初学者入门案例分析2020-11-16 6666

-

XILINX FPGA IP之AXI Traffic Generator2023-11-23 5611

-

一文详解Video In to AXI4-Stream IP核2025-04-03 3054

-

VDMA IP核简介2025-10-28 281

-

有人有经验AXI4-Stream到视频输出IP核吗?2019-03-08 8183

-

请问我对AXI4-Stream FIFO的理解不正确吗?2019-08-12 5308

-

请问AXI4-Stream到Video核心的技巧有什么?2019-11-08 3449

-

axi4-stream互连问题如何解决2020-06-18 2450

-

axi4-stream combiner问题的解决办法?2020-08-20 3463

-

AXI-stream数据传输过程2021-01-08 2904

-

Xilinx的LogiCORE IP Video In to AXI42017-02-08 920

-

自定义sobel滤波IP核,IP接口遵守AXI Stream协议2019-08-06 4782

-

AXI-Stream代码2020-11-05 4978

-

关于AXI4-Stream协议总结分享2022-06-23 3338

-

AXI4 、 AXI4-Lite 、AXI4-Stream接口2022-07-04 10918

全部0条评论

快来发表一下你的评论吧 !