XRT_Kernel与XRT_IP介绍

描述

本文作者:赛灵思工程师 Yang Chen

从2020.2开始,XRT提供了新的Native API,以区别行业标准OpenCL API的,在FPGA加速应用上,两者都是可以使用的。XRT Native API的优势是更加契合FPGA加速应用,而OpenCL的优势则是平台通用性比较好。

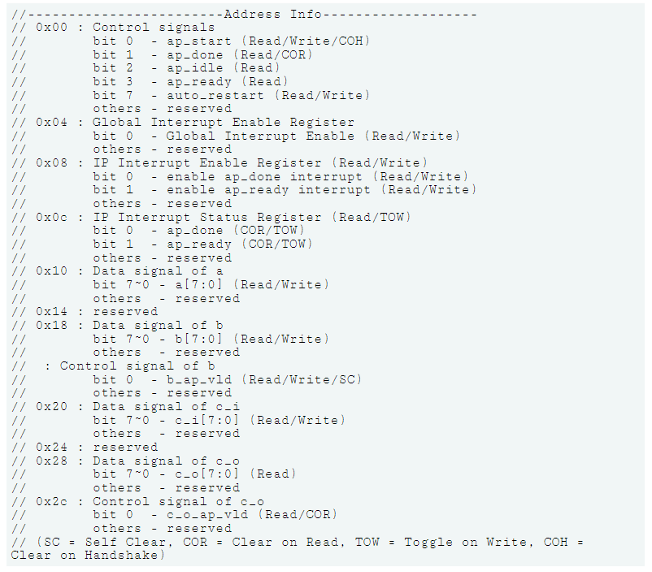

XRT Native API里面有两个API比较有意思,可能会产生混淆,一个是xrt_kernel,另一个是xrt_ip。IP这个概念,在FPGA中还是比较常用的,典型的就是IP catalog里面的IP,当然这次讲到的IP更倾向于custom IP,即用户自定义IP(以下略作IP)。无论使用Vitis_hls, V++,Package_xo中哪种生成方法,最后生成的kernel的端口类型都是固定的,另外控制端口AXI_LITE的寄存器配置也是保持固定的(当然会因参数数量不同而变化)。

截取以下网址-page 274 S_AXILITE Control Register Map作参考:

(https://www.xilinx.com/support/documentation/sw_manuals/xilinx2021_2/ug1399-vitis-hls.pdf )

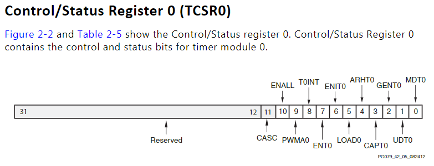

这些寄存器设置都是工具自动生成的,用户不需要进行修改。具体这些信号是如何让控制这些模块的,以后有机会可以再讲。那么如果有些需求是,我是一名RTL设计者,设计里面有Xilinx IP需要配置功能,我想用更多一点的寄存器空间作额外配置,现有的寄存器空间不够,不能满足我的要求:假设,一个IP中内嵌了一个axi_timer IP(截图取自:https://www.xilinx.com/support/documentation/ip_documentation/axi_timer/v2_0/pg079-axi-timer.pdf page 12)

那么我该如何配置它呢?

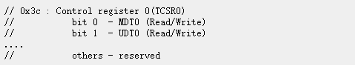

这时,之前提到xrt_ip就可以派上用场了,用户可以自己定制控制寄存器而不用受限于规定的control register map,当然端口类型还是需要按照kernel的要求来设计。沿用上述的寄存器配置,我们可以额外地添加寄存器:

所以我们可以看到,kernel应该算IP中的一个子集,只是IP的话更加的灵活些。但是由于IP控制寄存器配置的不固定,导致xrt无法自动管理IP(不知道哪个寄存器代表的含义),所以只能提供了寄存器接口让用户自己访问控制。从这方面来说,使用的便利性会降低,无论是IP的启动停止,还是寄存器配置都需要用户来控制。相对来说,xrt_kernel匹配的set_arg,run,wait等操作,它能够代替用户做一些底层操作,更加地省时省力。

原文标题:开发者分享|XRT Native API: XRT_Kernel & XRT_IP 介绍

文章出处:【微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

Xilinx运行时(XRT)发行说明2023-09-14 766

-

为Alveo卡安装Xilinx运行时(XRT)需要多长时间?2023-07-10 864

-

XRT工具之Xbmgmt的使用方法2023-01-11 3644

-

如何在IP的kernel module里设置并使用IP interrupt2022-08-02 1065

-

基于XRT83SL38EVAL视频系统的2021-09-09 581

-

基于XRT83SL3EVAL视频系统的参考设计2021-07-05 533

-

怎么在IP的kernel module里设置IP interrupt?2021-05-12 2078

-

基于XRT86L38EVAL成帧器的参考设计2021-01-13 818

-

基于XRT86L34EVAL成帧器的参考设计2021-01-12 679

-

怎么使用SPI-IN PSO3编程XRT8000时钟分频器?2019-05-15 2110

全部0条评论

快来发表一下你的评论吧 !