分享一下从PN结到IGBT的机理,掌握基础

描述

“使用IGBT时,注重实用的工程师往往在不同技术路线的IGBT芯片上看得云里雾里。这里,就分享一下从PN结到IGBT的机理,掌握基础,千变万化不离其宗,性能变化就很容易记了

PN结

PN结是半导体的基础,掺杂是半导体的灵魂,先明确知识点:

P型和N型半导体: 本征半导体掺杂三价元素,根据高中学的化学键稳定性原理,会有 “空穴”容易导电,因此,这里空穴是“多子”即多数载流子,掺杂类型为P(positive)型;同理,掺杂五价元素,电子为“多子”,掺杂类型为N(negative)型

载流子:导电介质,分为多子和少子,概念很重要,后边会引用

“空穴”带正电,电子带负电,但掺杂后的半导体本身为电中性

P+和N+表示重度掺杂;P-和N-表示轻度掺杂

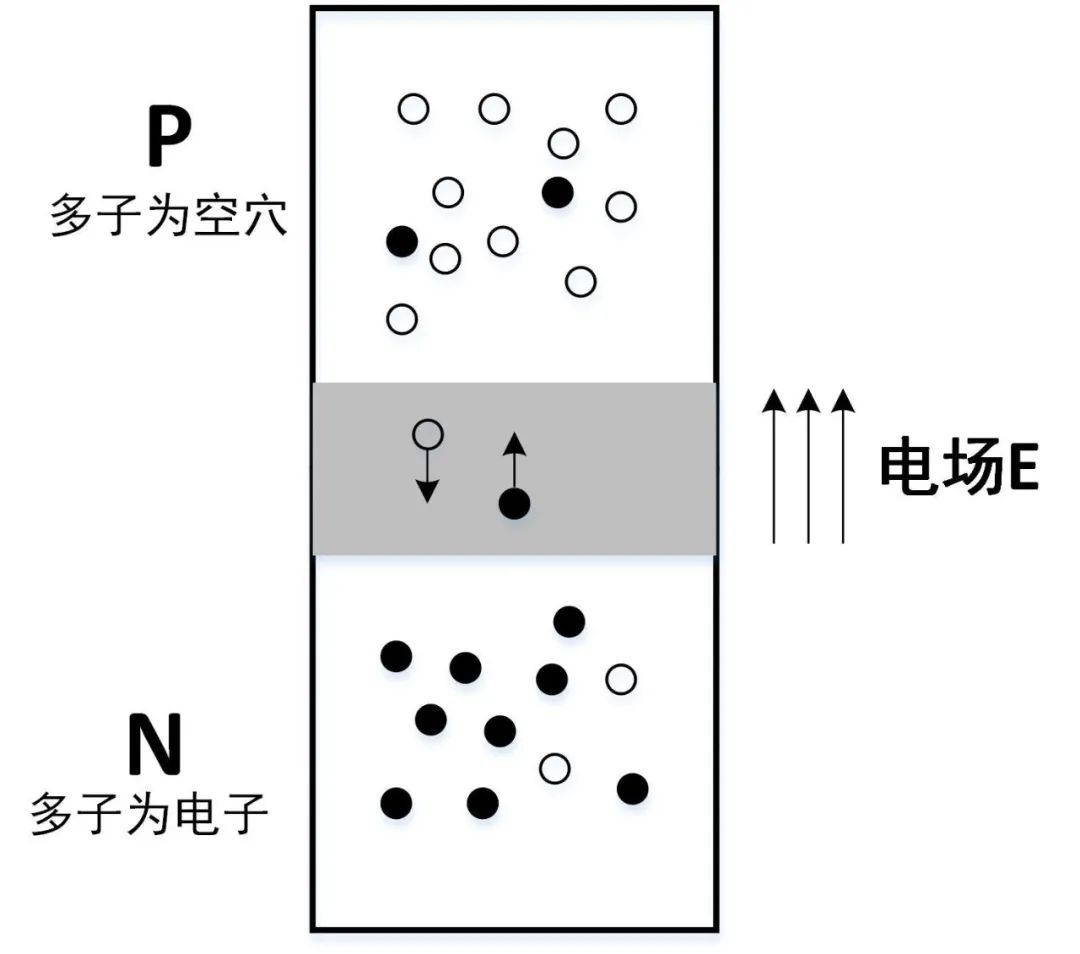

PN结原理如下图,空穴和电子的扩散形成耗尽层,耗尽层的电场方向如图所示:

二极管

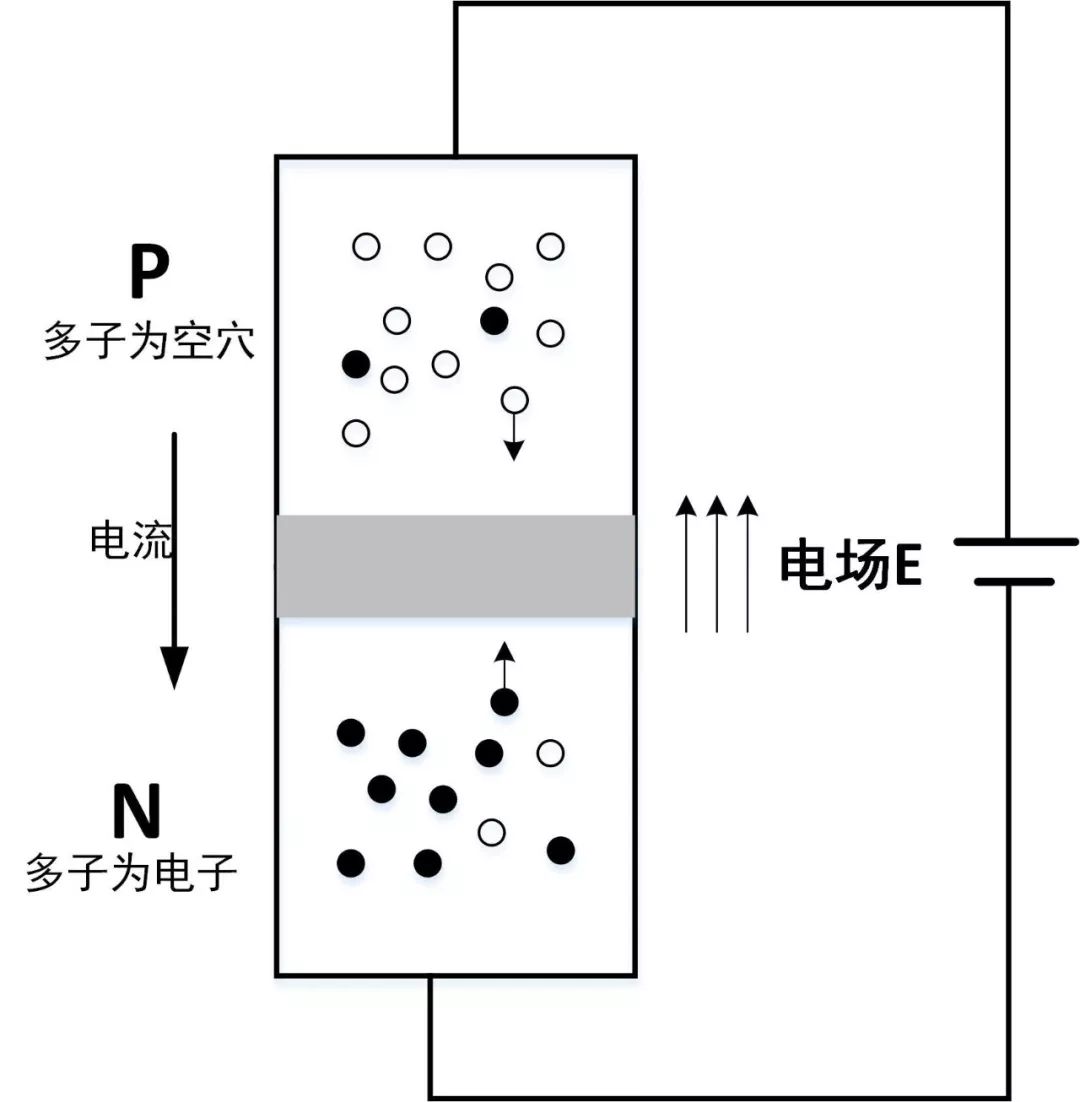

PN结正偏:PN结加正向电压,如下图

此时P区多子“空穴”在电场的作用下向N区运动,N区多子电子相反,使耗尽层变窄至消失,正向导电OK,也可以理解成外加电场克服耗尽层内电场,实现导电,该电压一般为0.7V或0.3V

二极管正向导通的原理即是如此

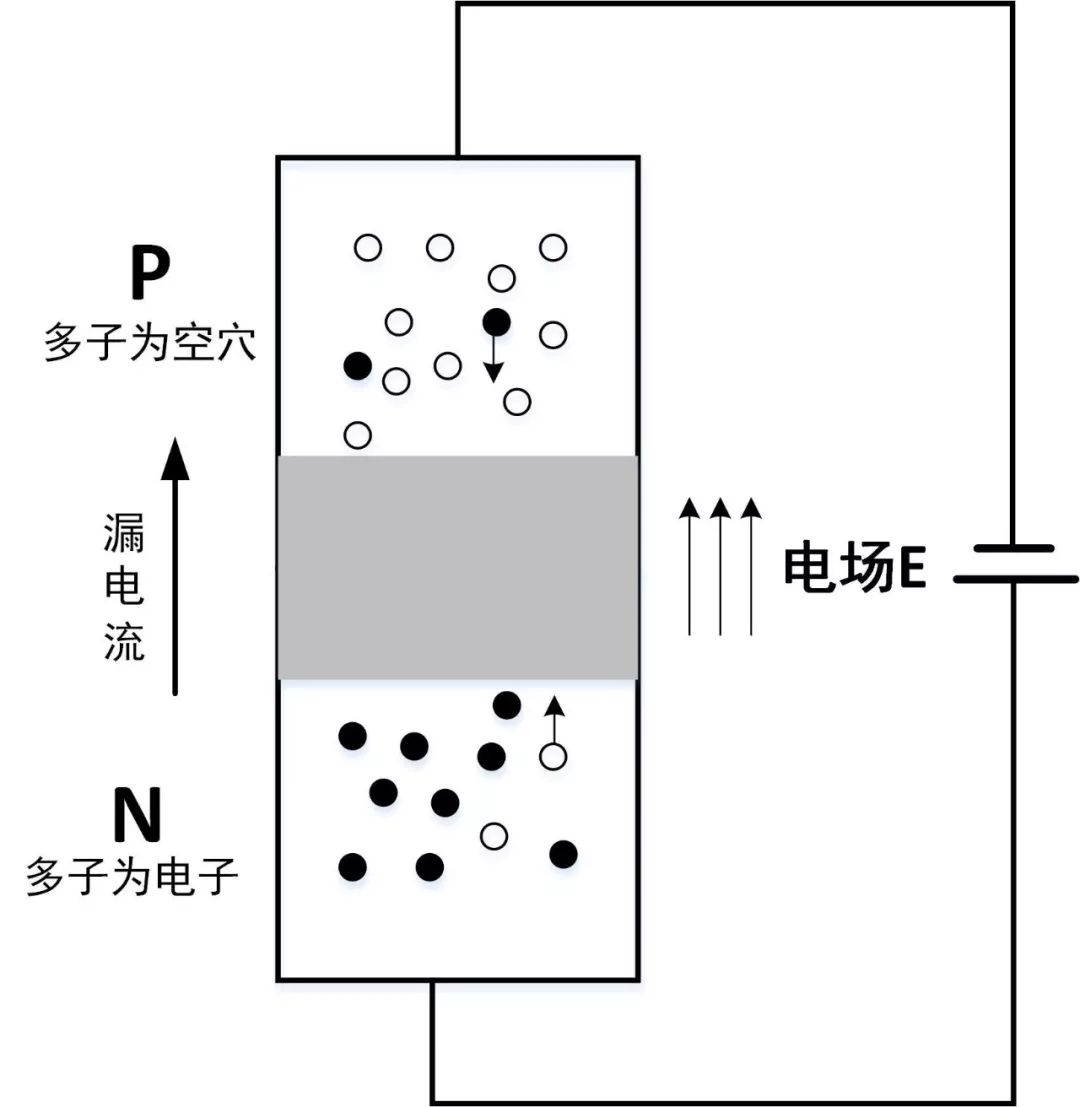

PN结反偏:PN结加反向电压,如下图

反偏时,多子在电场作用下运动使PN结加宽,电流不能通过,反向截止;

二极管反向截止的原理就是这样

但是,此时少子在内外电场的作用下移动,并且耗尽层电场方向使少子更容易通过PN结,形成漏电流。

得出重要结论,划重点:

反偏时,多数载流子截止,少数载流子很容易通过,并且比正偏时多数载流子通过PN结还要轻松。

三极管

上边说PN结反偏的时候,少数载流子可以轻易通过,形成电流,正常情况小少子的数量极少,反向电流可忽略不计。

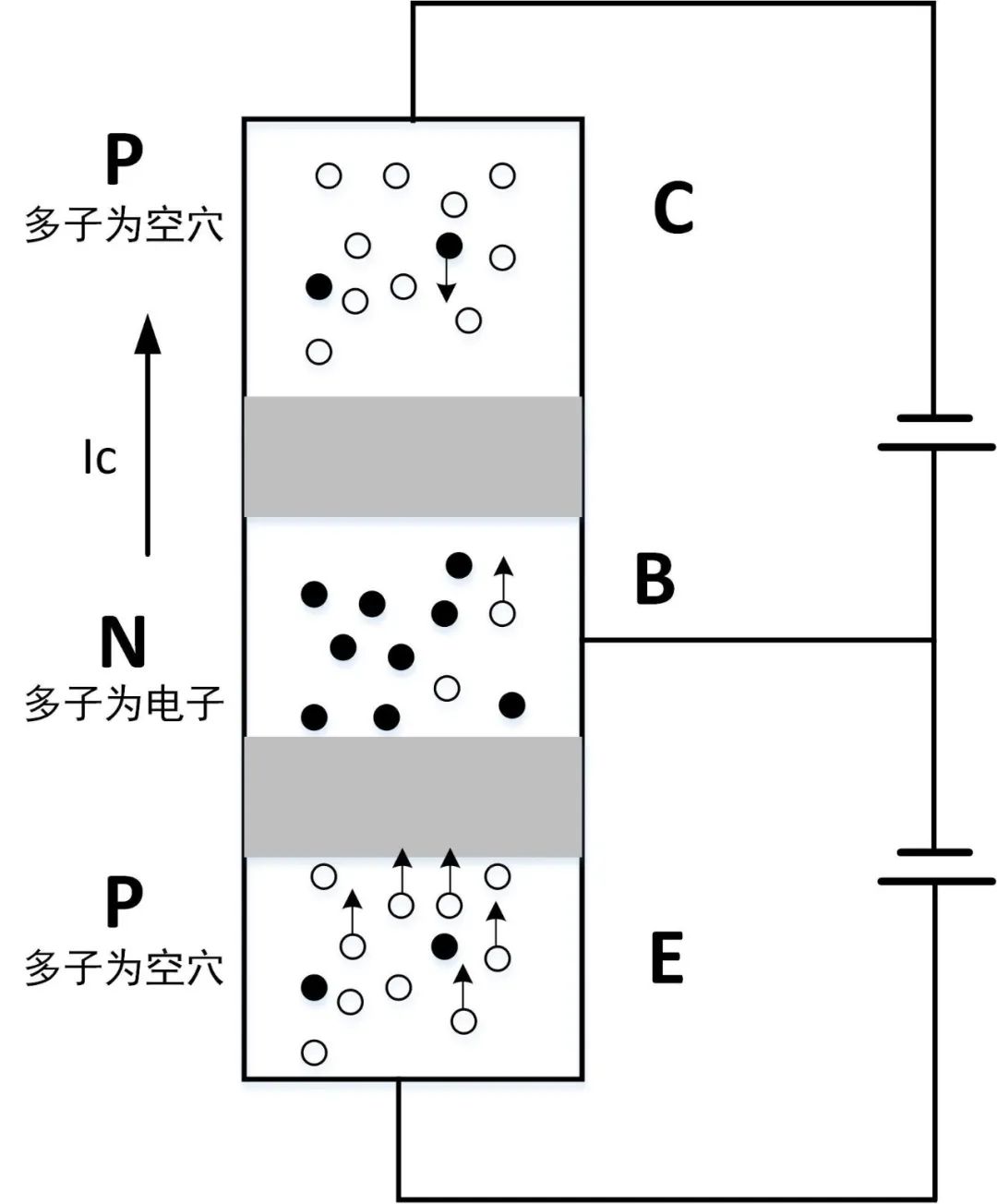

现在我们就控制这个反向电流,通过往N区注入少子的方式,怎么注入,在N区下再加一个P区,并且使新加的PN结正偏,如下:

上图中,发射结正偏,空穴大量进入基区,他们在基区身份仍然是少数载流子的身份,此时,如前所述,这些注入的少数载流子很容易通过反偏的PN结——集电结,到达集电极,形成集电极电流Ic

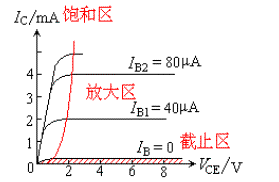

于是,我们课堂上背的三极管放大导通条件是<发射结正偏,集电结反偏>就非常容易理解了,上一张三极管的特性曲线

这里涉及了饱和区的问题

三极管工作在饱和区时Vce很小,有人说饱和区条件是发射结正偏,集电结也正偏,这很容易让人误解;发射结正偏导通没问题,但集电结并没有达到正偏导通,若集电结正偏导通,就跟两个二极管放一起没区别;集电结的正偏电压阻碍基区少子向集电极漂移,正偏越厉害,少子向集电极运动越困难,即Ic越小,因此饱和状态下的Ic是小于放大状态下的βIb的,此时,管子呈现出很小的结电阻,即所谓的饱和导通

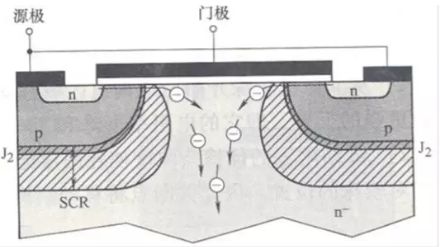

MOSFET

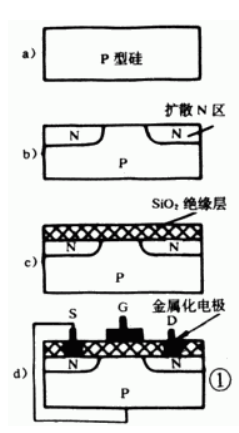

MOS管结构原理:以N-MOS为例,a:P型半导体做衬底;b:上边扩散两个N型区,c:覆盖SiO2绝缘层;在N区上腐蚀两个孔,然后金属化的方法在绝缘层和两个孔内做成三个电极:G(栅极)、D(漏极)、S(源极)

工作原理:一般衬底和源极短接在一起,Vds加正电压,Vgs=0时,PN结反偏,没有电流,Vgs加正电压,P衬底上方感应出负电荷, 与P衬底的多子(空穴)极性相反,被称为反型层,并把漏源极N型区连接起来形成导电沟道,当Vgs比较小时,负电荷与空穴中和,仍无法导电,当Vgs超过导通阈值后,感应的负电荷把N型区连接起来形成N沟道,开始导电。Vgs继续增大,沟道扩大电阻降低,从而电流增大

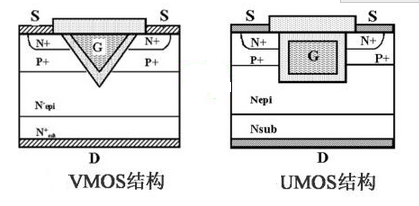

为改善器件性能,出现了VMOS、UMOS等多种结构,基本原理都一样。

功率MOS:

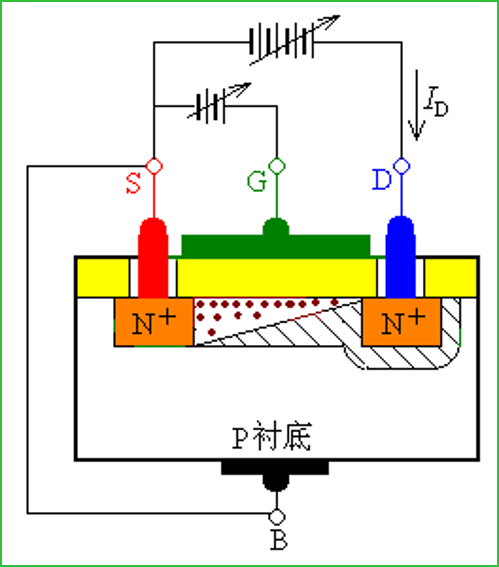

下图功率MOS结构上可以称VDMOS(vertical Double diffusion MOS垂直双扩散MOS),工作原理如上所述,仔细看对分析IGBT的结构有帮助哦!

插播:

不同MOS结构名称:

LDMOS:lateral double diffused MOSFET 水平双扩散MOS

VDMOS:vertical double diffusion MOSFET垂直双扩散MOS

VDMOS与LDMOS的不同是漏极在背面,垂直结构

为克服平面栅的缺点,后边发展了VMOS和UMOS(此思路同样适用于IGBT)

IGBT

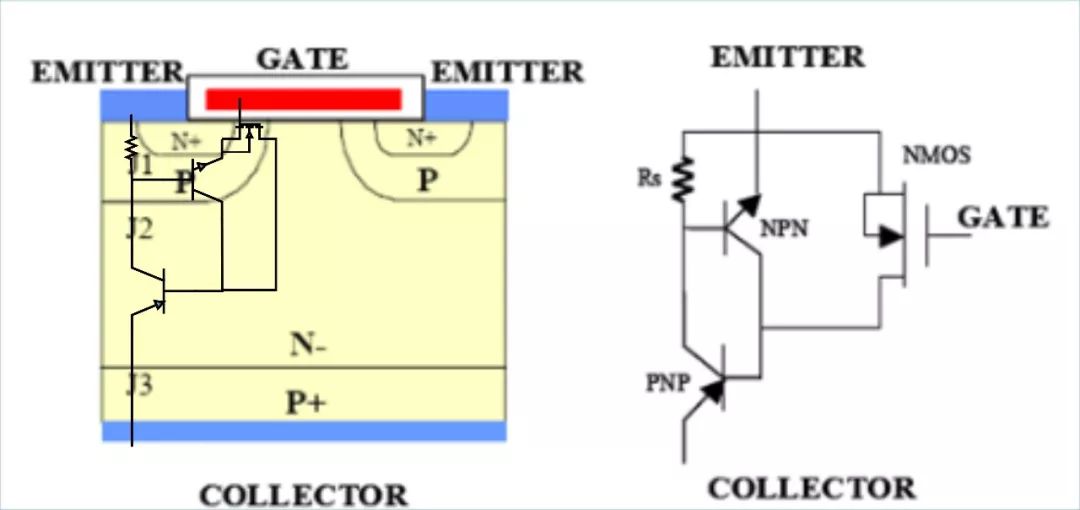

主角登场,以前说过,IGBT是MOS和BJT的复合器件,到底是怎么复合的,往下看

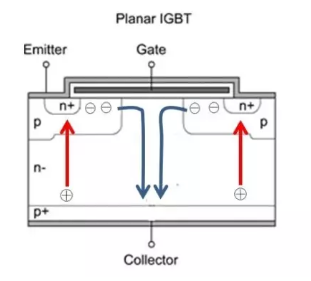

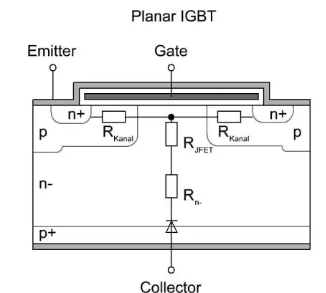

从结构上看,IGBT与功率MOS的结构非常类似,在背面增加P+注入层(injection layer)

与功率MOS相比

功率MOS:单一载流子“多子”导电

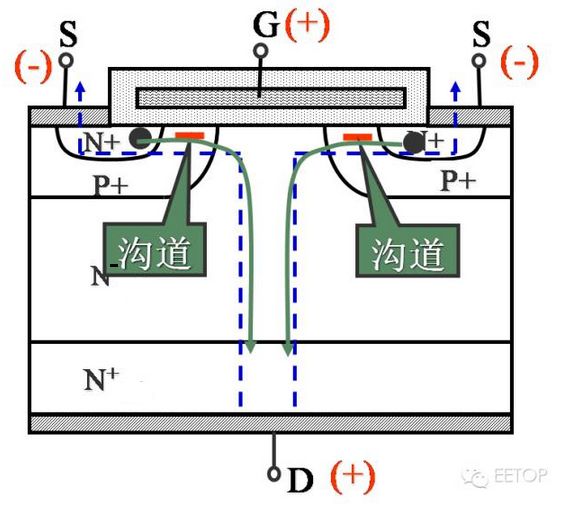

IGBT:增加P+注入层,向漂移区注入空穴,结构上增加P+/N-的PN结,并且正偏,也就是增加了类似BJT结构的三极管,于是就有两种载流子参与导电,大大增加了效率。

得出IGBT的导电路径:

由于上图P阱与N-漂移区的PN结成反偏状态,于是产生了JFET效应,如下图

于是,在上述IGBT结构中,电子流通方向的电阻可用下图表示,结合上边描述,一目了然

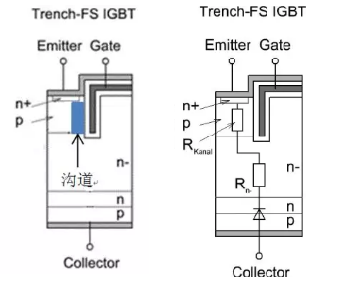

为了减小上述电阻,并且提高栅极面积利用率,沟槽栅IGBT变成主流,作用效果如下图

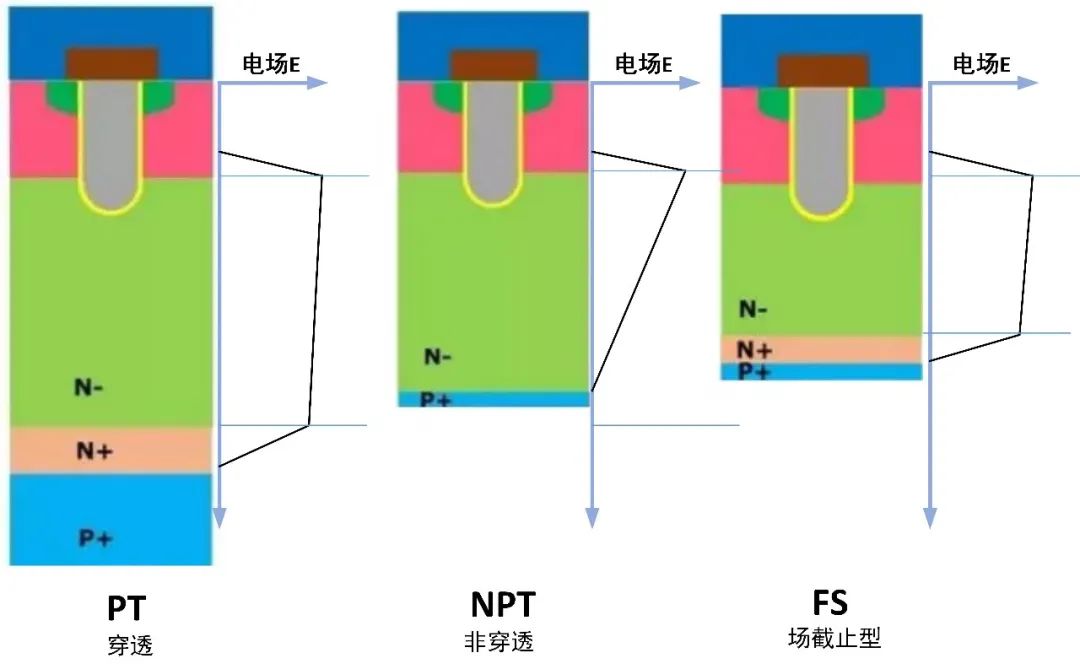

此外,为了提升IGBT耐压,减小拖尾电流,在N –漂移区、背面工艺(减薄和注入)上下了不少功夫:

N-区下的功夫包含以下几种:

PT:以高浓度的P+直拉单晶硅为起始材料,先生长一层掺杂浓度较高的N型缓冲层(N+buffer层),然后再继续淀积轻掺杂的N-型外延层作为IGBT的漂移区,之后再在N-型外延层的表面形成P-base、N+ source作为元胞,最后根据需要减薄P型衬底

NPT:采用轻掺杂N- 区熔单晶硅作为起始材料,先在硅面的正面制作元胞并用钝化层保护好,之后再将硅片减薄到合适厚度。最后在减薄的硅片背面注入硼,形成P+ collector

FS:以轻掺杂N- 区熔单晶硅作为起始材料,先在硅面的正面制作元胞并用钝化层保护好,在硅片减薄之后,首先在硅片的背面注入磷,形成N+ 截止层, 最后注入硼,形成P+ collector

从上边看,FS和PT结构相似,但工艺流程不同,表现形式上性能差距较大

有了以上基础知识后,再看IGBT芯片的发展史和带来的性能变化,就能比较容易理解了,究竟结构变化怎么带来性能变化,本篇文章不在展开,有兴趣可参考文末链接

审核编辑 :李倩

-

IGBT的终端耐压结构—平面结和柱面结的耐压差异(1)2023-12-01 4675

-

说说IGBT中PN结的导通状态2023-11-28 2239

-

PN结的雪崩击穿和齐纳击穿在温度升高时击穿电压变化方向相反?2023-09-21 6051

-

简述pn结的三种击穿机理2023-09-13 8444

-

PN结是如何形成的?什么是pn结二极管?2023-02-08 4158

-

pn结的基本特性是什么2018-09-06 108417

-

PN结2017-07-28 3050

-

PN结 耗尽层2017-04-13 8189

-

pin结与pn结的特性比较2013-05-20 33053

-

PN结,PN结是什么意思?2010-02-26 33076

-

pn结的特性,PN结的击穿特性,PN结的电容特性2008-09-10 14448

-

PN结的形成及特性ppt2008-07-14 1307

全部0条评论

快来发表一下你的评论吧 !