IEEE 1149.7扩展和改进JTAG

描述

IEEE 1149.1 标准于 1990 年被采用。基于联合测试行动小组 (JTAG) 的工作,它提供了从一个 IC 焊盘到另一个 IC 焊盘的引脚视图,以帮助测试工程师定位和发现有故障的 PC 板。1994 年增加了边界扫描描述语言的描述。

随着芯片功能的增加和设计从 PC 板转向多芯片模块和堆叠芯片封装,复杂性出现了。这些困难包括处理片上系统 (SoC) 设备的引脚数要求和多个测试访问端口 (TAP) 控制器、测试多芯片模块和堆叠芯片配置、提高调试性能以及改进测试和调试逻辑断电低功率条件。

移动行业处理器接口联盟和 NEXUS 5001 论坛等组织接受了挑战,以解决其行业特有的问题。他们的工作为 IEEE 1149.7 标准奠定了基础,该标准有望在明年初获得批准。

增加测试系统功能

新的 IEEE 1149.7 标准并没有取代 IEEE 1149.1,而是通过减少使用的引脚数量来扩展其功能。这提供了有利于堆叠裸片和多芯片模块配置的新扫描拓扑,并提供高级功能以帮助进行软件调试。

IEEE 1149.7 目标

与现有的 IEEE 1149.1 系统兼容

使用更少的引脚操作

使用相同的引脚提供后台仪表功能

提供 TAP 电源管理机制

用于调试半导体错误/缺陷的保留网关

提高选定调试用例的性能

保留对半导体 IP、软件 IP 以及现有调试和测试工具的投资

为其他调试引脚协议提供框架以访问引脚

IEEE 1149.7 标准具有两组功能:T0 到 T3 类,扩展 IEEE 1149.1 并启用新操作,以及 T4 和 T5 类,专注于高级双引脚操作。

T0 级

T0 类通过设置 IEEE 1149.7 设备以使其与 IEEE 1149.1 兼容,从而确保符合行业测试基础设施。这些技术包括使用 N 位 IR、1 位 DR 用于旁路指令、强制性 IDCODE(32 位路径)和行为如 IEEE 1149.1 规范中指定的强制性指令。启动测试逻辑复位后,所有多 TAP 设备必须符合强制性 IEEE 1149.1 指令行为,并对旁路指令执行 1 位 DR 扫描。

T1 级

T1 类实例化了一个对 IEEE 1149.1 设备透明的 IEEE 1149.7 标准的控制系统,为在 T1 到 T5 类中实现的高级功能提供了基础,而无需更改 IEEE 1149.1 状态机。除了创建控制系统外,该课程还解决了具有四种断电模式的功率敏感设备的需求。

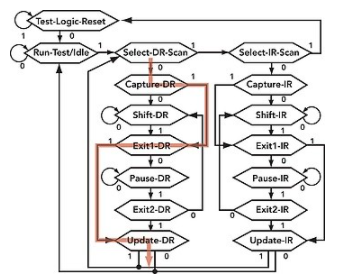

关键创新是 IEEE 1149.1 兼容的 TAP 状态序列和移位状态监视的组合,它创建了一个 IEEE 1149.7 控制系统,该系统利用旁路或 IDCODE 指令以及一系列称为零位 DR 扫描的 IEEE 1149.1 兼容序列( ZBS),如图 1 所示。

图1

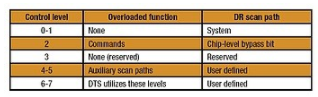

从零开始,ZBS 计数随着 ZBS 的每次连续出现而递增,而不会遇到 Shift-DR TAP 控制器 (TAPC) 状态。当包含 Shift-DR 的 DR 扫描发生并且 ZBS 计数大于零时,ZBS 计数被锁定,激活相应的控制级别(如表 1 所示)。

表格1

命令通常是 10 位值,由两个连续的 DR 扫描组成,同时控制器锁定在控制级别 2。命令部分 1 (CP1) 提供 5 位操作码,命令部分 2 (CP2) 提供立即操作数,这是命令的低 5 位。该命令指定的功能在 CP2 完成时执行。

可以通过在 CP1 和 CP2 之后附加第三个 DR 扫描(控制寄存器或 CR 扫描)并传输数据值来创建三部分命令。这三个三部分命令中的每一个都有一个特殊的用途。

T2 级

为了让参与测试高芯片数应用的工程师获得更高的性能,T2 类提供了一种缩短扫描链的芯片级旁路机制和另一种提供热连接能力的机制。T2 类添加了三种扫描格式来实现这些新功能:

JSCAN0:提供符合 IEEE 1149.1 的操作。

JSCAN1:提供热连接和断开保护。上电时,旁路可以是默认设置(JSCAN1 格式)。这可以保护 TAP 免受虚假信号的影响,并防止热连接期间的内核损坏。

JSCAN2:实施旁路以提高串联设备的性能。该机制还起到防火墙的作用,只有在启动预定序列后才能访问芯片 TAP。这种安全措施确保一旦运行的通电目标具有稳定的电气连接,只有调试测试控制器才能访问系统。

T3 级

虽然包括使用星形拓扑进行边界扫描测试的规定,但 IEEE 1149.1 并未提供足够的细节来使这种测试模式可行。IEEE 1149.7 中包含了一种新的扫描格式“Äì JSCAN3”,以纠正这一遗漏。用于指定扫描格式的只写寄存器和星型配置的设备地址分配也已添加到新标准中。

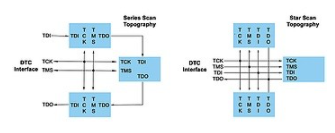

IEEE 1149.7 支持串联和星型拓扑,后者更适合测试堆叠芯片配置。由于调试连接的位置是一致的,因此星型拓扑对于堆叠管芯配置是可取的。图 2a 显示了串联扫描拓扑,图 2b 显示了 Star-4 或 Wide Star 配置。

图 2

IEEE 1149.7 通过在一组选定的支持 IEEE 1149.7 的 TAP 控制器中使用 Capture-xR 和 Update-zR TAPC 状态使所有操作看起来是系列扫描,从而保持与 IEEE 1149.1 标准的兼容性。要在这种模式下运行,必须为星型配置的芯片分配控制器标识 (CID) 编号。使用迭代仲裁系统分配 CID,并使用控制级别 2 执行操作。

T4 级

为了解决 SoC 器件中引脚数量不断增加的问题,T4 类增加了扫描格式以支持使用两个引脚而不是四个引脚的事务,从而减少了芯片封装所需的总引脚数。这也有助于堆叠裸片配置,因为非常希望在堆叠裸片时具有尽可能少的连接器数量。

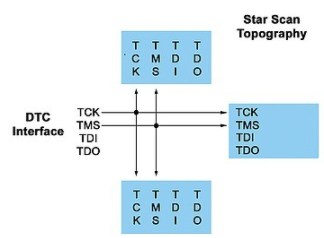

双引脚操作的关键是消除原始数据线并通过测试模式选择 (TMS) 线发送双向串行数据,该线更名为 TMS 计数器 (TMSC)。为实现此功能,使用了 T3 类的无缝星形配置,这次没有测试数据输入 (TDI) 和测试数据输出 (TDO)。这是图 3 中所示的 Star-2 配置。

图 3

除了减少引脚数之外,T4 类还定义了优化的下载特定扫描模式,其中只下载有用的信息。为了提高引脚操作性能,时钟频率也可以加倍。这些功能与优化的事务相结合不会导致性能损失,而是在某些情况下提高了性能。

T5 级

T5 类功能主要有利于利用 JTAG 进行调试的软件设计人员。此类使测试端口能够同时执行调试和仪表操作(数据在空闲时间传输),这减少了专用于仪表的引脚数量,并使自定义协议能够使用引脚,这是许多供应商在非标准中提供的功能方法。T5 类标准化了访问引脚的过程。

审核编辑:郭婷

-

可以将扩展基座用作JTAG探针吗?2018-11-05 1272

-

使用jtag接口通过网口烧写程序2007-06-05 2126

-

JTAG功能及系统设计2011-03-30 1748

-

IEEE1149.1标准JTAG接口与ISP接口,ISP interface2018-09-20 3159

-

JTAG接口定义2019-03-27 33445

-

ARM的JTAG接口基础知识2020-07-20 6885

-

ARM的JTAG调试结构2020-08-27 3974

-

一文详解JTAG2020-11-01 9832

-

JTAG简介 JTAG和SWD之间的区别2021-07-23 71861

-

什么是JTAG?用途是什么2022-10-17 11327

-

IEEE 1149.1 JTAG测试访问端口复位要求应用说明2023-07-26 798

-

SCANSTA112 7端口多点IEEE 1149.1(JTAG)多路复用器数据表2024-06-22 421

-

JTAG的基础知识2024-11-15 3162

-

深入解析 SCANSTA111:增强型扫描桥多分支可寻址 IEEE 1149.1(JTAG)端口芯片2025-12-31 506

-

深入了解SCANSTA112:7端口多分支IEEE 1149.1(JTAG)多路复用器2026-04-15 136

全部0条评论

快来发表一下你的评论吧 !