仿真和模拟用于IC验证的方法

描述

仿真技术已经存在了很长时间——据我统计,超过了四十年——行业观察家比以往任何时候都更加相信它是 IC 验证策略中的关键要素,尽管它正在重生。问题是,这个新的仿真时代是什么?为什么硬件仿真多年来一直处于 IC 设计生态系统的边缘,客户群很少,现在成为片上系统的主流设计工具( SoC)验证?答案可以在更大、更复杂的芯片的出现中找到,这些芯片通常包含多个处理器内核并超过 1 亿个门。

简而言之,一种寄存器传输级 (RTL) 模拟器,一种首选验证工具正在受到挑战,因为设计容量超过了 1 亿个门。由于处理器的扩展路线图,更大的门数是可能的。毕竟,多线程只能做这么多。其次,即使是在 PC 群上并行运行的硬件描述语言(HDL) 软件模拟器也无法创建可行的选择,因为被测设计 (DUT) 环境本质上是连续的。

另一方面,硬件仿真曾经是处理器和图形芯片等大型 IC 设计的主要部分,现在正成为一种流行的验证工具,正是因为它在全芯片验证方面比 HDL 模拟器运行得更快。硬件仿真工具可以对大型 SoC 设计进行 10 倍以上的验证,有时比软件仿真快 10 倍以上。

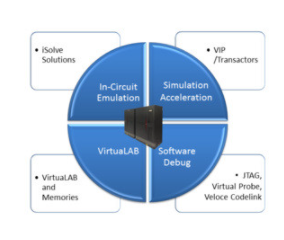

1. Mentor Graphics 的 Veloce2 仿真器平台支持的密钥验证模式视图。

在过去十年左右的时间里,硬件仿真一直在稳步发展,因为拥有成本正在下降,而仿真工具变得更易于安装和操作。并且随着仿真器 ROI 和 SoC 设计要求的变化,越来越多的 IC 设计人员倾向于使用仿真工具来调试硬件和测试软硬件集成。此外,仿真工具变得更加通用,从将物理设备连接到仿真器的在线仿真 (ICE) 到更具创新性的协同仿真解决方案,例如Mentor Graphics 的 VirtuaLab,它可以在当今日益增长的功能中虚拟化接口SoC 设计。

软件仿真或硬件仿真

模拟器尝试对 SoC 或系统级设计的行为进行建模,而模拟器则创建设计的实际实现。在这里,重要的是要注意软件模拟器和硬件模拟器都用于设计验证——这一阶段也称为被测设计或 DUT——在此阶段,编译器将设计模型转换为存储在内存中的数据结构。

然而,在仿真的情况下,软件算法使用设计语言处理表示设计模型的数据,而仿真器使用处理器阵列启用的计算引擎处理数据结构。尽管硬件仿真的市场规模已超过 3 亿美元,但这并不意味着它将成为 HDL 仿真工具的终点。

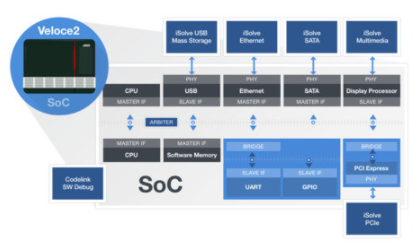

2. Veloce2仿真器同时支持传统的ICE和基于事务的验证,运行多协议接口的SoC验证。

基于 HDL 的软件仿真很可能仍然是首选的验证引擎,尤其是在验证过程的早期阶段(例如,在 IP 和子系统级别),因为它代表了一种经济、易于使用且快速上手的方法- 设置 EDA 工具。另一方面,仿真将在更大的 SoC 设计中获得牵引力,这些设计包含数百万个验证周期并且很难找到硬件错误。换言之,在可预见的未来,SoC 和系统级设计验证的两个 EDA 工具市场将共存。

审核编辑:郭婷

-

<猎头职位>深圳资深模拟IC设计工程师2015-07-08 3477

-

【招聘】职位包括数字IC设计/验证/后端物理设计、模拟IC设计/版图工程师2017-03-03 4114

-

求一种端到端的定制IC模拟与验证解决方案2021-06-22 1898

-

验证方法简介2022-02-13 5779

-

Python硬件验证——摘要2022-11-03 29591

-

用于低压系统的模拟IC2010-04-25 2138

-

硬件仿真对网络设计有何影响?2021-05-02 2160

-

仿真和模拟用于IC验证的重要工具2022-06-19 2623

-

软件仿真、硬件仿真、原型验证是如何工作的?2023-06-11 2460

-

基于场景的智能网联汽车模拟仿真测试评估方法与实践2023-07-20 6295

-

ic验证是做什么的 ic验证用什么语言2023-07-24 6545

-

ic验证是封装与测试么?2023-08-24 1945

-

芯片设计中逻辑仿真和数字验证介绍2023-09-14 3142

-

IC设计为什么需要仿真模拟?仿真模拟的重要性有哪些?2023-12-19 3929

-

数字电路设计有哪些仿真验证流程2024-01-02 3929

全部0条评论

快来发表一下你的评论吧 !