DDR4/LPDDR4硬核控制器I/O plannin的设计和实现

描述

本文作者:赛灵思工程师 Kathy Ren

在Versal新一代ACAP器件上,除了延续之前Ultrascale/Ultrascale+系列器件上已有的DDR4 IP之外,还配置了最新的DDR4/LPDDR4 硬核控制器 (NOC IP)。它的性能更高,并且不额外占用其他的可编程逻辑资源 (PL)。使用它的时候,在硬件设计方面和设计流程上,和之前的软核控制器(DDR4 IP)也有着很大的不同。今天我们来介绍一下I/O planning方面的设计考虑和实现流程。

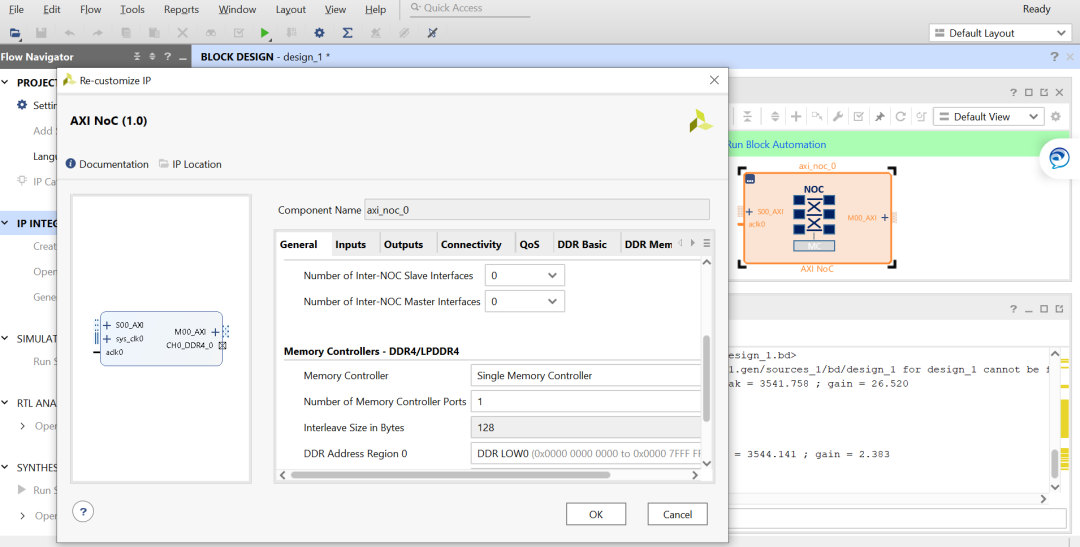

在原理图设计之前,需要先新建一个测试小工程,在block design中添加NOC IP。

在IP wizard中,根据 memory 容量,位宽,带宽等要求完成相关配置。

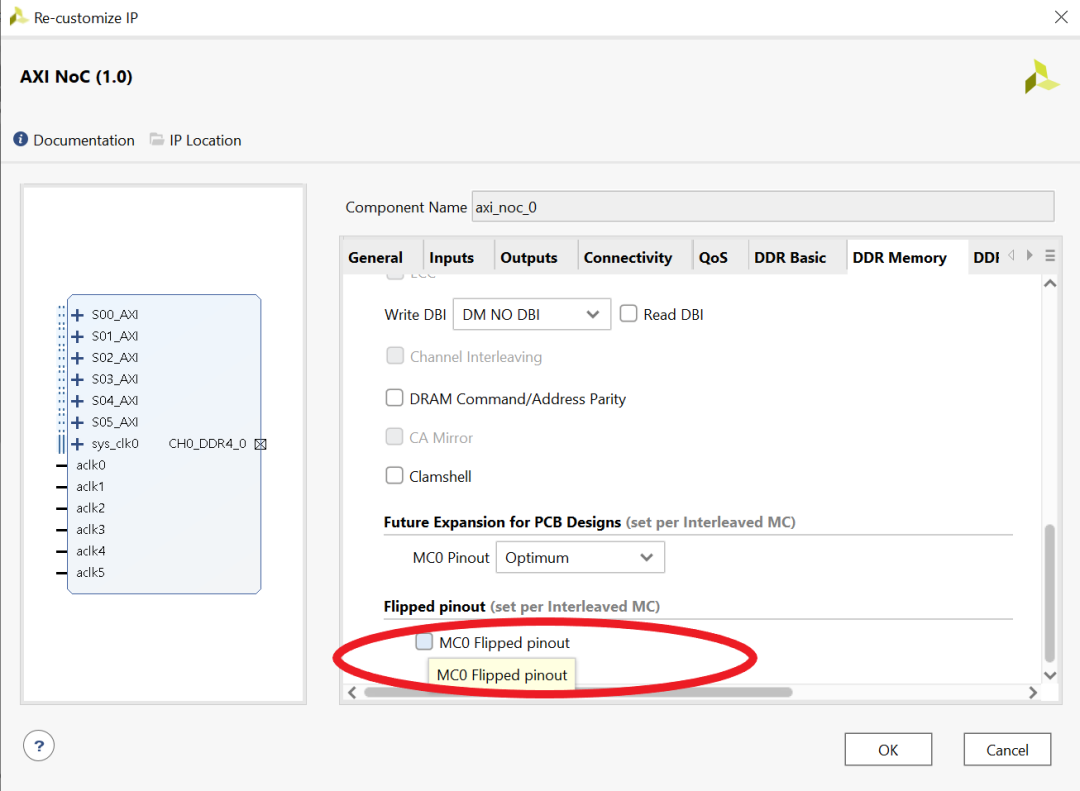

总体上来讲,DDR4/LPDDR4的管脚有2种分配模式:Flipped和Non-flipped,模式的选择可以通过使能或者关闭 NOC IP 中 “Flipped pinout”的选项来实现。

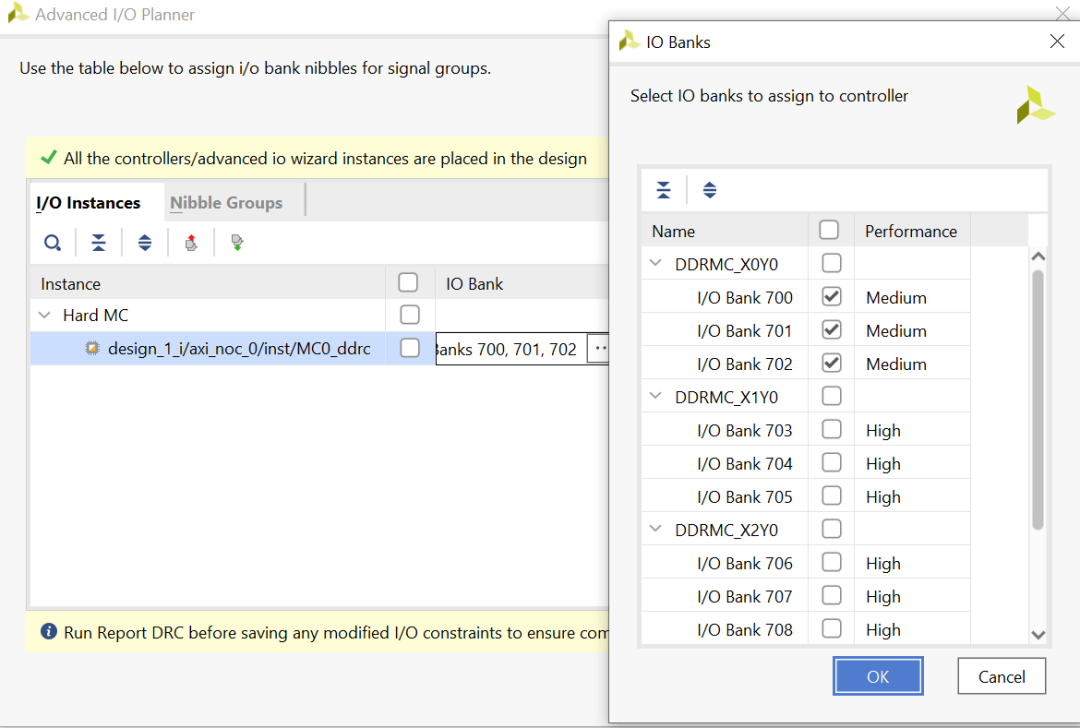

Versal 器件上每个NOC IP对应3个IO bank的管脚,它们都位于同一个triplet之中。一个NOC IP对应的所有DDR4/LPDDR4接口管脚都必须放置在这3个IO bank之中。在对 block design进行综合之后,打开synthesized design,在I/O ports窗口中点击 “Open advanced I/O planner” ,按照bank或者nibble为单位指定所有管脚的位置。

在此之后,地址、控制和时钟管脚的位置就被固定了下来。数据管脚在Byte以内和Byte之间可以进行微调,具体的调整规则可以参考pg313中Pinout Rules相关章节。

PG313:

https://docs.xilinx.com/r/en-US/pg313-network-on-chip

审核编辑:汤梓红

-

LPDDR4 DRAM 的 iMX8MP 的 DDR PHY 使用的 I/O 标准是什么?2026-04-03 186

-

LPDDR4、LPDDR3与LPDDR4X的区别是什么?2021-06-18 4304

-

浅析DDR,DDR2,DDR3,DDR4,LPDDR区别2021-09-14 2080

-

MT53E256M32替换LPDDR4,是否需要重新运行DDR工具以生成要在LPDDR4控制器中编程的新bin文件?2023-04-19 789

-

i.mx8m加支持lpddr4和lpddr4x吗?2023-04-21 734

-

i.MX 8M Nano UltraLite Quad LPDDR4校准失败的原因?2023-04-26 1112

-

lpddr4频率无法修改怎么解决?2023-06-02 1143

-

DDR4,什么是DDR42010-03-24 4254

-

使用用户为 LPDDR4 和 x8 或 x16 DDR4 组件接口指定的 DQS 字节交换生成管脚分配时,其中可能包含错误且需更改2022-08-09 3202

-

DDR4 SDRAM手册2022-12-05 1241

-

Versal ACAP DDRMC-DDR4、LPDDR4和LPDDR4X外部参考时钟设计指南2023-07-10 2737

-

LPDDR4是什么意思?LPDDR4X内存是什么意思?2023-08-21 13065

-

DDR4、LPDDR4和LPDDR4x的区别2023-09-19 25098

-

全套DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 电源解决方案同步降压控制器数据表2024-04-09 798

-

DDR4 SDRAM控制器的主要特点2024-09-04 2457

全部0条评论

快来发表一下你的评论吧 !