桥式结构中低边SiC MOSFET关断时的行为

描述

通过驱动器源极引脚改善开关损耗

本文的关键要点

1具有驱动器源极引脚的TO-247-4L和TO-263-7L封装SiC MOSFET,与不具有驱动器源极引脚的TO-247N封装产品相比,SiC MOSFET的栅-源电压的行为不同。

2要想正确实施SiC MOSFET的栅-源电压的浪涌对策,需要逐一了解电压的行为。

具有驱动器源极引脚的SiC MOSFET,与不具有驱动器源极引脚的SiC MOSFET产品相比,在桥式结构情况下的栅-源电压的行为不同。在上一篇文章中,我们介绍了LS(低边)SiC MOSFET导通时的行为。本文将介绍低边SiC MOSFET关断时的行为。

桥式结构中的栅极-

源极间电压的行为:关断时

关于桥式结构中具有驱动器源极引脚的低边SiC MOSFET关断时的行为,将与上一篇文章一样,重点介绍与没有驱动器源极引脚的TO-247N封装产品之间的区别。

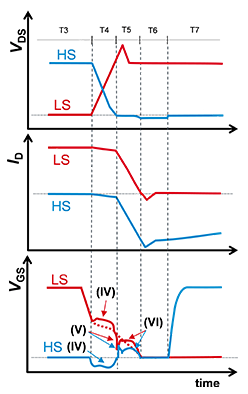

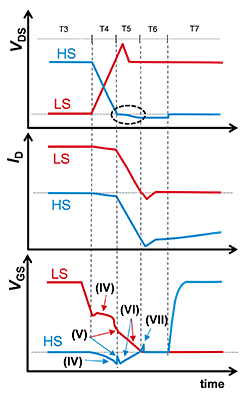

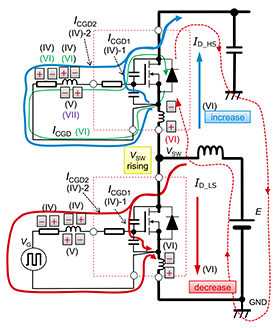

下图为关断时的各开关波形,左侧为不带驱动器源极引脚的TO-247N封装产品,右侧为带驱动器源极引脚的TO-247-4L封装产品。各横轴表示时间,时间范围Tk(k=3~7)的定义在波形图下方有述。右下方的电路图中给出了TO-247-4L封装产品在桥式电路中的栅极引脚电流情况。在波形图和电路图中,用(IV)~(VII)来表示每个时间范围中发生的事件。事件(VII)在T5期间结束后立即发生。

在桥式结构中低边SiC MOSFET

关断时的各开关波形

TO-247N封装产品

没有驱动器源极引脚

TO-247-4L封装产品

有驱动器源极引脚

时间范围的定义

T3:LS导通期间

T4:LS关断、MOSFET电压变化期间【事件(IV)同时发生】

T5:LS关断、MOSFET电流变化期间【事件(VI)同时发生】

T4~T6:HS导通之前的死区时间

T7:HS为导通期间(同步整流期间)

TO-247-4L:

LS关断时的

栅极引脚电流

在波形图比较中,TO-247-4L的事件(VI)和(VII)与TO-247N的事件不同。

事件(VI)是ID发生变化的时间点,这一点与导通时的情况一致。当HS的ID_HS急剧增加时,体二极管的VF_HS急剧上升(前面波形图中的虚线圆圈)。因此,会再次流过dVF_HS/dt导致的电流ICGD,并产生负浪涌。

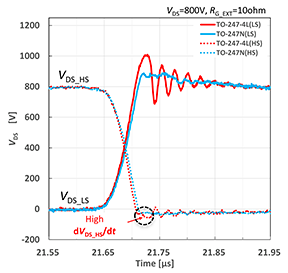

右图为关断时开关侧(LS)和换流侧(HS)的VDS波形。通过波形可以看出,与导通时的情况一样,HS的VDS_HS是在本来的dVDS_HS/dt(T4期间)结束后的ID变化时(T5期间)向负端变化,并产生了dVF_HS/dt。

TO-247-4和

TO-247-4L关断时的

VDS波形比较

事件(VII)是在T5期间结束、ID_HS的变化消失时,dVF_HS/dt消失,要流入栅极引脚的ICGD不再流动,ICGD的电流路径中存在的布线电感中积蓄的能量引起的电动势,作为栅极和源极之间的正浪涌被观测到。而在TO-247N封装的产品中,这种正浪涌几乎观测不到。

关于TO-247N封装产品关断动作的详细介绍,请参考Tech Web基础知识SiC功率元器件系列中的文章“低边开关关断时的Gate-Source间电压的动作”或应用指南的“关断时栅极信号的动作”。

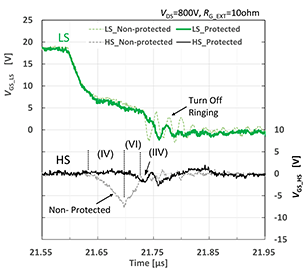

右图是TO-247-4L封装产品关断时的VGS波形。该波形图对是否采取了浪涌对策的结果进行了比较。从图中可以看出,与导通时一样,在没有采取浪涌对策(Non-Protected)的情况下,发生了前述的浪涌。而实施了浪涌对策(Protected)后,很好地抑制了VGS浪涌。

TO-247-4L关断时的VGS波形

(有无对策)

为了抑制这些浪涌,必须了解上一篇文章和本文中介绍过的栅-源电压的行为,并紧挨SiC MOSFET连接浪涌抑制电路作为对策。

如果希望了解更详细的信息,请参考应用指南中的“栅极-源极电压的浪涌抑制方法”或R课堂基础知识SiC功率元器件“SiC MOSFET:栅极-源极电压的浪涌抑制方法”(连载中)。

审核编辑:汤梓红

-

jf_66703047

2022-11-03

0 回复 举报为什么只能看几篇文章,之前的文章看不到啊 收起回复

jf_66703047

2022-11-03

0 回复 举报为什么只能看几篇文章,之前的文章看不到啊 收起回复

- 相关推荐

- 热点推荐

- 驱动器

- 引脚

- SiC MOSFET

-

SiC MOSFET 开关模块RC缓冲吸收电路的参数优化设计2025-04-23 1859

-

SiC MOSFET:桥式结构中栅极-源极间电压的动作2023-12-07 1361

-

桥式结构中的栅极-源极间电压的行为:关断时2023-12-05 1281

-

SiC MOSFET的桥式结构及栅极驱动电路2023-02-27 2449

-

低边SiC MOSFET关断时的行为2023-02-09 1101

-

SiC MOSFET:桥式结构中栅极-源极间电压的动作-前言2023-02-08 1023

-

SiCMOSFET的桥式结构详细讲解2020-12-07 803

-

SiC MOSFET SCT3030KL解决方案2019-07-09 2462

-

沟槽结构SiC-MOSFET与实际产品2018-12-05 4844

全部0条评论

快来发表一下你的评论吧 !