RISC-V入门:模块化开放式的ISA CISC和RISC代码区别

嵌入式操作系统

描述

本文是RISC-V基础知识的入门篇。介绍了开放式架构理念,模块化ISA的技术描述,以及一些商业RISC-V微处理器实现。

RISC-V开放式指令集架构是当今专有架构(如ARM架构)的流行替代方案。自诞生以来,RISC-V在学术和商业上稳步普及。了解 RISC 与 CISC

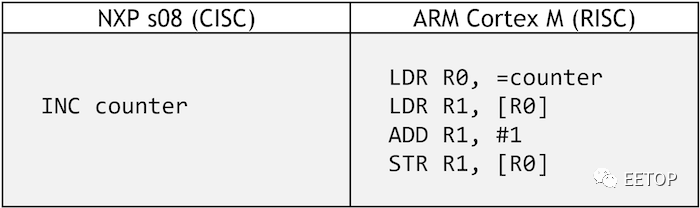

RISC是1980年代提出的一种计算机架构理念,,作为英特尔、摩托罗拉和几乎所有其他公司提供的商业体系结构的替代方案。这种架构最初被称为“复杂指令集计算机”或CISC,它依赖于密集的指令集来实现各种被认为是有用和必要的操作。然而,包括IBM和加州大学伯克利分校在内的许多研究团队发现,编译器最终通常只使用这些复杂指令集的很小一部分。这一发现,以及后续的一些其他发现,导致了对于是否需要更大的指令集的质疑,转而采用专注于将简单性作为提高效率的手段。总体而言,RISC在许多方面与CISC相反。通常,CISC中央处理器(CPU)具有少量的寄存器和大量指令集,其中大多数可以访问内存,而RISC CPU具有大量寄存器和非常适度的指令集,内存访问仅限于少数加载和存储指令。为了说明复杂指令和简单指令之间的区别,表1显示了使用CISC CPU(恩智浦的s08)和RISC CPU(ARM Cortex M0 +)递增计数器变量之间的代码比较。表 1. CISC 和 RISC 代码之间的比较示例

在此表中,CISC 允许在单个指令中递增变量,而RISC需要用加载和存储来访问内存。虽然这显示了代码大小的差异,但这不是一对一的比较,因为架构之间存在许多差异,因此这并不能证明一个在技术上比另一个更好。

如今,英特尔 x86/x64 架构证明了 CISC 微处理器没有被 RISC 取代,而 ARM 架构则证明了 RISC 已经主导了移动设备市场。RISC-V 历史

RISC的首字母缩略词是在1980年左右由加州大学伯克利分校的David Patterson教授创造的,他和斯坦福大学的John Hennessy教授共同创作了著名的书籍《计算机组织与设计》和《计算机体系结构:定量方法》。由于他们在RISC架构上的突出贡献,他们在2017年获得了ACM A.M图灵奖。从1980年到2010年,第五代RISC研究项目的开发开始了,并最终被称为RISC-V。RISC-V International— 一个开放的 ISA

RISC-V是一种开放式指令集架构(ISA),这意味着您可以自由地在微处理器或微控制器中实现RISC-V CPU,而无需向任何人支付使用此ISA的版税。

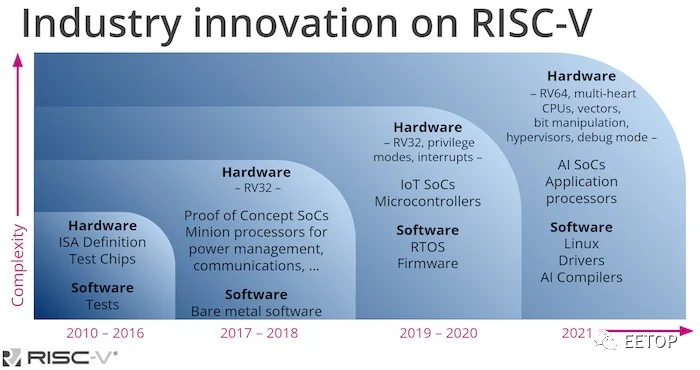

RISC-V International是一个全球性的非营利组织,拥有并维护RISC-V ISA知识产权。其主要目标之一是保持RISC-V的设计基于简单性和性能,而不是专注于商业利益。出于这个原因,RISC-V International依赖于其成员,这些成员代表了微处理器生态系统群体,从个人到Google,Intel和Nvidia等组织。成为会员有很多好处,包括有可能为ISA的设计做出贡献,并投票批准拟议的变更。在图1中,你可以看到多年来RISC-V发展的高层次时间表。

图 1. 自2010年成立以来,RISC-V一直受到微处理器行业的好评,并且在硬件和软件方面的采用一直在稳步增长

RISC-V ISA和扩展的约定

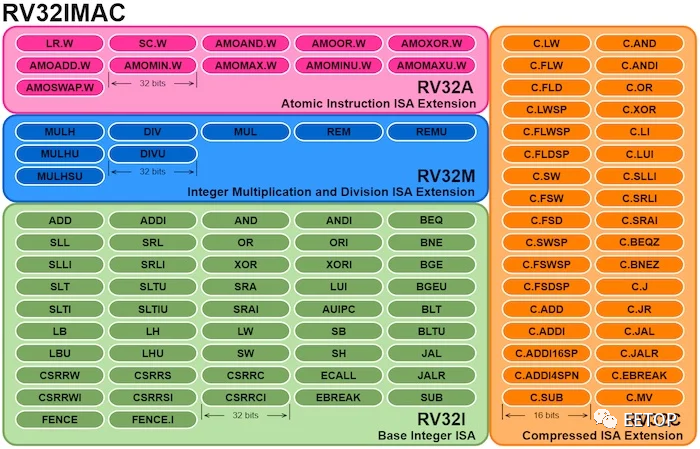

作为始于1980年的第五代研究项目,RISC-V是一个经验丰富的架构,旨在成功地解决过去其他人可能失败的问题,RISC-V旨在从过去任何潜在的错误中吸取教训。因此,RISC-V被设计为模块化ISA,而不是传统的增量ISA。这意味着RISC-V实现由一个强制性的基本ISA和许多ISA扩展组成,因此可以根据应用程序的需求定制CPU。自定义 ISA 的命名约定由字母 RV(对于 RISC-V)后跟位宽度和变体的标识符组成。例如,RV32IMAC(如图 2 所示)表示:RV32I:具有基本整数 ISA 的 32 位 CPU

M:整数乘法和除法扩展

A:原子指令扩展

C:压缩指令扩展

图 2.RV32IMAC ISA的指令集显示了RISC-V的模块化(非增量)特性。必需的基本 ISA 与一组扩展名组合在一起

编译器会被告知目标 CPU 中包含的扩展,以便它生成尽可能好的代码。如果代码包含来自缺少扩展的指令,则硬件将捕获并执行标准库中的软件函数。基本整数 ISA

RV32I 基本整数 ISA 仅包含 47 条指令,即可实现绝大多数必要的操作,以实现 32 位整数的基本功能(其 64 位变体为 RV64I)。此 ISA 以 32 位编码,包括以下说明:- 加法

- 减法

- 按位运算

- 加载和存储

- 跳转

-

分支

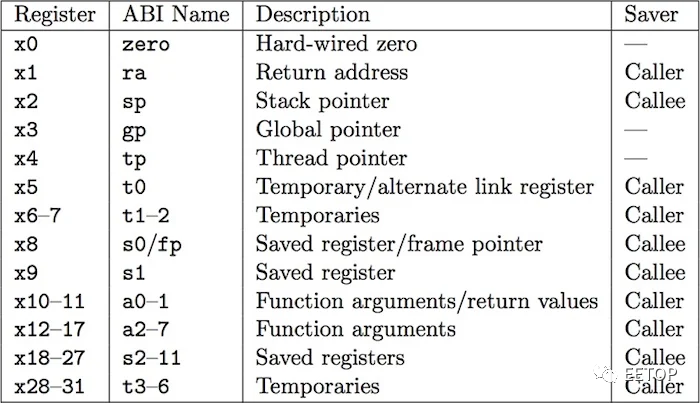

表 2.RV32I寄存器文件显示RISC-V应用二进制接口中指定的硬件寄存器名称及其分配的功能。

RISC-V 乘法和浮点

RV32M扩展实现了8条指令,以对整数执行乘法和除法(RV64M在这8条指令中增加了5条指令)。RV32F 扩展为 32 位浮点数和 26 个浮点指令增加了 32 个单独的寄存器。同样,RV32D 扩展使用 32 个 64 位浮点寄存器,支持双精度 64 位浮点数。RISC-V 指令的压缩

RV32C扩展是RISC-V ISA的一个巧妙的补充,因为它为现有指令的一个特殊子集提供了一种可选的16位编码。

在分析了现代优化编译器生成的无数行代码后,RISC-V的创建者确定了最流行的指令,并创建了16位版本,放弃了其完整32位版本的一些功能,无论如何,这些功能仍然在RV32I基础ISA中可用。

由于这些指令的存在,这种压缩是可能的:

1.有些寄存器比其他寄存器更受欢迎。

2.通常会覆盖一个操作数。

3.有一些首选的即时值。

这允许将有限数量的寄存器的指令编码为操作数,仅使用2个寄存器而不是3个,使用小的即时值,所有这些都在16位中。

通过压缩最常用的指令,您有更好的机会显着压缩程序。

其他 RISC-V 扩展

还有许多其他扩展,它们实现了您可能期望从现代微处理器获得的所有功能。这包括嵌入式基础ISA(RV32E),原子操作(A),位操作(B),矢量操作(V)的扩展,等等。

RISC-V 实现

有许多公司在其微控制器、微处理器和 SoC 中制造 RISC-V 内核的所有变体。一个例子是SiFive,这是第一家基于RISC-V ISA制造芯片的公司。他们的芯片范围从低端微控制器一直到高性能SoC。

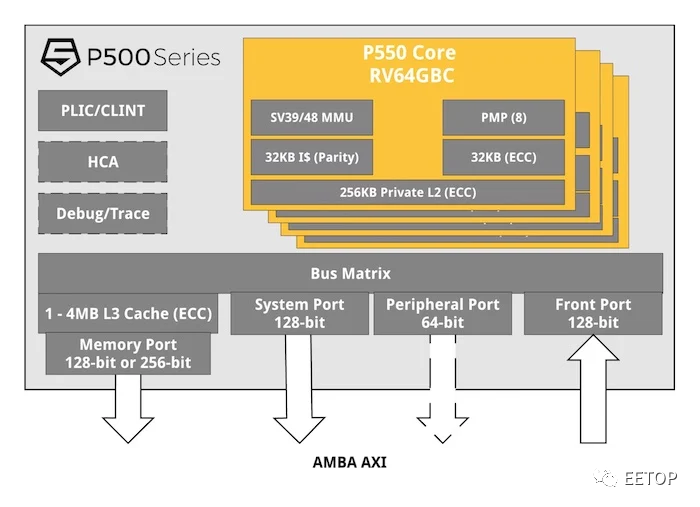

图 3. RISC-V框图的一个例子,即P550高性能应用处理器

然而,实际的RISC-V项目并不局限于集成电路。在许多领域,如编译器、模拟器、开发环境、操作系统等,正在进行的项目数量都令人印象深刻。有关项目的详细列表,请访问此GitHub (https://github.com/riscvarchive/riscv-software-list) 以了解更多信息。

总而言之,RISC-V是计算机架构世界中一个令人兴奋的话题。

-

RISC-V 手册2025-07-28 1088

-

什么是RISC-V?以及RISC-V和ARM、X86的区别2024-11-16 1518

-

RISC-V有哪些优缺点?是坚持ARM方向还是投入risc-V的怀抱?2024-04-28 2276

-

【RISC-V开放架构设计之道|阅读体验】一本别出心裁的RISC-V架构之书(第一章)2024-01-24 1075

-

【RISC-V开放架构设计之道|阅读体验】 RISC-V设计必备之案头小册2024-01-22 2023

-

risc-v是什么意思2023-03-30 2201

-

RISC-V简介2023-02-27 1346

-

RISC-V基础知识:模块化开放式的ISA CISC和RISC代码区别2022-12-23 2240

-

RISC-V 简介——理解 RISC 的开放式 ISA2022-08-25 4066

-

RISC-V ISA是怎样进行命名的2021-12-09 1693

-

RISC-V ISA 命名规范2021-11-26 1433

-

MIPS Technologies加入RISC-V,转向开源ISA标准2021-03-09 5858

-

为什么选择RISC-V?2020-07-27 5006

-

计算机RISC-V内容整理2019-07-29 2729

全部0条评论

快来发表一下你的评论吧 !