PCB设计中阻抗匹配的重要性

PCB设计

描述

将 PCB 本身视为连接多条迹线的组件是公平的。每条迹线都是不同的,有些是高速的,有些是低速的,有些是有噪声的,有些是用于电路电流的返回路径等。现在,众所周知,理想电路和实际电路存在很多差异。 假设一条高频走线是用一条走线宽度为 0.5mm 的 7mm 铜走线来布线的,它会在走线上增加电感、电容和电阻。这对高频信号线造成了困难,因为电容和电感会改变信号的频率,走线的终点会产生与走线起点完全不同的结果。此类信号的主要衰减是由于PCB 走线中的阻抗。 在本文中,我们将更多地了解PCB 阻抗匹配,以及它为何如此重要。

什么是阻抗?

您可以将阻抗视为交流电中的电阻。阻抗也以欧姆为单位,就像电阻一样,但它与电阻有很大不同。电阻欧姆适用于直流特性,但阻抗用于交流,特别是具有频率的交流。

为确保信号走线经过精心设计并且信号质量不会因走线而降低,需要仔细控制阻抗,因为 PCB 走线的阻抗通常不受控制。

PCB设计中阻抗匹配的重要性

本质上,PCB设计 中的阻抗控制是指基板材料特性与走线尺寸和位置的匹配,以确保走线信号的阻抗在特定值的一定百分比范围内。受控阻抗板提供可重复的高频性能。

以下是在 PCB 设计中控制阻抗的原因。

在高频下,PCB 上跟踪的信号不仅仅是一个连接,而是一个组件。即使是一条迹线,在不同的点也有不同的特征。

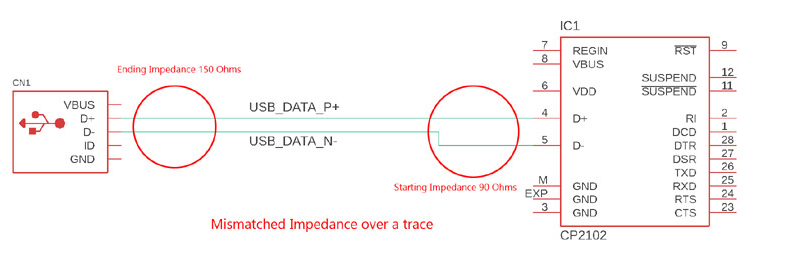

每当信号在走线中进一步移动时,不同的阻抗会产生取决于两个不匹配阻抗之间的差异的信号反射。较大的阻抗失配会产生较大的反射并影响信号完整性。

信号的反射叠加了经常被高频ADC、高速处理电路误解的实际或初级信号,无法解码实际信号。

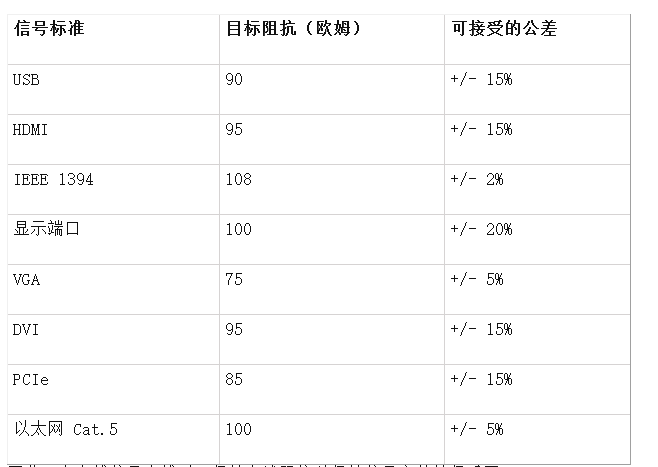

PCB 设计的标准阻抗值

不同的信号迹线需要在整个信号迹线上具有不同的阻抗特性。根据信号类型和数据传输速度或频率,下表将为不同的 PCB 信号迹线提供广泛接受的受控阻抗。

重要的是要记住,需要在整个信号路径中保持阻抗。

因此,在布线信号走线时,保持上述阻抗以保持信号完整性很重要。

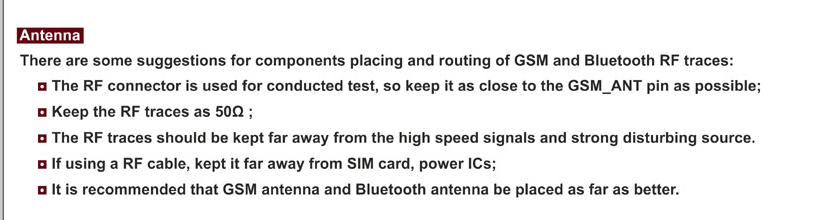

但是,除此之外,各个组件的数据表中总是会提到特定的阻抗要求。建议阅读数据表以获取有关高频迹线的信息以及特定信号的阻抗要求。

PCB 阻抗匹配 – 示例

例如,我们选择一个流行的射频模块,在物联网中广泛流行的 SIM800模块由于其低成本和易于获得。许多人使用这个模块并设计了一个可能对业余项目有好处的 PCB,但是当这个 PCB 将被测试信号电平完整性时,SIM800 的输出会很差。不仅如此,在最严重的情况下,RF 天线可能会提供较差的结果,以及 SIM800 无法在网络中工作。几乎所有情况的主要原因都是不良的 PCB 设计,尤其是射频信号路由。RF天线或RF信号是接收GSM频段数据的高频信号。这需要适当设计以减少 RF 迹线上的反射。数据表表明,RF 走线的目标阻抗应为 50 欧姆作为受控阻抗。

PCB阻抗测量和计算

大多数只是单信号路径的信号都具有单端阻抗,并且信号使用差分对阻抗以及单端阻抗。

阻抗迹线取决于以下因素:

铜迹线的宽度和厚度(在所有层中)

芯材和预浸材料的介电常数

与其他铜的距离

芯材或预浸材料的厚度。

因此,信号走线的阻抗匹配需要上述信息。在之前的文章中,我们已经了解了如何路由差分对信号。让我们匹配相同信号的阻抗,因为当阻抗匹配正确时,差分对路由完成。

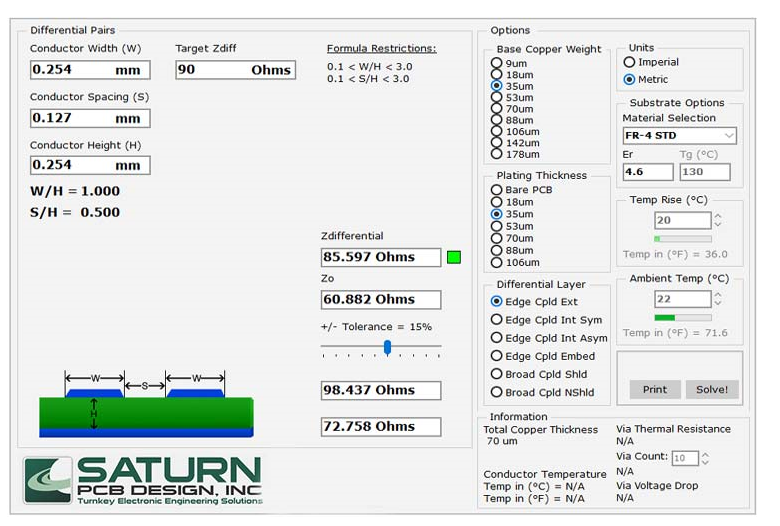

为了计算阻抗,我使用 Saturn PCB 阻抗计算器软件,Inc - PCB Toolkit V8.05,它是免费软件,在设计师中非常有名。获得所需阻抗间距的近似值等很有用。

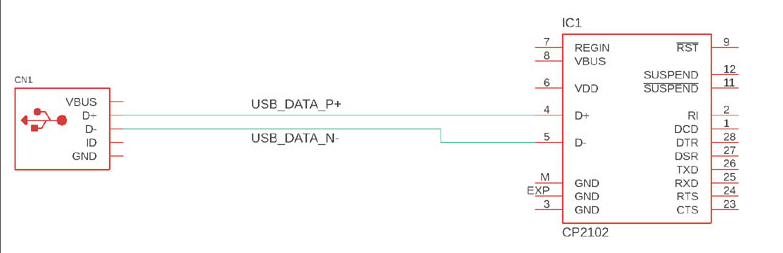

因此,需要在 USB 的 D+ 和 D- 线上匹配阻抗。由于是USB信号,阻抗要求为90欧。

以下是我的参数-

PCB - FR4,介电常数为 4.6 Er

底铜和镀层厚度均为35um

导体高度选择为 0.254mm

差分对将在顶层或底层布线

让我们计算走线厚度和走线间距-

Som 具有 15% 的容差和 90 欧姆的目标阻抗,导体宽度要求为 0.254mm,两者之间的间距要求为 0.127mm。

因此,如果我们在具有 35um 铜和镀层厚度的 FR-4 板上布线差分对,目标阻抗将接近 90 欧姆。需要仔细布线,任何地方两根导线之间的间距不应增加或减少超过 0.127mm,轨道宽度不应增加或减少超过 0.254mm。

然而,布线后的完美阻抗值和匹配只能由制造商完成。制造商需要更新,电路板需要阻抗控制,目标阻抗为差分对 90 欧姆和单端阻抗 60 欧姆。PCB的制造商将制造具有目标阻抗的PCB。

-

如何解决PCB设计中的阻抗匹配问题2012-03-03 11240

-

PCB设计中的阻抗匹配2019-02-14 5009

-

高速PCB设计中的阻抗匹配2019-05-31 1723

-

PCB阻抗匹配的方法2020-11-02 4603

-

高频高速PCB设计中的阻抗匹配,你了解多少?2023-05-26 1368

-

高速PCB中的阻抗匹配2017-08-28 1788

-

怎样理解阻抗匹配_pcb阻抗匹配如何计算2018-05-02 45373

-

PCB设计中的阻抗匹配的介绍特征阻抗及常见阻抗匹配的方式详细概述2018-07-12 2384

-

技术 | 如何解决PCB设计中的阻抗匹配问题2019-06-21 7778

-

【硬见小百科】高速PCB设计中的阻抗匹配2019-12-13 3960

-

PCB设计阻抗匹配问题的解决办法2020-11-12 6081

-

阻抗匹配的重要性及理想模型2023-07-04 2979

-

什么是阻抗匹配?高速PCB设计为什么要控制阻抗匹配?2023-10-30 4197

-

PCB阻抗匹配过孔的多个因素你知道哪些?2024-07-04 3600

-

技术资讯 I 信号完整性与阻抗匹配的关系2025-09-05 5339

全部0条评论

快来发表一下你的评论吧 !