Arm用新的SoC和演示板测试安全架构

电子说

描述

Arm 公司最近宣布了一个新的原型架构,这个架构是从其 Morello 项目中分离出来的,它可能为下一代数据安全系统铺平道路

几年前,剑桥大学(University of Cambridge)的研究人员与 ARM 合作,开发了一种名为 CHERI 的实验架构ーー能够增强硬件性能的 RISC 指令ーー该指令使用64位 Armv8-A 来解决内存安全问题,尤其是在编程语言中。

在 CHERI 保护模型的基础上,安谋与剑桥大学(University of Cambridge)合作,创建了“莫雷洛计划”(Morello program) ,并于2019年启动了为处理器设计安全硬件架构的爱丁堡大学。

Arm Morello SoC.作为这个项目的一部分,Arm 公司现在已经使用基于 CHERI 的 Morello 原型架构构建了一个系统芯片(SoC)和一个演示板。这种架构据说可以增强内存保护和扩展软件防火分区,目的是保护内存不安全的语言不受各种漏洞的影响。

内存安全可能取决于编程语言

内存安全是现代嵌入式设计面临的最紧迫的挑战之一。像健身追踪器、智能手机、笔记本电脑,甚至基于物联网的智能汽车这样的智能设备存储着诸如照片、交易凭证和保存的密码等敏感信息,以及许多其他类型的个人数据。

内存安全也是一些编程语言的关键属性。内存安全语言防止程序员引入某些缺陷或错误来控制设备的内存。这样的语言包括 C # 、 Java 和 Python。相反,C、 C + + 和汇编语言是内存不安全的。

使用内存安全语言,用户可能允许访问内存中的某些地址范围。即便如此,如果程序员试图访问超出范围的地址,这个人应该会收到一个错误,否则程序就会崩溃。但是,内存不安全的语言允许程序员读取所有内存内容。

CHERI 建筑

为了减轻这种内存漏洞,CHERI 被开发为一种混合能力架构来扩展传统的硬件指令集架构(ISA)。体系结构增加了指针(在内存中引用地址的变量)的使用限制。这样,只能引用一些确定的地址范围。一旦物理实现,指针的地址访问就不能被软件内存不安全的语言伪造。

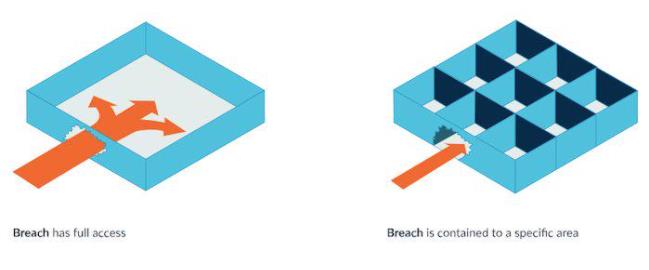

说明 CHERI 架构如何通过防火分区提高内存安全性的插图

CHERI 还可用于将关键地址块与其他非关键地址块分离。研究人员称之为防火分区。在这里,代码的关键部分被隔离在一个隔间中。因此,即使程序员破坏了代码的一部分,他们也只能被困在那个隔间里。

Morello 系统芯片设计

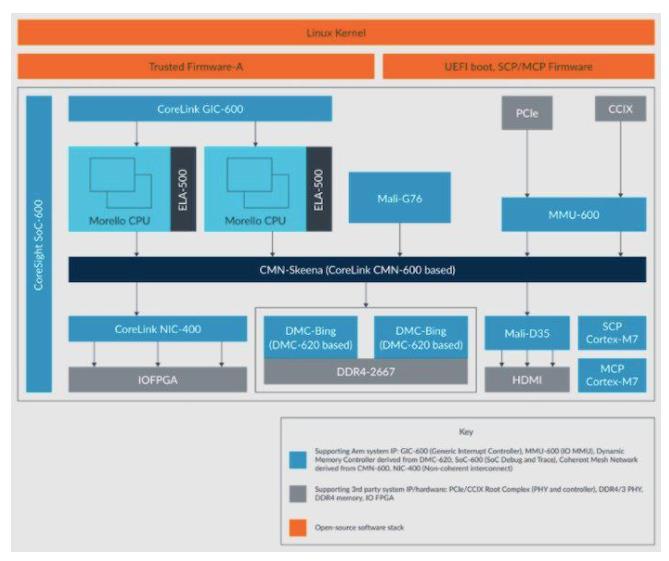

Morello SoC 基于 ARM 的 N1SDP 平台,其中四个 CPU 的配置被分配到两个 CPU 集群中。在 Morello SoC 中复制了类似的配置,以及新的互连和动态内存控制器。它还使用相同的系统控制处理器(SCP)和可管理性控制协议(MCP)。

由于 SoC 预计将运行操作系统,因此它集成了 Arm Mario-G76图形处理器和 Ma-D35显示处理器。

Morello SoC 配置

除了硬件,ARM 工程师还开发了软件工具链,主要是 LLVM 和 Clang 工具链,实现了 Morello 架构。Arm 创建了一个内部 FPGA,以方便操作系统在 SoC 数据库被录制用于制造之前启动 SoC 设计。

莫雷洛示范委员会

Morello 演示板嵌入了 Arm v8-2-A 处理器。它的特点是 ARM 的 ULINK-Plug 调试适配器,它消除了对单独适配器的需要。根据研究人员的说法,演示板可以让研究人员实际评估和测试安全效益。

固件包括 SRP、 TF-A 和 UEFIED2,以支持操作系统的引导。研究人员报告称启动了一系列 Arm 64位操作系统,包括 Linux、 Android 11和 Windows 11。

Arm 正在通过 UKRI Digital Security by Design (DSbD)计划,将董事会分发给大学和企业中感兴趣的合作伙伴,其中最著名的两家是谷歌(Google)和微软(Microsoft)。

莫雷洛计划的下一步是什么?

随着 Morello 架构的硬件实现现已可用,ARM 和剑桥的研究人员现在正在寻找这种架构的未来机会。他们还在开发第二个基于 GNU 的工具链,以及一个新的 Linux 内核用户 ABI,以促进纯功能用户空间软件的生产。

莫雷洛研究项目的下一阶段将持续到五年计划结束。

-

浅析PSA平台安全架构2019-07-25 1925

-

阿里云安全肖力:云原生安全构筑下一代企业安全架构2019-09-29 3009

-

关于PSA平台安全架构看完你就懂了2021-05-18 2322

-

请教大神怎样去设计一种DBAS应用系统安全架构?2021-07-22 1655

-

Arm的平台安全架构(PSA)干货2021-07-27 1873

-

Arm 用新的 SoC 和演示板测试安全架构2022-06-16 2180

-

Arm平台安全架构固件框架1.02023-08-08 769

-

Arm推出平台安全架构PSA 为万亿互联设备建立行业通用框架2017-10-24 11212

-

Arm推出平台安全架构PSA,为万亿互联设备建立行业通用框架2017-10-25 6941

-

ARM推出最新安全架构,支持物联网多样化、碎片化2017-12-04 1116

-

Arm安全架构入选“2017世界互联网领先科技成果”2017-12-12 7133

-

车载信息安全架构与应用实例2019-01-17 4563

-

Arm PSA安全架构助你轻松解决不同行业中的安全挑战2019-06-20 4734

-

建立云安全架构的解决方案及技术综述2021-06-14 2491

-

搭配Arm开源固件TF-M,共同形成完整IoT应用平台安全架构2023-08-10 1533

全部0条评论

快来发表一下你的评论吧 !