AXI VIP设计示例 AXI接口传输分析

接口/总线/驱动

描述

赛灵思 AXI Verification IP (AXI VIP) 是支持用户对 AXI4 和 AXI4-Lite 进行仿真的 IP。它还可作为 AXI Protocol Checker 来使用。

此 IP 只是仿真 IP,将不进行综合(它将在 Pass-through 配置中被连线所替代)。

AXI VIP IP 核用途如下:

生成 Master AXI 指令和写内容

生成 Slave AXI 读内容和写响应

检查 AXI 传输是否符合协议标准

它支持 5 种不同配置:

AXI Master VIP

AXI Pass-through VIP(无内存模型)

AXI Pass-through VIP(有内存模型)

AXI Slave VIP(无内存模型)

AXI Slave VIP(有内存模型)

如需获取 AXI VIP IP 核相关文档,请扫码参阅

AXI VIP 设计示例

在 Vivado 中提供了一个 AXI VIP 设计示例。

要为 AXI VIP 生成设计示例,只需遵循以下步骤进行操作即可:

打开新工程,并单击“IP Catalog”。

搜索“AXI Verification IP”。双击并配置 IP,然后 generate IP。

右键单击此 IP 并选择“Open IP Example Design”

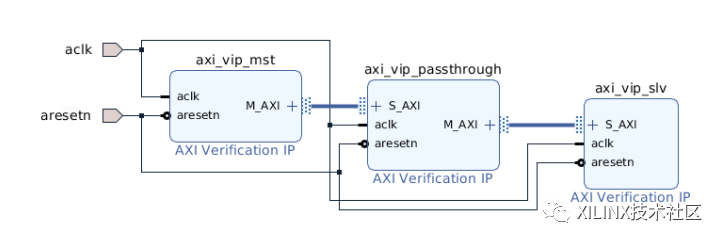

AXI VIP 的设计示例包含 3 个 AXI VIP:其中一个配置为 Master、一个配置为 Pass-through,另一个配置为 Slave。

工程中包含了多个 Test Bench 源文件,以匹配不同 AXI VIP 组合:

注:所有 Test Bench 文件均为 SystemVerilog 语言。要使用 AXI VIP 的全部功能,应将此 IP 例化包含在 SystemVerilog Test Bench 文件中。

分析 AXI 接口传输

Vivado 仿真中的实用功能之一是可将协议实例添加到波形图中以在传输级别来查看信号。

我将逐一介绍sim_basic_mst_active_pt_mem__slv_passive 仿真集的步骤。

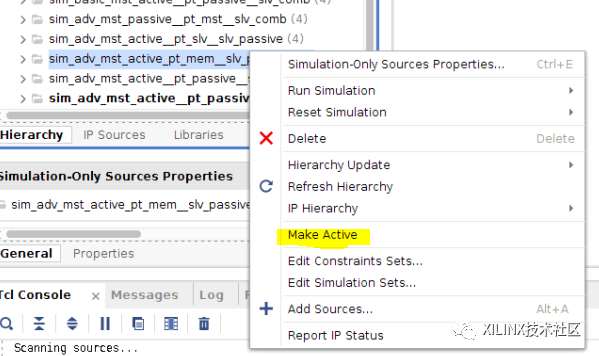

要使用该仿真集,请在“Source”窗口中右键单击它,然后单击“Make Active”。

该仿真集仅使用 Master AXI VIP 和 Pass-through AXI VIP(充当内存级别的 Slave 设备)。

可单击 Flow Navigator 中的“Run Simulation”来运行仿真。

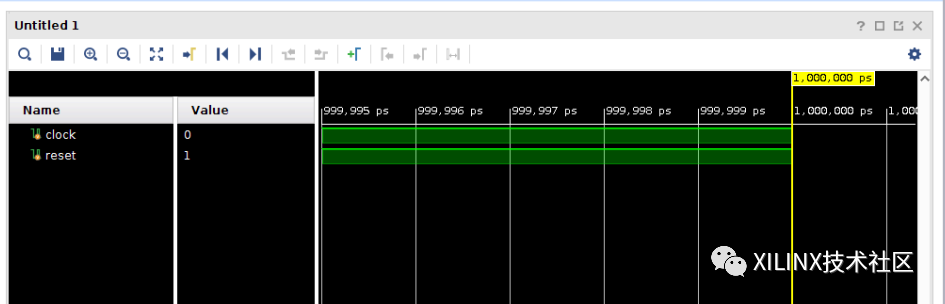

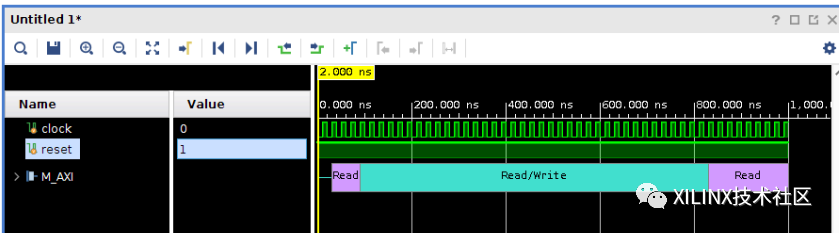

默认情况下,这将打开仅含时钟和复位信号的波形图。

我们将添加 Master AXI VIP 和 Pass-through AXI VIP 之间的 AXI 接口。

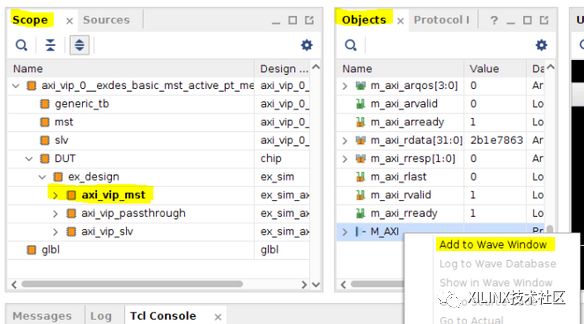

在“Scope”窗口中,查找并选中“DUT”>“ex_design”下的主设备 AXI VIP (axi_vip_mst)。随后,“Objects”窗口将显示 IP 的所有端口。找到 M_AXI 接口对象并单击“Add to Wave Window”。

随后,即可在波形图窗口中看到 AXI 传输信号:

可以看到,在开始时间与仿真时间 1us 之间,读取 (Read) 和写入(Write) 传输均已发生。

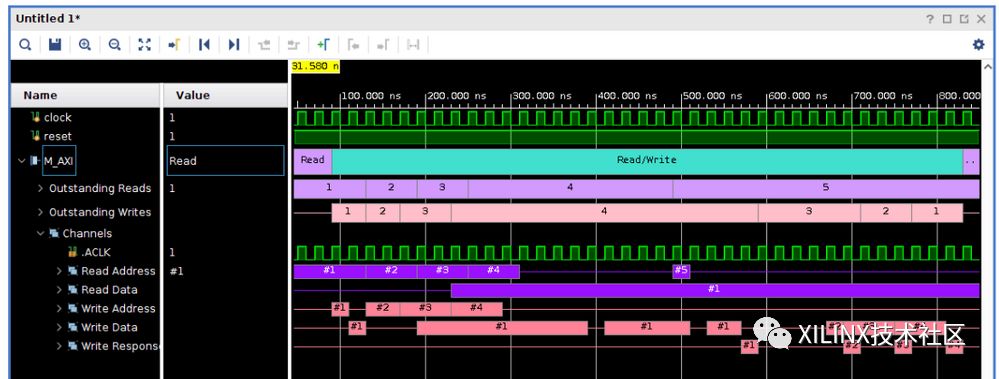

在波形图窗口中可展开 M_AXI 接口以查看所有信号波形:

每个通道上面的数字对应于传输数量。可以看到在Read通道(紫色)上有 5 次读传输,Write通道上有 4 次传输。

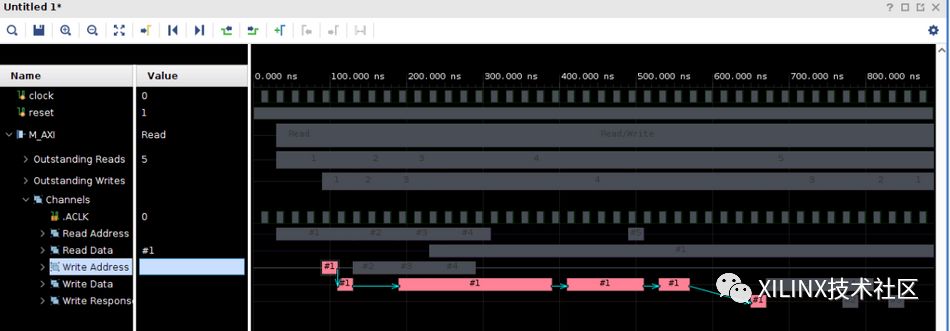

单击特定传输即可看到其详细过程。例如,如果单击Write通道上的第一次传输,即可看到此传输为 burst 传输类型:

此传输事务首先在Write Address通道上写入地址

然后,在Write Data通道上发送 burst 数据

最后,如果写数据成功,Slave 会在Write Response通道上返回响应

审核编辑:汤梓红

-

RDMA简介8之AXI分析2025-06-24 756

-

AXI接口FIFO简介2025-03-17 2331

-

AXI传输数据的过程2023-10-31 2348

-

AXI VIP当作master时如何使用?2023-07-27 3413

-

AXI接口协议详解2022-10-14 2933

-

如何使用Xilinx AXI VIP对自己的设计搭建仿真验证环境的方法2022-10-09 5121

-

使用AXI VIP的几个关键步骤及常见功能2022-10-08 7796

-

AXI VIP 中产生传输事务的基本方法2022-08-29 3244

-

如何将AXI VIP添加到Vivado工程中2022-07-08 2834

-

AXI4 、 AXI4-Lite 、AXI4-Stream接口2022-07-04 10919

-

如何创建AXI CDMA Linux用户空间示例应用2020-09-28 3317

-

如何使用Xilinx AXI进行验证和调试2018-11-20 4857

-

AXI接口简介_AXI IP核的创建流程及读写逻辑分析2018-06-29 17981

全部0条评论

快来发表一下你的评论吧 !