如何将AXI VIP添加到Vivado工程中

接口/总线/驱动

描述

在这篇新博文中,我们来聊一聊如何将 AXI VIP 添加到 Vivado 工程中,并对 AXI4-Lite 接口进行仿真。随后,我们将在仿真波形窗口中讲解用于AXI4-Lite 传输事务的信号。

使用 AXI VIP 作为 AXI4-Lite 主接口(教程)

-

下载设计文件(本文后附)

-

打开 Vivado 2019.2。

-

在 Tcl 控制台中,使用 cd 命令进入解压缩的目录 (cd AXI_Basics_3)

-

在 Tcl 中,使用 source 命令执行tcl脚本(source./create_proj.tcl)

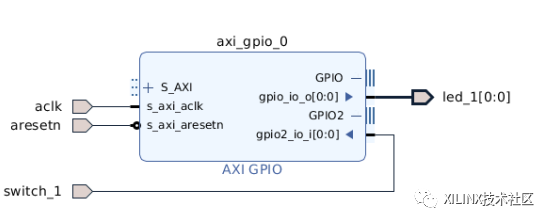

这将创建 1 个 Vivado 工程,其中附带包含 AXI GPIO IP 的块设计 (Block Design)。此 AXI GPIO IP 的通道 1作为外部输出接口,用于仿真到板载 LED 的连接,我们将尝试通过 AXI4-Lite 传输事务来开关此 LED;同时,此 IP 的通道 2作为外部输入接口,用于仿真到板载开关的连接,我们将尝试读取此开关的状态。

5. 将 AXI Verification IP (AXI VIP) 添加到设计中。

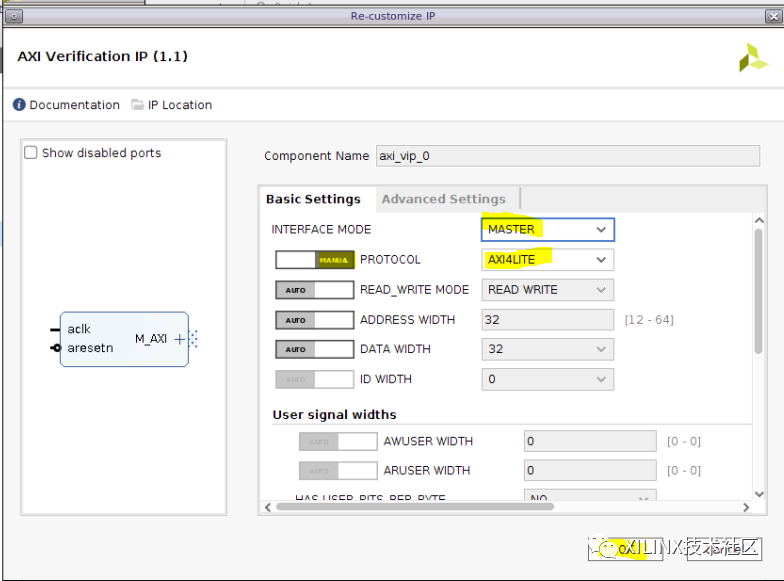

6. 双击 AXI VIP 打开其配置 GUI,并修改以下参数:

-

Interface mode:MASTER

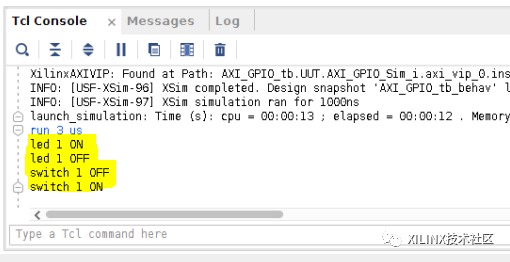

-

Protocol (MANUAL):AXI4LITE

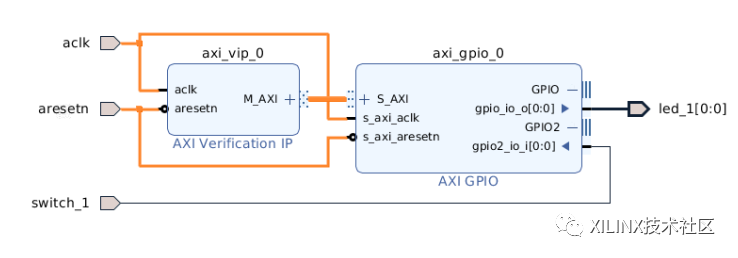

7. 将 AXI VIP 的 AXI4-Lite 主接口 (M_AXI) 连接到 AXI GPIO IP 的 AXI4-Lite 从接口 (S_AXI),将 AXI VIP 的 aclk 和 aresetn 端口连接到块设计的输入

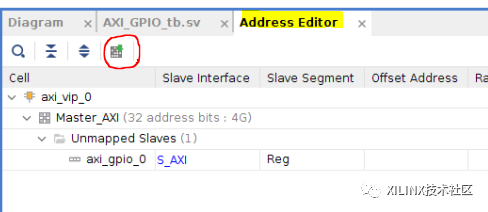

8. 打开“地址编辑器 (Address Editor)”选项卡(“窗口 (Window) > 地址编辑器 (Address Editor)”),然后单击“自动分配地址 (Auto Assign Address)”图标

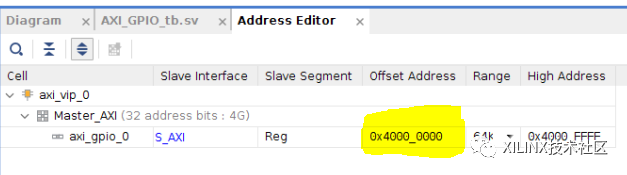

9.确认此地址设置为 0x4000_0000

注:此处地址的上半部分无关紧要,因为 AXI GPIO 的 S_AXI 接口,其中仅有 9 个地址位连接到 AXI VIP

点击“验证块设计”图标。确保其中不存在任何严重警告或错误。然后保存块设计。现在,我们需要更新测试激励文件,以声明例化并控制 AXI VIP。为此,我们将按照(PG267(2019年 10 月 30 日v1.1))中“实用编码指南与示例”章节的内容来进行操作。

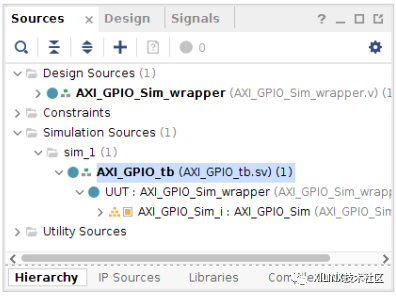

11. 从“源 (Sources)”窗口打开测试激励文件 AXI_GPIO_tb.sv

测试激励文件中已包含部分信号(例如,时钟和复位)的控制逻辑,并包含将 LED 状态输出至控制台的流程。

always @(posedge led_1)

begin

$display("led 1 ON");

end

always @(negedge led_1)

begin

$display("led 1 OFF");

end

在“实用编码指南与示例”中提到的第 1 步是在 SystemVerilog 测试激励中创建 1 个模块。此操作在此测试激励文件中已完成。

第 2 步是导入 2 个必需的包:axi_vip_pkg 和

注:请使用以下 Tcl 命令来查找 VIP 实例的

随附的测试激励中假定 AXI 组件名称为 design_1_axi_vip_0_0(添加到 BD 的首个 AXI VIP 的默认名称)

get_ips *vip*

12. 在第 58 行附近添加以下行

//Step 2 - Import two required packages: axi_vip_pkg and

import axi_vip_pkg::*;

import AXI_GPIO_Sim_axi_vip_0_0_pkg::*;

第3 步是声明VIP 主接口的代理(agent)

13. 在第 102 行附近添加以下行

// Step 3 - Declare the agent for the master VIP

AXI_GPIO_Sim_axi_vip_0_0_mst_t master_agent;

第 4 步和第 5 步为创建新代理并将其启动。

14. 在第 107 行附近添加以下行

// Step 4 - Create a new agent

master_agent = new("master vip agent",UUT.AXI_GPIO_Sim_i.axi_vip_0.inst.IF);

// Step 5 - Start the agent

master_agent.start_master();

准备就绪,可以发送传输事务了。

发送 AXI4-Lite 传输事务其实很简单。

只需使用AXI4LITE_WRITE_BURST(addr,prot,data,resp) API 执行写传输事务,

使用AXI4LITE_READ_BURST(addr,prot,data,resp) API 执行读传输事务即可。

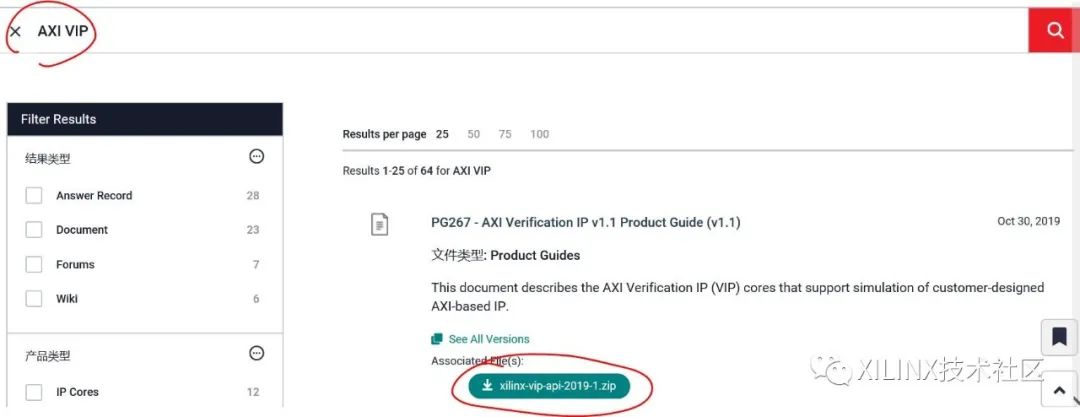

注:AXI VIP 的所有 API 都记录在 zip 文件中,您可从 china.xilinx.com 下载该文件。

(下载方法如下:

在本教程中,我们将尝试开关连接到 AXI GPIO 通道 1 的 LED_1,并读取连接到 AXI GPIO 通道 2 的 SWITCH_1 的状态。

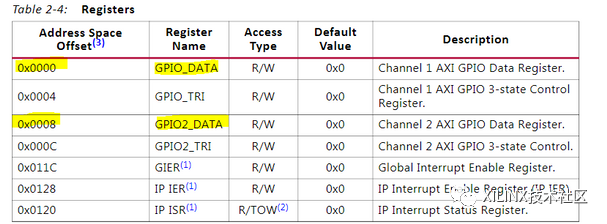

通过查看 AXI GPIO IP 的寄存器映射((PG144)的表 2-4)可知,我们必须在地址 0x0 执行写操作,在地址 0x8 执行读操作:

我们将从写操作开始,尝试切换 LED_1 的状态。

15. 添加以下代码以将 0x1 写入 AXI GPIO 寄存器 0x0,这样应可开启此 LED

//Send 0x1 to the AXI GPIO Data register 1

#500ns

addr = 0;

data = 1;

master_agent.AXI4LITE_WRITE_BURST(base_addr + addr,0,data,resp);

16. 添加以下代码以将 0x0 写入 AXI GPIO 寄存器 0x0,这样应可关闭此 LED

//Send 0x0 to the AXI GPIO Data register 1

#200ns

addr = 0;

data = 0;

master_agent.AXI4LITE_WRITE_BURST(base_addr + addr,0,data,resp);

下一步,我们将读取开关位置的每次变更,并向控制台显示开关状态。

17. 添加对应于读传输事务的以下代码:

// Switch in OFF position

switch_1 = 0;

// Read the AXI GPIO Data register 2

#200ns

addr = 8;

master_agent.AXI4LITE_READ_BURST(base_addr + addr,0,data,resp);

switch_state = data&1'h1;

if(switch_state == 0)

$display("switch 1 OFF");

else

$display("switch 1 ON");

// Switch in ON position

switch_1 = 1;

// Read the AXI GPIO Data register 2

#200ns

addr = 8;

master_agent.AXI4LITE_READ_BURST(base_addr + addr,0,data,resp);

switch_state = data&1'h1;

if(switch_state == 0)

$display("switch 1 OFF");

else

$display("switch 1 ON");

18. 启动仿真,并使其运行 3us。在 Tcl 控制台中,您应可看到该 LED 的开启和关闭,并可看到开关状态

现在,我们即可对 AXI4-Lite 接口上的传输事务进行分析

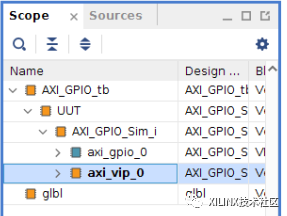

19. 在“范围 (Scope)”窗口中,选中位于“AXI_GPIO_tb > UUT >AXI_GPIO_Sim_i”下的 axi_vip_0

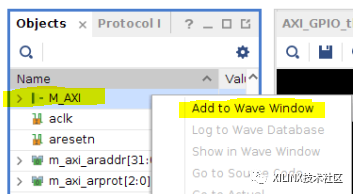

20. 在“对象 (Objects)”窗口中,右键单击 M_AXI 协议实例,然后单击“添加到波形窗口 (Add to Wave Window)”

21. 重新启动仿真,并运行 3us

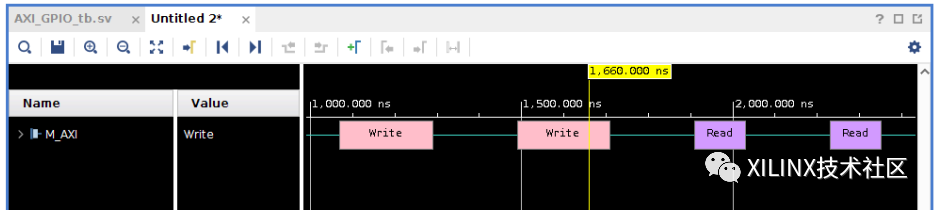

这样在 AXI4-Lite 接口上将可看到 4 个传输事务:2 个写传输事务后接 2 个读传输事务

22. 展开 M_AXI 协议实例,查看各个通道

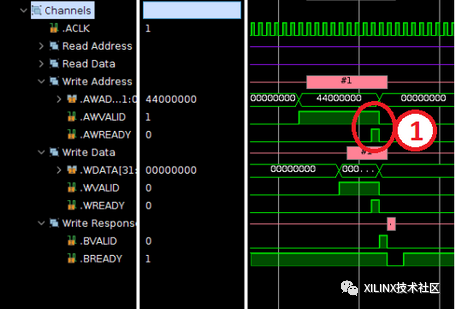

这样可以看到写传输事务中的各个步骤。首先,当 READY 和 VALID 信号在写地址通道上均处于高位(AWREADY 和 AWVALID)时,地址从主接口传输到从接口

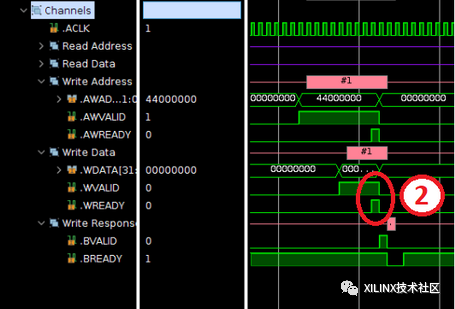

随后,当 READY 和 VALID 信号在写通道上均处于高位(WREADY 和 WVALID)时,数据从主接口传输到从接口。

注:每个地址仅传输一个数据,因为在 AXI4-Lite 接口上不支持突发 (burst) 读写。

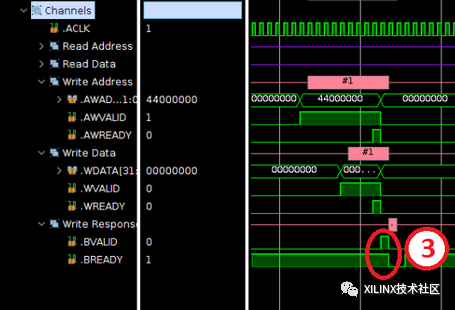

最后,当从接口在写响应通道上发送写响应(以表明写操作是否成功)时,写传输事务即告完成。当 READY 和 VALID 信号在写响应通道上均处于高位(BREADY 和 BVALID)时,响应从从接口传输到主接口

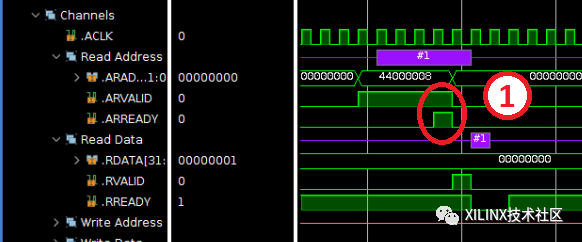

对于读传输事务,同样可执行此分析。首先,当 READY 和 VALID 信号在读地址通道上均处于高位(ARREADY 和 ARVALID)时,地址从主接口传输到从接口

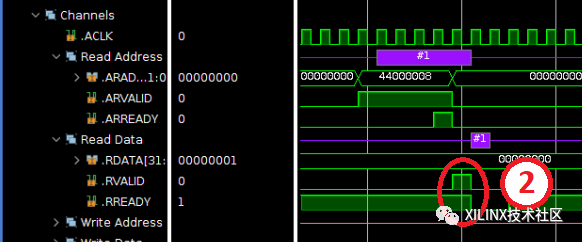

随后,当 READY 和 VALID 信号在读通道上均处于高位(RREADY 和 RVALID)时,数据从从接口传输至主接口。

注:执行读传输事务期间,从接口也会发送读响应以指示读操作是否成功。

此响应将与读通道上的数据同时发送。

往期精选

-

AXI VIP当作master时如何使用2023-07-27 2526

-

如何将F-RAM™添加到现有的PSoC™ Creator项目?2024-03-01 510

-

xilinx EDF已经综合过的网表文件怎样添加到Vivado工程中?2016-09-07 15584

-

怎么将纯文本文件添加到Vivado项目2020-04-08 6734

-

如何将CML逻辑添加到IBIS模型中?2020-04-13 1899

-

如何将库添加到设计中并使用Tcl脚本编译?2020-04-16 1555

-

将新库添加到Petalinux rootfs的最简单方法是什么2020-05-22 3810

-

请问如何将自己的代码添加到工程中?2022-01-05 1266

-

如何将RAFL添加到我的项目的适当示例和/或文档?2023-01-10 686

-

如何将应用程序添加到任务栏?2009-07-31 6697

-

如何将TDM业务添加到WiMAX平台上2009-10-20 992

-

如何将Crosswalk添加到Cordova应用程序中2018-11-07 3335

-

如何将WizFi360 EVB Mini添加到树莓派Pico Python2022-12-01 792

-

将RTL模块添加到Block Design的步骤2023-06-11 6181

-

如何将溶解氧添加到WiFi水培套件2023-06-14 681

全部0条评论

快来发表一下你的评论吧 !