如何导出IP以供在 Vivado Design Suite 中使用

描述

在 AXI 基础第 6 讲 - Vitis HLS 中的 AXI4-Lite 简介中,使用 C 语言在 HLS 中创建包含 AXI4-Lite 接口的 IP。

在本篇博文中,我们将学习如何导出 IP 以供在 Vivado Design Suite 中使用、如何将其连接到其它 IP 核与处理器以及如何在板上运行工程。

本篇博文将分为 3 个部分:

1. 从 Vitis HLS 导出 IP。

2. 使用Vivado Design Suite创建硬件。

3. 在Vitis 统一软件平台中编写软件并在板上运行。

01

导出 IP

在AXI 基础第 6 讲 - Vitis HLS 中的 AXI4-Lite 简介中(AXI 第六讲请回复本公众号AXI 获得),我们创建了 1 个包含 AXI4-Lite 接口的 IP。如果要把新 IP 连接到任何其它 IP 或者连接到 PS,则首先需要将软件代码综合成 RTL(即,将其转换为硬件)。随后,我们就可以将 RTL IP 导出到 Vivado Design Suite,以便在其中将其连接到其它 IP 核或者连接到 PS。

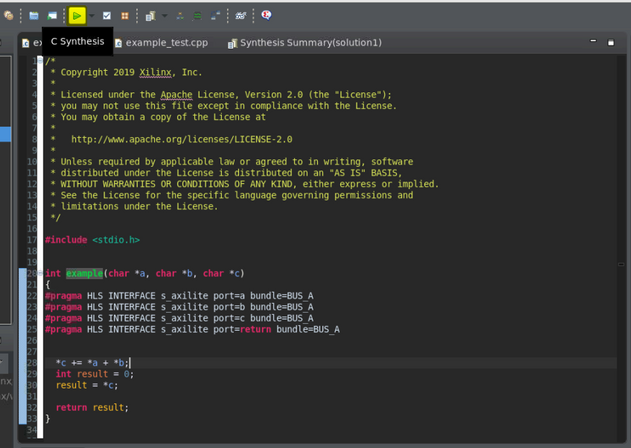

1.1. 按如下所示编辑代码,然后保存。

int example(char *a, char *b, char *c)

{

#pragma HLS INTERFACE s_axilite port=a bundle=BUS_A

#pragma HLS INTERFACE s_axilite port=b bundle=BUS_A

#pragma HLS INTERFACE s_axilite port=c bundle=BUS_A

#pragma HLS INTERFACE s_axilite port=return bundle=BUS_A

*c += *a + *b;

int result = 0;

result = *c;

return result;

}

1.2. 鉴于我们将在板上运行此代码,因此需要将综合设置更改为对应于可用的开发板的设置。

我这里选择的是 Zynq UltraScale+ ZCU106 评估板。要更改所使用的开发板,请转至“解决方案 (Solution) -> 解决方案设置 (Solution Settings) -> 综合设置 (Synthesis Settings)”,然后选择如下所示高亮的“...”即可选择可用的开发板。

1.3. 选择屏幕顶部的绿色运行按钮 即可运行 C 语言综合。这样即可将代码转换为 RTL:

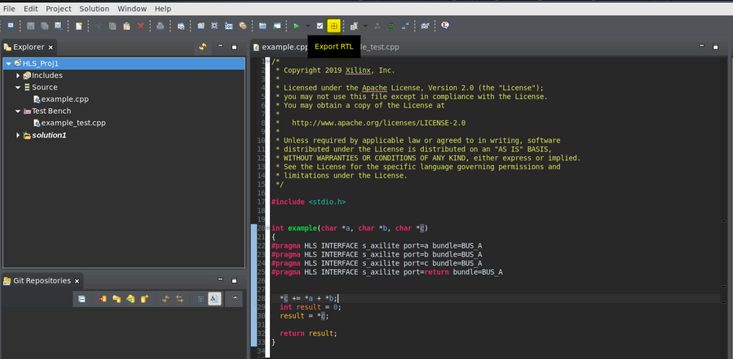

1.4. 完成综合后,您可选择“导出 RTL (ExportRTL)”工具栏按钮,或者也可以单击“解决方案 (Solution) -> 导出 RTL (Export RTL)”以打开“Export RTL”对话框。

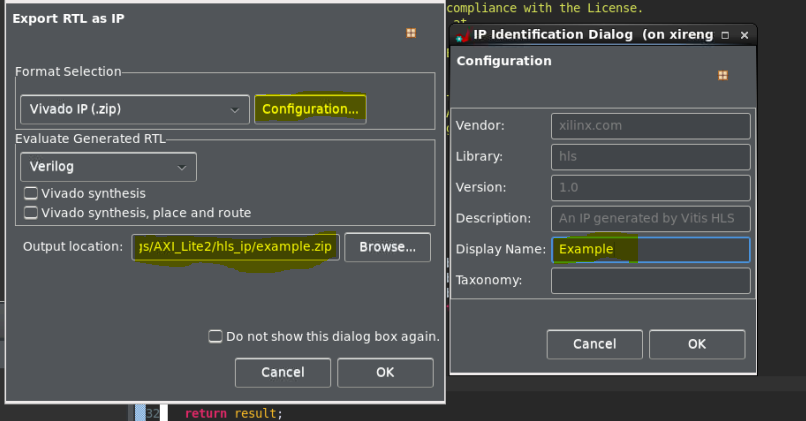

1.5. 打开的对话框应如下截屏所示。

本文包含有关所有可用选项的详细解释。

选择“配置 (configuration)”选项,为新 RTL IP 添加详细信息。将显示名称更改为“Example”,然后选择“确定 (OK)”。当您在 Vivado Design Suite 中打开自己的 IP 时,将显示此名称。

选择“浏览 (Browse)”按钮以选择 Vivado IP (.zip) 文件的输出位置及其名称。输出的 ZIP 文件将包含您的 RTL IP,您可将其导入 Vivado Design Suite。

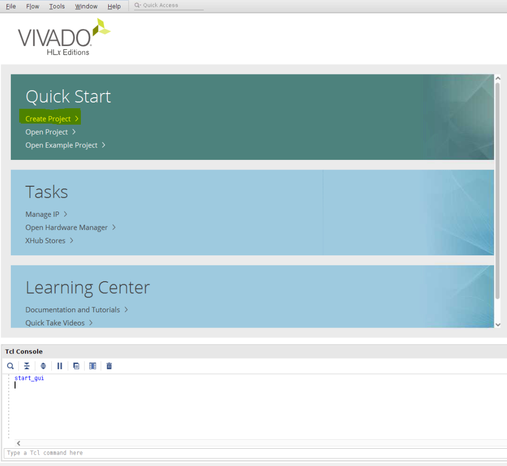

1.6. 等待工具完成导出,然后打开 Vivado Design Suite。选择“创建新工程”选项:

1.7. 对于后续所有其它步骤,请选择“下一步 (Next)”。选择器件时,请务必选择您在创建工程时所选的器件。如果您不确定,可在 Vitis HLS 中的“解决方案设置 (solution settings) -> 综合设置 (synthesis settings)”下找到该器件。如果您选择其它器件,那么将您的 IP 导入 Vivado Design Suite 时可能会出现问题。

最后,选择“完成 (Finish)”以打开空工程。

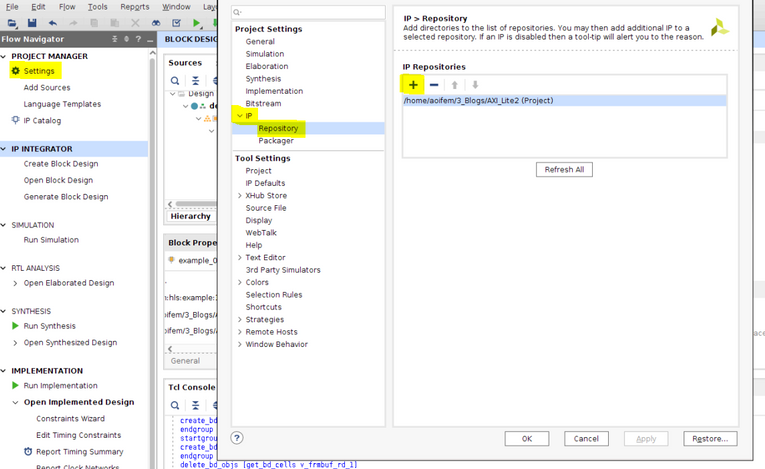

1.8. 要使用 Vivado 工程中生成的 IP,首先必须将新 IP 存储库添加到 Vivado 工程中。此处所示文件夹包含从 Vitis HLS 导出的 .zip 文件。要添加存储库,请选择“设置 (Settings) -> IP -> 存储库 (Repository)”。选择 + 按钮并在 Vitis HLS 中选择 IP 导出的位置(即,以上第 6 步)。

选择位于对话框底部的“应用 (Apply)”按钮,然后选择“确定 (OK)”。

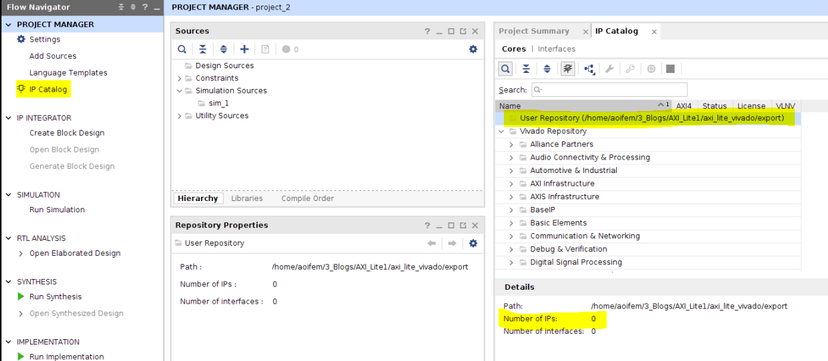

1.9. 选择 IP 目录 (Select IP Catalog)。现在,您的新存储库应已显示在目录中。

如已成功导入 IP,那么详细信息窗口中所列出的 IP 数量应为“1”。

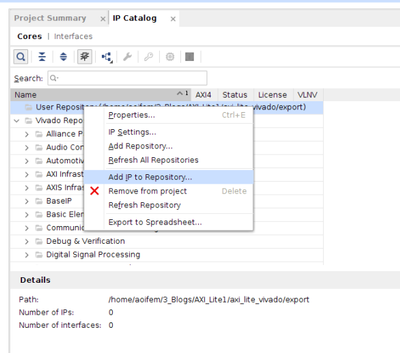

注:如果列出的 IP 数量为 0,那么您可右键单击自己的新存储库并选择“将 IP 添加到存储库中 (Add IP to Repository)”。选择您从 Vitis HLS 导出的 ZIP 文件。随后,存储库中的 IP 数量应已显示为“1”。如果未显示正确数量,请检查您在 Vitis HLS 中所选的板/器件与您在 Vivado 中所使用的是否相同,否则,则表示您的 IP 可能不兼容。

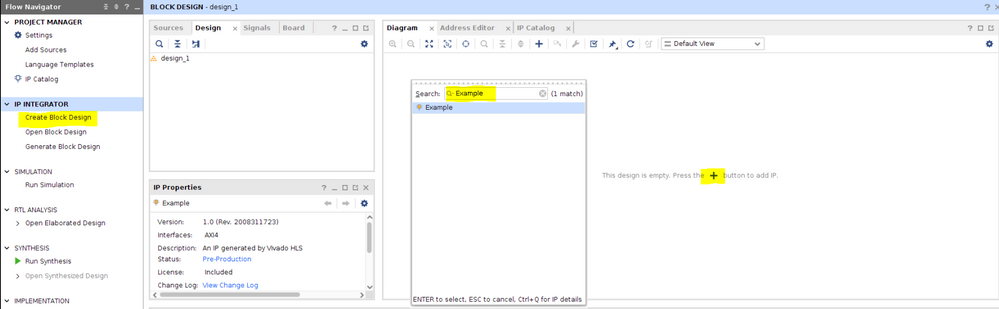

1.10. 在 Flow Navigator 中,选择“创建模块设计 (Create Block Design)”。

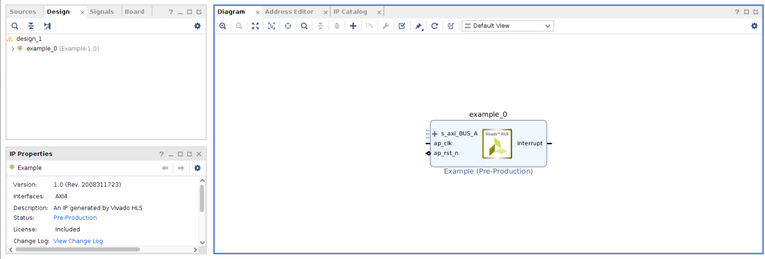

在显示的选项卡中,选择 + 按钮并搜索您在第 6 步中在 Vitis HLS 中指定的 IP 名称(即,Example)。

祝贺您!您已成功创建了 IP、将其从 Vitis HLS 导出并已添加到 Vivado Design Suite 中的模块设计中。

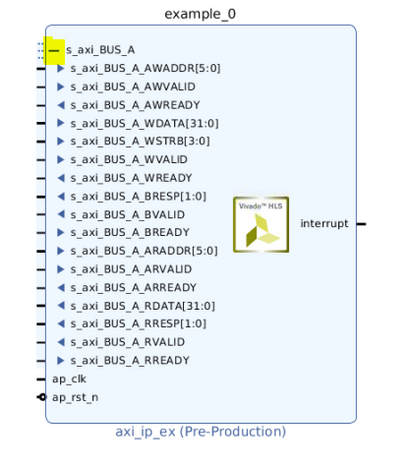

单击 s_axi_BUS_A 旁的 + 按钮即可展开端口。如需获取更多相关信息,请参阅 (PG155 )中的 “端口描述”。

★

02

创建硬件

您可能会想要连接到 PS 以便充分利用其功能。添加 PS IP(如 ZCU106 评估板上提供的 Zynq UltraScale+ MPSoC IP)即可支持您执行此操作。如需获取有关 Zynq UltraScale+ MPSoC IP 的更多信息,请扫码参阅:

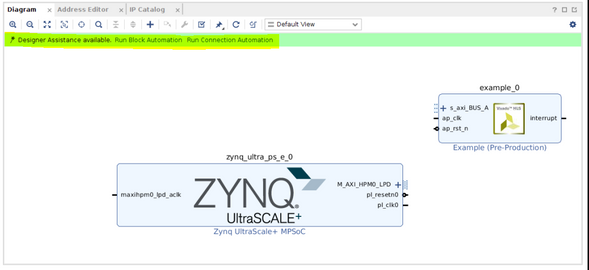

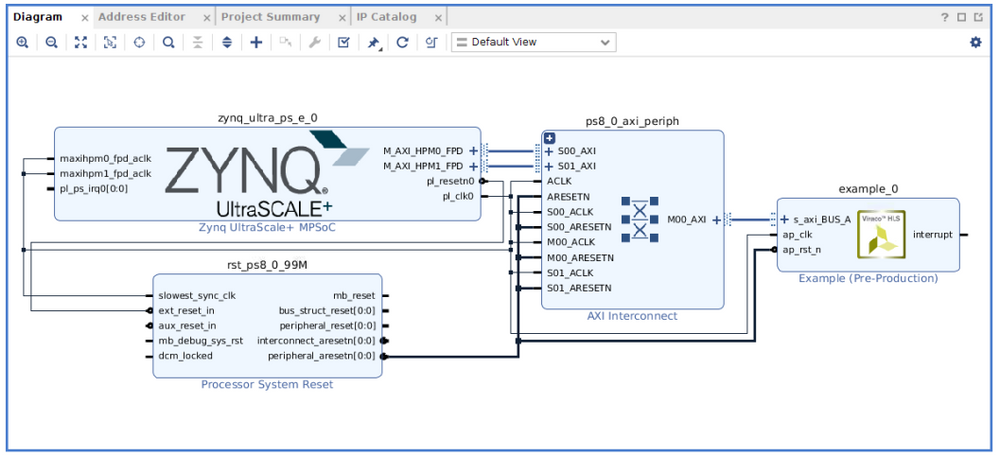

2.1. 将 Zynq UltraScale+ MPSoC IP 添加到模块框图中。添加完成后,将在屏幕顶部出现一条提示信息。选择“运行自动连接功能 (Run Connection Automation)”。

2.2. 这样即可得到如下图示。或者,您可为此 IP 手动添加所有器件,并如该图所示连接这些器件。这样即可得到如下图示:

2.3. 右键单击“源 (Source)”选项卡下的.bd 以创建 HDL 封装器 (wrapper)。运行综合、运行实现,然后生成比特流。下一步,选择“文件 (File) -> 导出 (Export) -> 导出硬件 (Export Hardware)”。请务必选中包含比特流的选项,并记下所选导出位置。这样即可创建包含所有硬件信息的 XSA 文件。现在,您可以关闭 Vivado。

★

03

编写软件

鉴于您的硬件已完成创建并导出,我们需要编写软件以向硬件提供操作指示。我们将在Vitis中编写软件。您将需要从赛灵思网站下载 Vitis Core 开发套件(扫码查阅)。

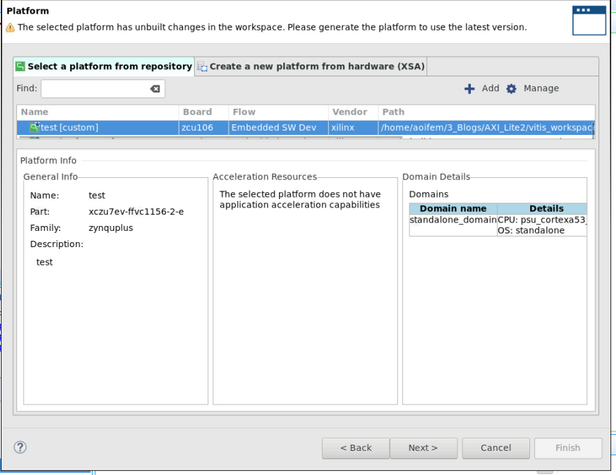

3.1. 打开 Vitis。在打开的菜单中,选择“创建平台工程 (Create Platform Project)”。这将生成工程基本信息,我们将在其中添加硬件信息(XSA 文件)并编写一些软件定义。出现提示时,请选中“从 XSA 文件创建 (create from XSA file)”选项。随后,我们需要选择以上步骤 2.3 中的 XSA 文件导出位置。继续完成其它设置,最后单击“完成 (Finish)”。

3.2. 下一步,我们需要创建包含软件的应用工程。它将基于我们的平台工程,因此其中包含我们的硬件信息,并且我们需要使用该应用工程在目标板上运行应用。选择“文件 (File) -> 新建 (New) -> 新建应用工程 (New Application Project)”。

3.3. 出现提示时,选中“选择存储库中的平台 (Select a platform from arepository)”选项。选择步骤 3.1 中创建的平台工程,然后单击“下一步 (Next)”。

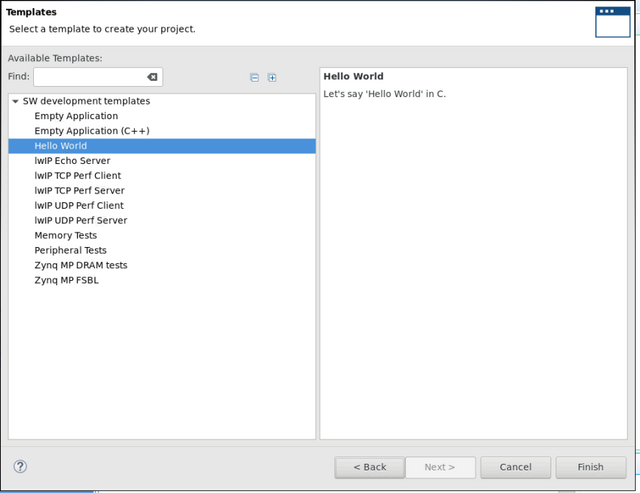

3.4. 选择 Hello World 模板,然后单击“完成 (Finish)”。

3.5. 现在,Hello World 代码会显示在/src/helloworld.c下。为了执行完整性检查,我们将通过 JTAG 把示例下载到板上,并使用 UART 终端查看 printf 信息。

为此,请连接目标板,并打开终端仿真器软件(例如,Tera Term)以读取输出消息。如果您不知晓如何执行此操作,请参阅板相关的用户指南。 编译并运行程序。正确完成此操作后,您应可在 Tera Term 中看到 Hello World 打印信息。

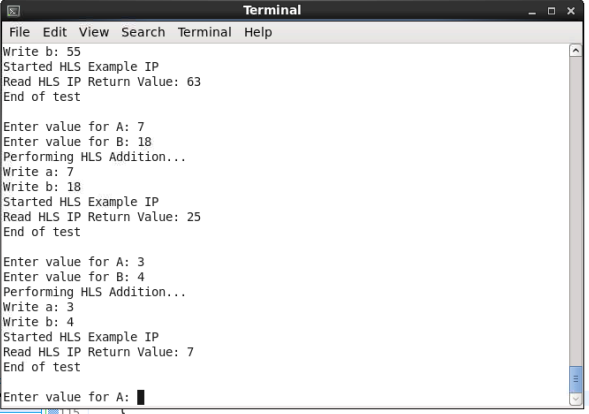

3.6. 现在,确认板已正确连接后,下一步即可创建使用 HLS IP 的代码。从Vitis_Code.c复制代码(随附于本教程)并将其粘贴到 helloworld.c 中,替换原有 helloworld 代码。

保存,然后重新编译并运行软件。这次 Tera Term 会提示您提供 2 项输入:A 和 B,这 2 项将作为输入一并传递给 HLS IP 中,并显示结果。

注:由于在 Vitis HLS 中,A 和 B 已定义为“char”类型,因此输入的值上限为 127。

示例代码使用由 Vitis 自动创建的函数,因此开发非常便捷。

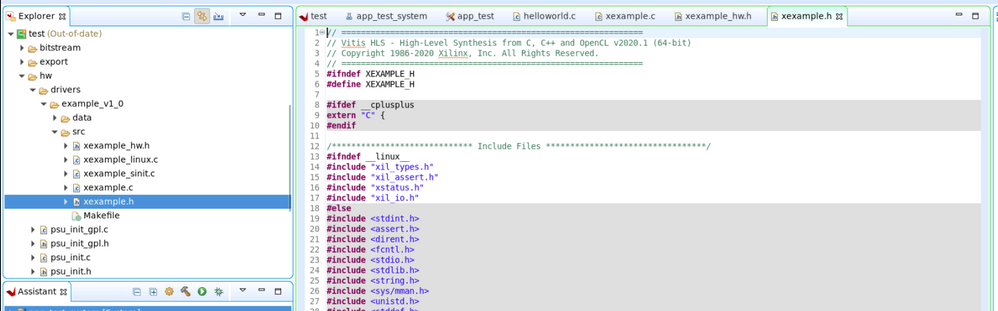

在名为X.h的文件中以及在/hw/drivers//src 下可找到所使用的函数。

如需获取有关这些函数的详细信息,请扫码参阅。请查看此文件以及该文件夹中的其它相关文件。您可通过编辑这些文件来进一步控制自己的 IP 以及执行中断编程等操作。

原文标题:开发者分享 | AXI 基础第 6 讲 - 使用 AXI4-Lite 将 Vitis HLS 创建的 IP 连接到 PS

文章出处:【微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

-

Vivado Design Suite用户指南:逻辑仿真2025-01-15 397

-

Vivado Design Suite教程:动态功能交换2023-09-14 633

-

Vivado Design Suite用户指南:采用IP进行设计2023-09-13 659

-

使用AXI4-Lite将Vitis HLS创建的IP连接到PS2022-08-02 1399

-

如何导出IP以供在Vivado Design Suite中使用?2021-04-26 5842

-

如何使用Vivado Design Suite IP Integrator的调试AXI接口2018-11-29 4701

-

Vivado Design Suite 2016.1的新功能介绍2018-11-20 3318

-

Vivado Design Suite 2014.4.1 现已推出!2017-02-09 535

全部0条评论

快来发表一下你的评论吧 !