如何使用AXI VIP在AXI4(Full)主接口中执行验证和查找错误

接口/总线/驱动

描述

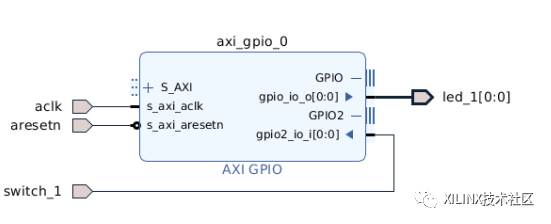

在 AXI 基础第 2 讲 一文中,曾提到赛灵思 Verification IP (AXI VIP) 可用作为 AXI 协议检查工具。在本次第4讲中,我们将来了解下如何使用它在 AXI4 (Full) 主接口中执行验证(和查找错误)。

1. 下载设计文件(请输入以下网址进行下载

https://forums.xilinx.com/xlnx/attachments/xlnx/support_blog/130/1/AXI_Basics_4.zip

2. 打开 Vivado 2019.2。

3. 在 Tcl 控制台中,使用 cd 命令导航到解压缩的目录 (cd AXI_Basics_4)

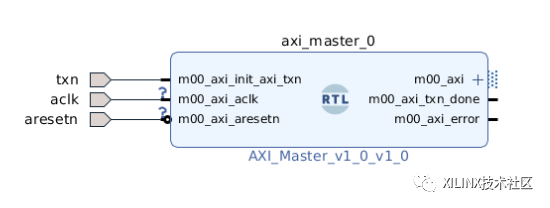

4. 在 Tcl 控制台中,用 source 命令来创建一个 Vivado 工程,其中附带包含自定义 IP 的块设计 (BD),此自定义 IP 具有我们要验证的 AXI4 主接口。

(source./create_proj.tcl)

现在,我们可将 AXI VIP 连接到自定义 IP 的主接口并对其进行验证。

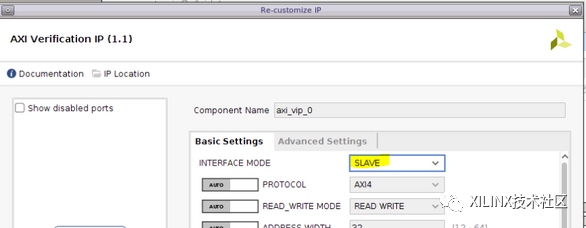

5. 右键单击 BD、单击“添加 IP (Add IP)”,并将 AXI Verification IP (AXI VIP) 添加到 BD 中

6. 双击 AXI VIP 以打开其配置界面

7. 将接口模式更改为“ (Slave)”,然后单击“确定 (OK)”

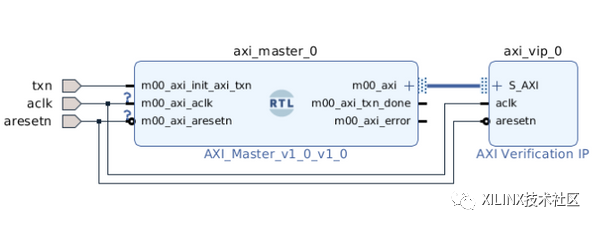

8. 将 AXI VIP 的 S_AXI 输入接口连接到自定义 IP 的 m00_axi 输出接口,并将 AXI VIP 的 aclk 和 aresetn 输入端口连接到 BD 的对应输入端口

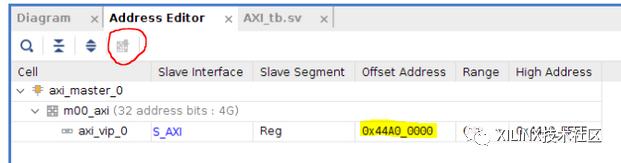

9.打开“地址编辑器 (Address Editor)”选项卡,单击“自动分配地址 (Auto Assign Address)”按钮。确保为 AXI VIP 自动分配的地址为 0x44A0_0000,如果显示其它地址,请手动分配该地址。

10. 验证 BD。确保其中不存在任何严重警告或问题。

11. 保存 BD。

12. 在 Tcl 控制台中输入以下命令,以查找 AXI VIP 实例的全名:

get_ips *vip*

默认情况下,返回的组件名称应为 design_1_axi_vip_0_0

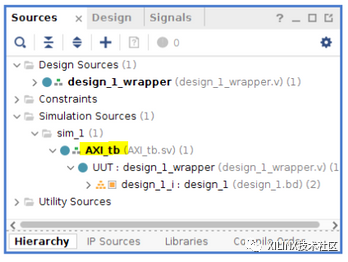

13. 双击“ (Sources)”窗口中的测试平台文件 AXI_tb 以在文本编辑器中将其打开

AXI_tb 测试平台文件已包含运行自定义 IP 所需的代码。我们只需添加 AXI VIP 所需的代码即可。根据 AXI 基础第 3 讲,我们只需遵循来自PG267(v1.1,2019年 10 月 30 日)第 46 页的“实用编码指南与示例”进行操作即可。

首先,导入 2 个必需的包:axi_vip_pkg 和 _pkg。组件名称即步骤 12 中 get_ips 所返回的名称

14. 在第 58 行附近添加以下行

//Import two required packages: axi_vip_pkg and _pkg.

import axi_vip_pkg::*;

import design_1_axi_vip_0_0_pkg::*;

下一步是声明类型为从 VIP 的代理。

15. 在第 91 行附近添加以下行

// Declare the agent

design_1_axi_vip_0_0_slv_mem_t slv_agent;

下一步,我们需要创建从代理。

16. 在第 96 行附近添加以下行

//Create an agent

slv_agent = new("master vip agent",UUT.design_1_i.axi_vip_0.inst.IF);

17. 在本教程中,我们需要使 AXI VIP 在控制台中输出错误,因此我们需要使用以下行(99行附近)启用详细模式

// set print out verbosity level

slv_agent.set_verbosity(400);

18. 最后,使用以下代码行启动从代理:

//Start the agent

slv_agent.start_slave();

19. 保存测试平台文件,启动仿真,运行 200 us

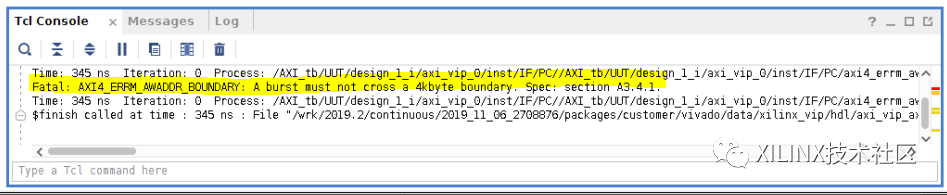

20. 查看 Tcl 控制台,搜索关键字“Fatal”。您应看到以下行:

Fatal: AXI4_ERRM_AWADDR_BOUNDARY: A burst must not cross a 4kbyte boundary. Spec: section A3.4.1.

为理解此错误,我们可以按错误消息中所述查看ARM 网站上提供的 AMBA AXI 和 ACE 协议规范中的第 A3.4.1 小节

在此规范中可以看到如下语句:

“A burst must not cross a 4KB address boundary.”

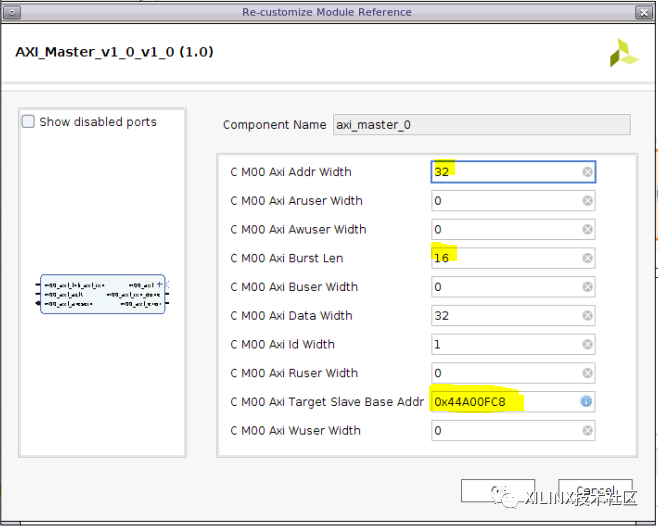

21. 关闭仿真,双击定制 IP axi_master_0 以打开其配置界面。

可以看到,自定义 IP 配置为发送突发 (burst),其中含 16 个 32 位的数据,从地址 0x44A00FC8 开始。这意味着写突发将从地址 0x44A00FC8 开始并于地址 0x44A01004 结束。这是一个错误,因为这些突发会跨越 4k 边界,其地址为 0x44A01000 (4K = 4*1024 = 4096 = 0x1000)。

22. 将 M00 Axi Target Slave Base Address 更改为 0x44A00000,单击“OK”关闭 IP 配置界面,然后保存块设计。

23. 重新运行仿真并持续 200 us。

24. 重新搜索关键字“Fatal”。可以看到,错误消息已改变(这表明第一个问题已解决)。您应看到如下错误:

Fatal: AXI4_ERRM_WDATA_STABLE: WDATA must remain stable when WVALID is asserted and WREADY low. Spec: section A3.2.1.

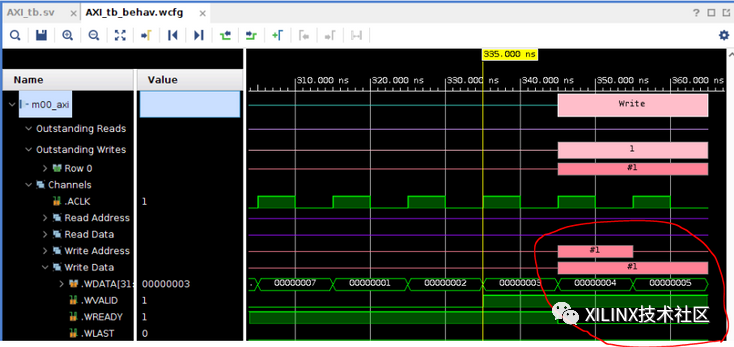

25. 在波形窗口中,展开 m00_axi 接口的写数据通道。您将看到 wvalid 确实正在发生改变,而 tready 为低,这有违 AXI 规范。

26. 关闭仿真,在“Sources”窗口中打开位于BD下的 AXI_Master_v1_0_M00_AXI.v 文件

27. 修改 506/518行附近的如下段落。这样当 tready 为低时就会阻止 wdata 发生更改。

/* Write Data Generator

Data pattern is only a simple incrementing count from 0 for each burst */

always @(posedge M_AXI_ACLK)

begin

if (M_AXI_ARESETN == 0 || init_txn_pulse == 1'b1)

axi_wdata <= 'b1;

//else if (wnext && axi_wlast)

// axi_wdata <= 'b0;

else if (wnext)

axi_wdata <= axi_wdata + 1;

else

axi_wdata <= axi_wdata;

end

28. 保存此文件。这样应可显示“刷新已更改的模块 (Refresh Changed Modules)”选项。单击该选项。

29. 重新运行仿真并持续 200 us。

在新仿真运行中应该不会再出现任何新错误,如果您查看波形窗口,应看到正常发生的 16 次写入和 16 次读取的突发传输事务。也就是说第二个问题已经得到修复。

往期精选

第二讲 使用 AXI Verification IP (AXI VIP) 对 AXI 接口进行仿真

第三讲 使用AXI VIP 对 AXI4-Lite 主 (Master) 接口进行仿真

审核编辑:汤梓红

-

使用AXI4接口IP核进行DDR读写测试2025-11-24 3333

-

AXI VIP设计示例 AXI接口传输分析2022-07-08 2969

-

NVMe IP之AXI4总线分析2025-06-02 6041

-

如何使用Xilinx AXI VIP对自己的设计搭建仿真验证环境的方法2022-10-09 5016

-

AMBA 4 AXI4、AXI4-Lite和AXI4-流协议断言用户指南2023-08-10 610

-

AXI4接口协议的基础知识2020-09-23 6914

-

一文详解ZYNQ中的DMA与AXI4总线2020-09-24 7155

-

ZYNQ中DMA与AXI4总线2020-11-02 5008

-

AXI4 、 AXI4-Lite 、AXI4-Stream接口2022-07-04 10479

-

AXI3与AXI4写响应的依赖区别2023-03-30 1809

-

FPGA AXI4协议学习笔记(二)2023-05-24 2743

-

Xilinx FPGA AXI4总线(一)介绍【AXI4】【AXI4-Lite】【AXI-Stream】2023-06-21 3069

-

FPGA通过AXI总线读写DDR3实现方式2024-04-18 2474

-

Xilinx NVMe AXI4主机控制器,AXI4接口高性能版本介绍2024-07-18 1422

-

AMBA AXI4接口协议概述2024-10-28 1366

全部0条评论

快来发表一下你的评论吧 !