HBM的基本情况

描述

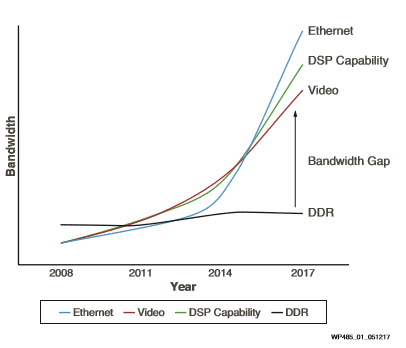

HBM(High Bandwidth Memory,高带宽存储)已成为现代高端FPGA的一个重要标志和组成部分,尤其是在对带宽要求越来越高的现如今,DDR已经完全跟不上节奏。本篇将分享学习一下HBM的基本情况。

什么是HBM

高带宽存储(HBM)是三星、AMD和SK Hynix推出的基于3D堆叠同步动态随机存取存储器(SDRAM)的高速计算机内存接口。它使用在高性能图形加速器、网络设备、高性能数据中心AI ASIC和FPGA以及一些超级计算机中。(如NEC SX-Aurora TSUBASA和富士通A64FX) 第一款HBM芯片是由SK Hynix在2013年生产的,而2015年AMD首次研发了使用这种技术的GPU芯片。

2013年10月,JEDEC(电子器件工程联合会)采用高带宽内存作为行业标准。第二代HBM2,于2016年1月被JEDEC所承认。

HBM memory on an AMD Radeon R9 Nano graphics card‘s GPU package

HBM及其接口

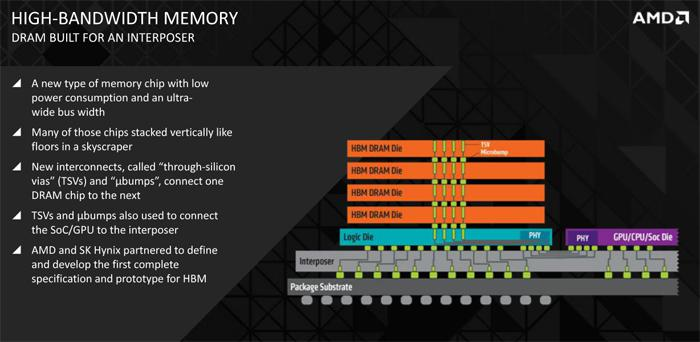

HBM以比DDR4或GDDR5功耗更低,带宽更高。这是通过堆叠8个DRAM die(3D集成电路)来实现的,包括可选的基die(通常是硅interposer)和memory控制器,该控制器通过硅通孔(TSV)和微突点(microbump)相互连接。HBM技术与Micron的Hyrid Memory Cube技术在原理上相似,但不是一回事。

与其他DRAM内存(如DDR4或GDDR5)相比,HBM内存总线非常宽。一个HBM stack由4个DRAM die(4-Hi)堆叠而成,并拥有8个128位信道(每个die上2个),总宽度为1024位。因此,具有四个4-Hi HBM stack的GPU将拥有4096位宽度的内存总线。相比之下,GDDR存储器的总线宽度为32位,同样16个信道则只具有512位存储器接口。HBM支持每个package的容量最多为4GB。

HBM DRAM与具有分布式接口的主计算die进行紧密耦合。该接口被分为若干完全独立的信道但信道间不一定完全同步。HBM DRAM使用wide-interface架构来实现高速、低功耗运算。HBM DRAM使用一个500MHz的差分时钟CK_t/CK_c(其中后缀“_t”表示差分对的“真”或“正”分量,“_c”代表“互补”分量)。命令在CK_t,CK_c的上升沿进行寄存。每个信道接口管理一个128位的数据总线,以双倍数据速率(DDR)运行。HBM支持每个pin上1GT/s的传输速率(传输1bit),提供128GB/s的总package带宽。

HBM2

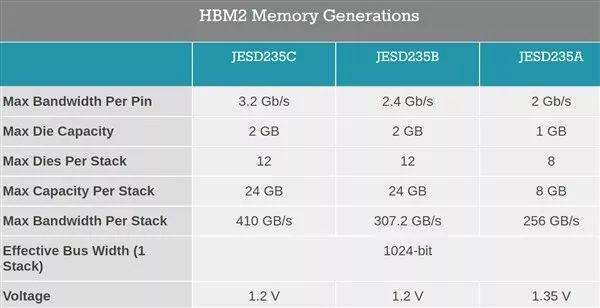

第二代高带宽存储,HBM2,该标准指定了每个stack多达8个die,将pin传输速率提高一倍来到2GT/s。保留1024位宽的存取,HBM2能够达到每个package 256GB/s存储带宽。HBM2规范允许每个package容量高达8GB。HBM2对性能敏感的消费类应用,如虚拟现实,特别有吸引力。

HBM2 die

HBM2 Controller die

HBM2 规范演进

HBM2E

2018年底,JEDEC宣布了对HBM2规范的更新,增加了带宽和容量。官方规范现在支持每堆栈高达307GB/s(2.5Tbit/s有效数据速率),尽管以此速度运行的产品已经问世。此外,该更新还增加了对12-Hi stack(12个die)的支持,使每个堆栈的容量高达24GB。2019年3月20日,三星宣布了他们的Flashbolt HBM2E,每stack 8个die,传输率为3.2GT/s,每stack可提供410GB/s带宽。2019年8月12日,SK Hynix发布了他们的HBM2E,每stack8个die,传输速率为3.6GT/s,每stack可提供460GB/s带宽。

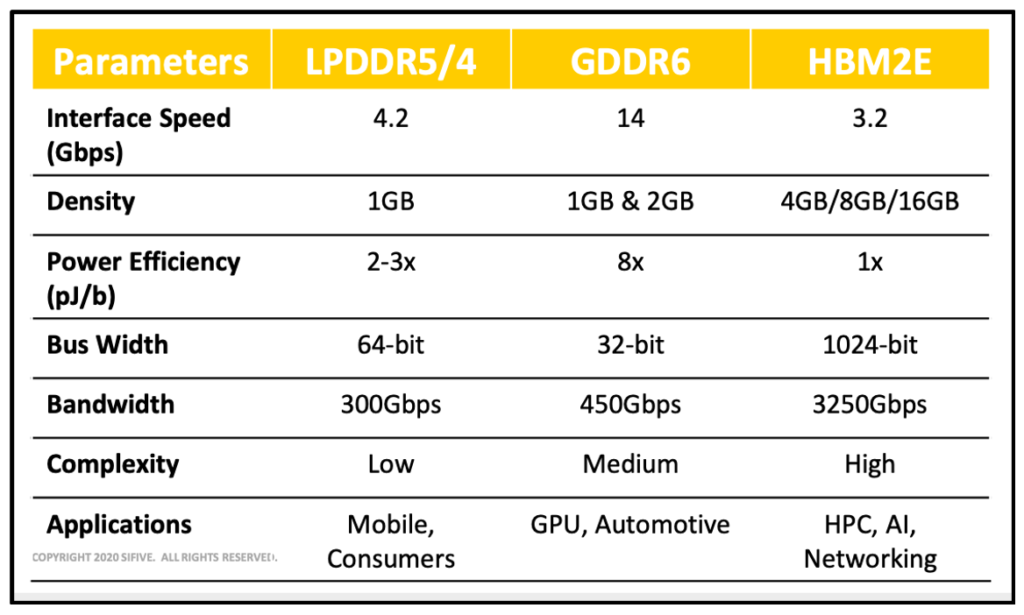

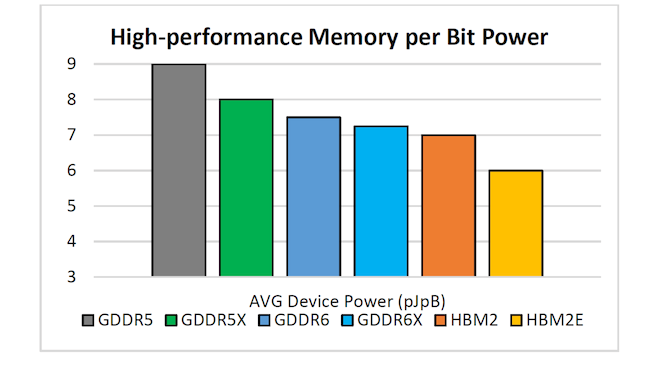

HBM2E 和LPDDR5/4以及GDDR6对比

各类型存储的平均器件功耗

下一代HBM

2020年底,Micron公司发布了下一代标准HBMnext并表示将全程参与JEDEC的标准制定工作,预计2022年面世。这个未来很有可能是HBM3的标准很可能还是服务于数据中心。

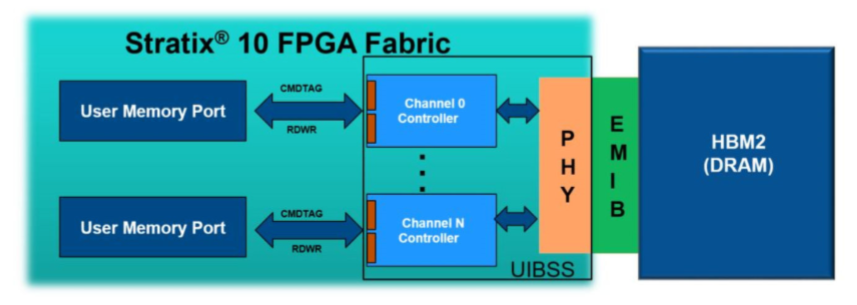

Intel在其Stratix10 MX上集成了HBM2接口。

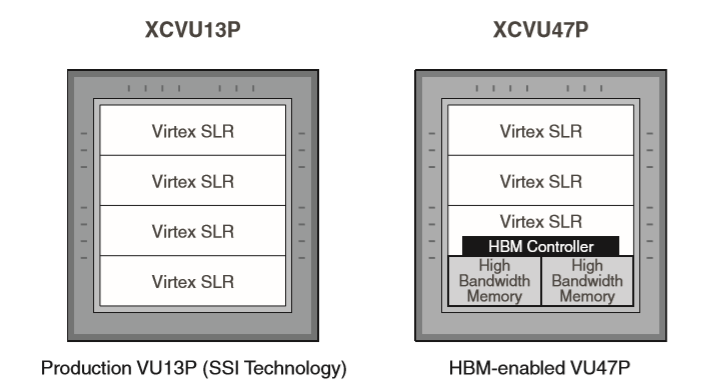

Xilinx则是将HBM集成到了其Ultrascale+器件中。

近年来,FPGA厂商对HBM的态度甚至比GPU厂商还要积极,随着数据中心上越来越高的性能要求,相信带有HBM3的FPGA也会在不远的未来和大家见面。

原文标题:现代高端FPGA的重要拼图:HBM

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

-

美光发布HBM4与HBM4E项目新进展2024-12-23 1751

-

HBM4到来前夕,HBM热出现两极分化2024-09-23 4099

-

HBM、HBM2、HBM3和HBM3e技术对比2024-03-01 7122

-

如何加速HBM仿真迭代优化?2023-11-29 2090

-

[1.1.1]--小程序的基本情况jf_75936199 2023-02-23

-

ChatGPT带旺HBM存储2023-02-15 6559

-

CNN结构基本情况2022-07-05 3224

-

介绍一下关于74LS系列芯片的一个基本情况2021-07-22 3874

-

从2020年4季度看整车和电池的基本情况2021-01-26 2169

-

2020年车市的基本情况概览2021-01-18 2677

-

HBM产品在电机测试中的使用情况2020-10-31 3609

-

HBM传感器的安装2020-06-19 3175

-

HBM称重传感器的运用知识2018-11-02 2444

-

追求性能提升 使用8GB HBM2显存2016-12-07 4382

全部0条评论

快来发表一下你的评论吧 !