i.MXRT1170 的时钟架构

接口/时钟/PLL

描述

如果我们从一颗 MCU 芯片的引脚分类来看芯片功能,大概可以分为三大类:电源、时钟、外设功能。

作为嵌入式开发者,大部分时候关注的都是外设功能引脚,而对于时钟相关引脚往往不太在意,其实有些时候利用时钟功能引脚也能助你定位问题。

今天就带你梳理一下 i.MX RT1xxx 系列的时钟系统以及相关功能引脚:

一、时钟系统简介

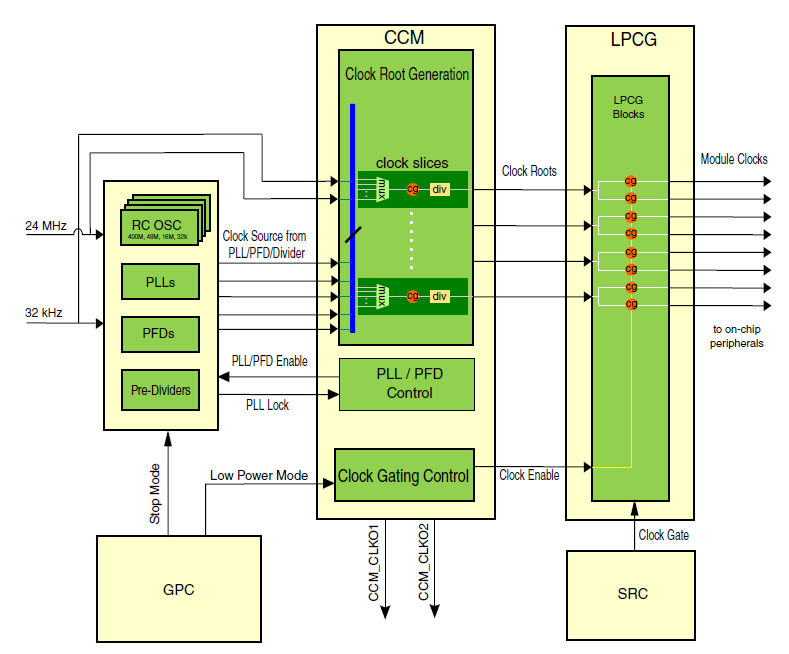

目前 i.MXRT1xxx 系列主要分为 i.MX RT10xx 和 i.MXRT11xx 两大分支。这两个分支的时钟系统设计是有一些差异的,不过总体来说,架构差别不大,我们以如下 i.MXRT1170 的时钟架构为例来具体介绍。

在时钟系统架构图里,我们能看到有五大组件:OSC_PLL、CCM、LPCG、GPC、SRC,其中最核心的功能在前两个,OSC_PLL 主要负责产生时钟,CCM 主要用于分配时钟。

二、关于时钟源头

上一节里我们知道 OSC_PLL 模块负责所有时钟的生成,但那些时钟并不是凭空产生的,也是需要源头的。这个源头既可以来自芯片内部,也可以来自外部引脚输入。

先说芯片内部的 RC OSC,在芯片设计时,为了保证在没有外部时钟/晶振输入的情况下,芯片也能工作,所以内部集成了一些振荡器/振荡电路(RC Oscillator),32KHz 和 24MHz(48MHz) 是标配,部分型号上还有 16MHz、400MHz,不过这些内部振荡器精度有限(有可能误差20%),适合芯片低速运行场合。

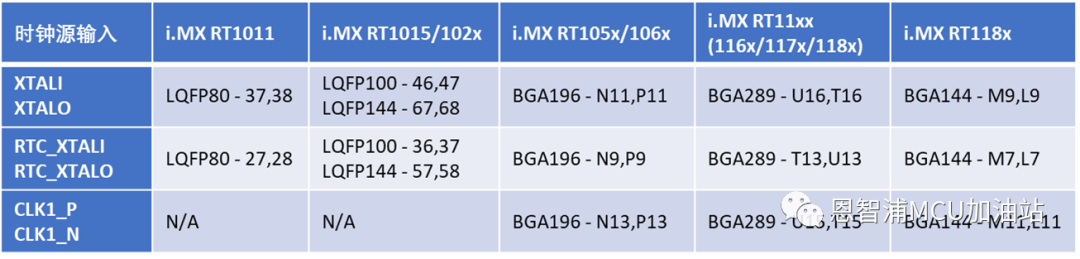

如果是芯片高速运行的场合(或者对精度要求高的场合),那一定需要外接高精度振荡器,包含从 XTALI/XTALO 引脚进来的 24MHz OSC,以及从 RTC_XTALI/RTC_XTALO 引脚进来的 32.768KHz OSC,这两个外部时钟源是由 OSC_PLL 大模块内部的 XTALOSC 小模块负责管理的,XTALOSC 模块优先检测外部是否有 32.768KHz / 24MHz OSC 存在,如果存在则用外部源,如果不存在则启用内部 32KHz / 24MHz RC OSC 源。

24MHzOSC(内部或者外部源)是 OSC_PLL 内部 PLL 的主要时钟源,有了基准的 24MHz 时钟,PLL 就能将其倍频得到想要的高频时钟,芯片内部 PLL 有很多个,大部分 PLL 都只是输出固定原始频率时钟,少部分含 PFD 功能的 PLL(一般是 System PLL)可以调节原始频率输出。除了 24MHz OSC 外,PLL 也可以接受来自 CLK1_P/CLK1_N 引脚输入的源。

对于 i.MXRT10xx 系列,PLL时钟源选择在CCM_ANALOG-》PLL_xxx[BYPASS_CLK_SRC] 位

对于 i.MXRT11xx 系列,PLL时钟源由Set Point 设置

三、关于时钟输出

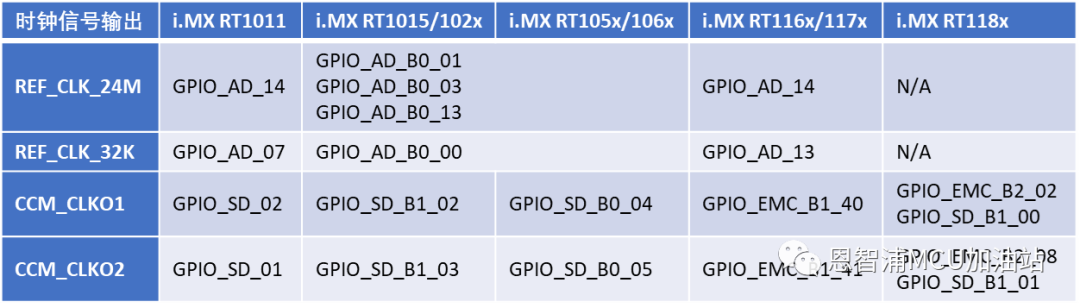

前面讲了32KHz / 24MHz OSC 是比较重要的时钟源头,它的精度对系统性能有很大影响,因此我们需要有一种方法实测这两个时钟的精度,芯片设计时特意在一些 I/O 引脚复用功能里做了 REF_CLK_24M / REF_CLK_32K 选项,当 I/O 配置为该功能时,便可用示波器量得具体时钟频率。

我们知道CCM 模块负责 OSC_PLL 输出的时钟资源的分配,芯片里所有外设的具体时钟源指定以及分频系数、开关控制均由 CCM 来完成。如果你想观测某 PLL 最终输出或者常用外设时钟源最终配置,也可以通过指定 I/O 输出观测,即下面的 CCM_CLKO1 / CCM_CLKO2 复用功能选项。当然 CCM_CLKOx 不仅仅用于观测频率,也可以用于给外部芯片提供时钟源。

对于 i.MXRT10xx 系列,CCM_CLKOx时钟输出控制在CCM-》CCOSR 寄存器

对于 i.MXRT11xx 系列,CCM_CLKOx时钟输出控制在最后两个CCM-》CLOCK_ROOT_CONTROL 寄存器

总结一下,时钟功能引脚尤其是输出引脚对于确认时钟频率具有重要意义,如果你的应用严重依赖时钟精度,遇到问题时不妨先检查一下时钟频率的准确性以及精度。

至此,i.MXRT1xxx系列MCU时钟相关功能引脚作用痞子衡便介绍完毕了,掌声在哪里~~~

原文标题:浅谈i.MX RT系列MCU时钟相关功能引脚的作用

文章出处:【微信公众号:MCU开发加油站】欢迎添加关注!文章转载请注明出处。

-

i.MX RT1xxx 系列的时钟系统以及相关功能引脚2022-07-08 1235

-

MCU时钟相关功能引脚操作2022-09-28 4282

-

介绍一下i.MXRT1170上用于保护片内OCRAM1,2的MECC64功能2023-12-29 2371

-

i.MXRT1170的相关资料分享2021-11-04 1043

-

i.MXRT1170 eFuse空间访问可靠性的保护策略是什么2021-12-20 1105

-

求助,如何在没有互联网的情况下通过以太网电缆将一个简单的十六进制数从I.MXRT1170板发送到PC?2023-03-17 458

-

s32k144evb如何与i.MXRT通信?2023-03-29 662

-

如何确保 i.MXRT1176 从低功耗模式快速恢复?2023-04-06 588

-

浅谈数字总线的时钟架构2017-01-17 808

-

WEBENCH® 时钟架构如何获取完整、优化的时钟树解决方案?2018-08-02 4685

-

新UltraScale ASIC时钟架构的使用及好处2018-11-29 4429

-

痞子衡嵌入式:终于可以放开聊一聊i.MXRT1170这颗划时代MCU了2021-10-29 695

-

MCU时钟相关功能引脚作用介绍2022-07-07 6984

-

在i.MXRT1060和RT1170上使用高效神经网络进行多人检测2023-08-17 527

-

不同J-Link版本对于i.MXRT1170连接复位后处理行为2024-08-08 1772

全部0条评论

快来发表一下你的评论吧 !