SmartSiC的制作步骤及技术细节

描述

前段时间,Soitec宣布8英寸SiC量产,而且还投资23亿建线(。点这里。),更为关键的是他们号称能让单块SiC晶锭产量增加10倍,使SiC MOSFET芯片尺寸缩小5-15%。

很多人都很好奇Soitec的技术细节,最近,“行家说三代半”拿到了他们的技术文献,今天就给大家分享一下。

插播:7月7日,欣锐科技、英飞凌、Wolfspeed、三菱电机、芯干线、百识电子和恒普科技等企业“大咖”,将参与“新能源趋势下第三代半导体产业化发展论坛”,发布最新技术报告,报名点文末“阅读原文”。

SiC功率器件已成为广泛应用的突破性技术,风靡汽车牵引逆变器、DC/DC转换器、车载充电器或充电站等领域。

但是目前,4H-SiC材料质量和供应限制了碳化硅在汽车等领域的爆发,因为这些领域对碳化硅衬底的质量要求非常高,而目前业界还很难提供近乎无缺陷的衬底晶圆。

Soite认为,他们通过Smart Cut技术,制造的SmartSiC衬底,具有非常高的质量,能够优化器件良率。

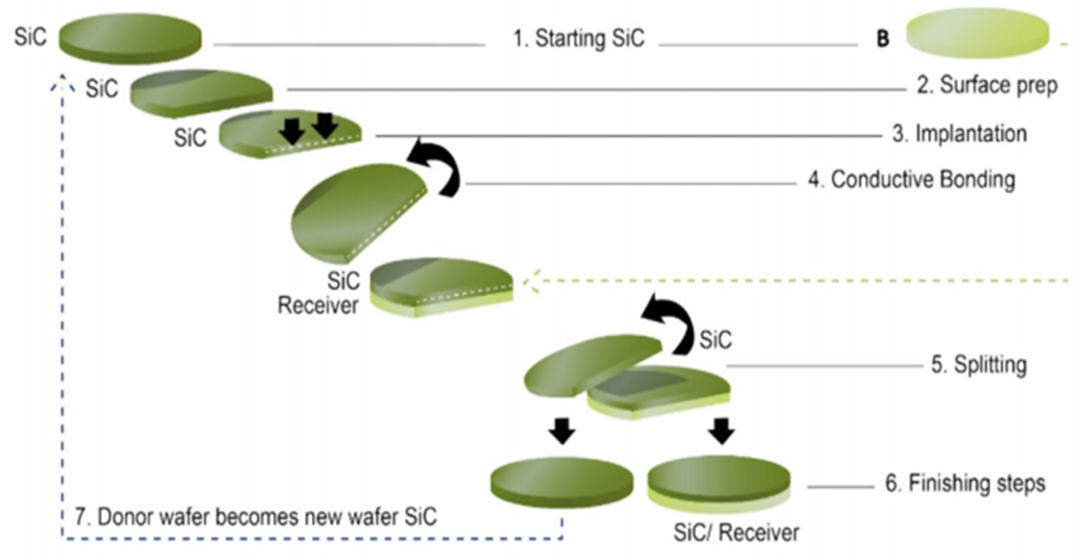

SmartSiC的制作步骤如下,这种方式的好处可以参考之前的报道:

图1:SmartSiC 衬底制造工艺

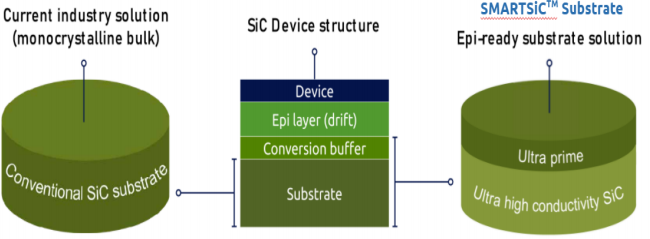

SmartSiC衬底概念图如下:

图2: SmartSiC衬底

目前,Soitec已经展示了SmartSiC开发样品,并可用于器件评估。

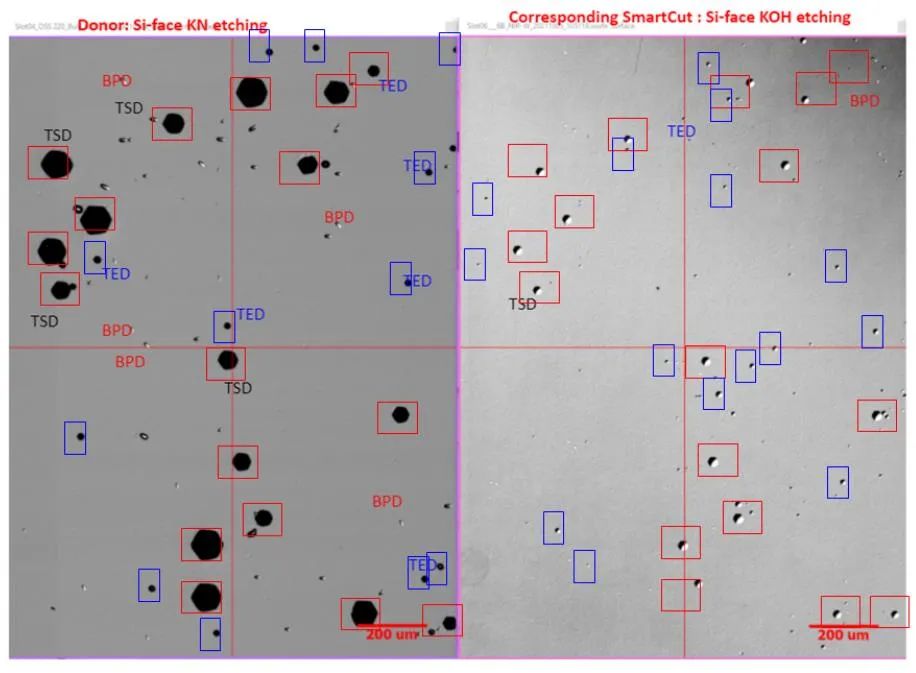

4H-SiC 衬底(左)和 SmartSiC衬底(右)

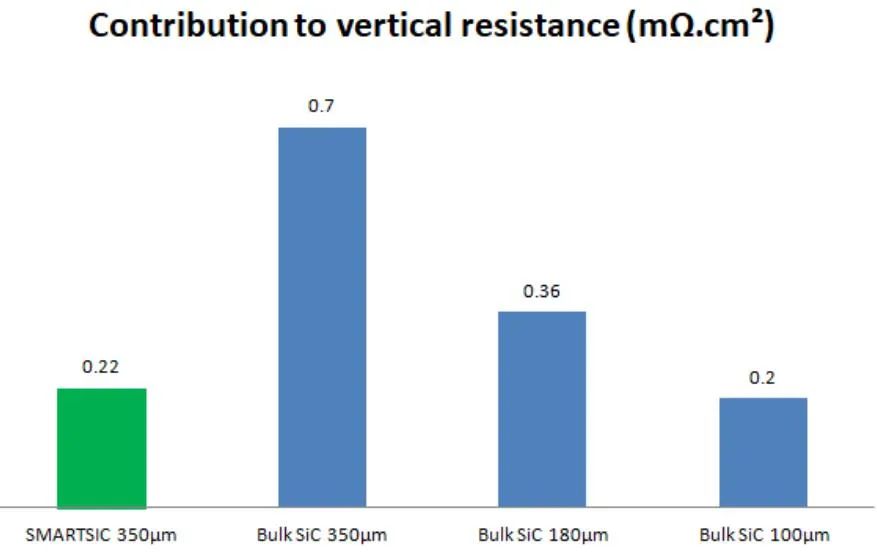

根据文献,Soitec通过多晶SiC衬底的开发,制作了电阻率低至 5mΩ.cm或更小的碳化硅晶片。从整个堆栈来看,对应的垂直电阻为0.22mΩ.cm2(或更小)。

350μm的SmartSiC电阻率与100µm的 4H SiC相当,比常规180µm的碳化硅衬底的电阻率降低了35%。

此外,多晶SiC衬底的另一个好处是能够提高材料的机械性能,从而使磨削下的变形可以忽略不计。与Bulk SiC 参考相比,优化的多晶SiC磨削至180µm变形得到改善。

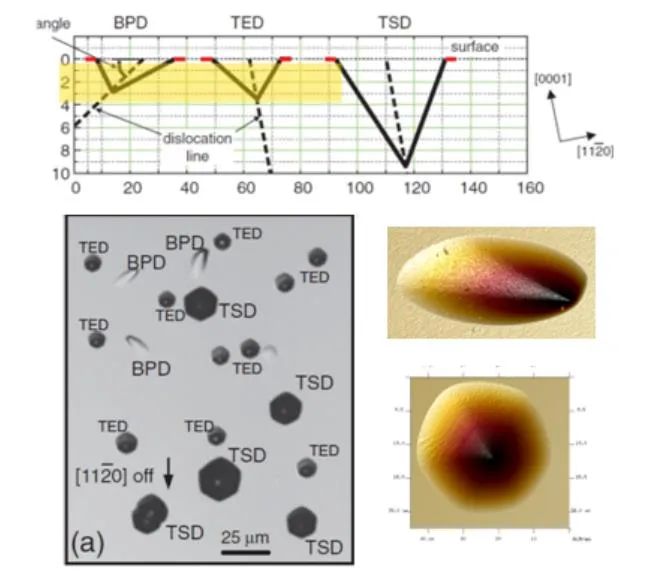

同时,Soitec还证明了SmartSiC衬底比供体晶圆更低的晶体缺陷率。

显微镜和 AFM 图像显示,SmartSiC的 TED、TSD 和 BPB都得到了明显的优化。

通过对比可以发现,Smart Cut 不会引入新的晶体缺陷。

为此,该公司认为,他们的SmartSiC在功率器件应用方面具有巨大潜力,不仅可以提高性能,而且可以提高可制造性。

原文标题:电阻率降低35%!Soitec公布碳化硅技术细节

文章出处:【微信公众号:第三代半导体风向】欢迎添加关注!文章转载请注明出处。

-

低功耗蓝牙的技术细节2018-12-22 2896

-

应用Bluetooth Smart技术的全套智能骑行设备的技术细节和应用场景,不看肯定后悔2021-05-21 1868

-

ARM公司公开下一代ARM架构技术细节2011-11-03 1808

-

英特尔揭露Ivy Bridge技术细节,将包含至少四个版本2012-02-23 1309

-

MIT公布“盲动”机器人技术细节2018-07-11 3541

-

意法半导体公布ST54J系统芯片(SoC)的技术细节2018-10-10 7936

-

要想电流测得准,一定不能忽视的技术细节(第二讲)2019-07-02 3805

-

小米手表e-SIM技术细节揭露,明天发布2019-11-04 5923

-

一文解析鸿蒙系统诞生背景、技术细节生态圈2021-06-11 8430

-

聊聊50G PON的技术细节2024-04-30 223

-

深入解析Zephyr RTOS的技术细节2024-10-22 4761

-

索尼IP编码板:技术细节与应用探索2025-03-20 1247

-

揭秘徐工新能源重卡的技术细节2025-08-11 1398

-

PCIe 7.0技术细节曝光2025-09-08 3132

-

有哪些具体的技术细节需要企业在选择电能质量在线监测装置数据存储方式时注意?2025-10-30 405

全部0条评论

快来发表一下你的评论吧 !