旁路电容与去耦电容的定义与比较

描述

射频电路工作频率高,与数字、模拟电路相比,射频电路非理想特性众多,寄生效应复杂。实际应用中,需要对射频信号串扰、不同器件间隔离等做良好处理,稍有不慎,便会出现干扰、震荡等问题。在射频电路的测试中,实测结果与仿真结果不一致是家常便饭,实测被仿真完美预测的情况寥寥无几。

“旁路(Bypass)”与“去耦(Decoupling)”处理不好是造成射频实测异常的重要原因之一。虽然对于这两个问题在设计时有一些经验可循,但如果对问题成因理解不深,很有可能造成问题无法本质解决,严重时还会引起其他更严重的后果。

而且“Bypass”和“Decoupling”很多时候结构类似,很多人也将“Bypass电容”与“Decoupling电容”用做同义词,不过二者的使用目的和设计考虑是不同的。

本文尝试对“Bypass”和“Decoupling”的概念做一个讨论,理解二者设计的基本理念,同时给出二者设计时注意的要点。

一、Bypass”与"Decoupling"的定义

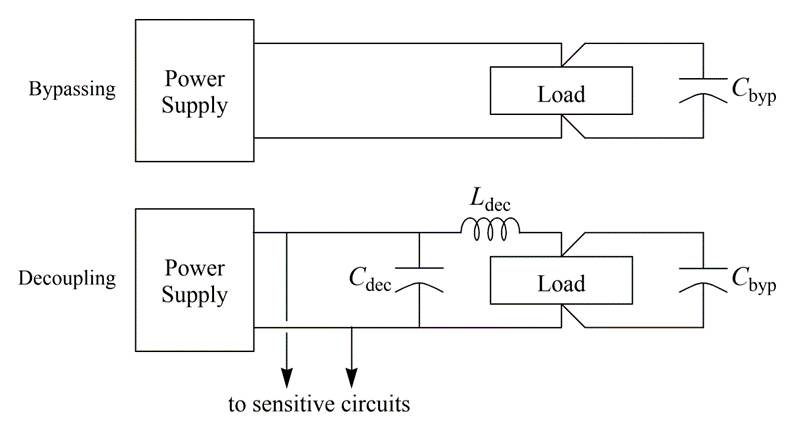

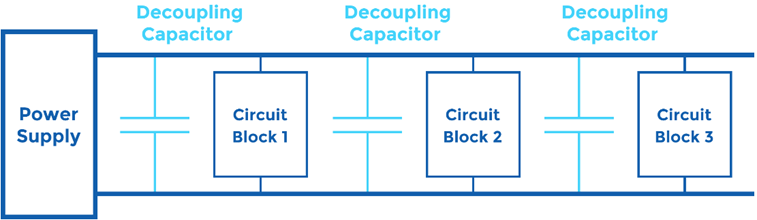

图:Bypass与Decoupling

Bypass

Bypass(旁路)是指为射频信号提供一个低阻通路(通常使用电容,如上图中的 ),使射频信号沿此低阻通路流动,减少射频信号向其他高阻路径的流动。

),使射频信号沿此低阻通路流动,减少射频信号向其他高阻路径的流动。

Decoupling

目的是将共用连接线上的不同电路做隔离,一般由低通网络构成。隔离的目标是不让电路间的噪声互相传播干扰。在上图中Decoupling电路设计中,Bypass电容 和Decoupling电路

和Decoupling电路 、

、

共同完成Decoupling,这种设计方法在射频电路实现中经常使用。 以下将对Bypass和Decoupling电路做详细讨论。

二、Bypass电路

理想情况下,电压源提供低阻阻抗,但实际应用并非如此。电压源的阻抗随着频率的升高而升高;另外由于电源走线的寄生电感效应,以及电源上连接其他器件的寄生效应,射频芯片端口的射频阻抗已经不再保证是低阻,这个时候,就需要用Bypass电容来提供低阻路径。

图:射频芯片应用中,需要片外Bypass电容提供低阻路径

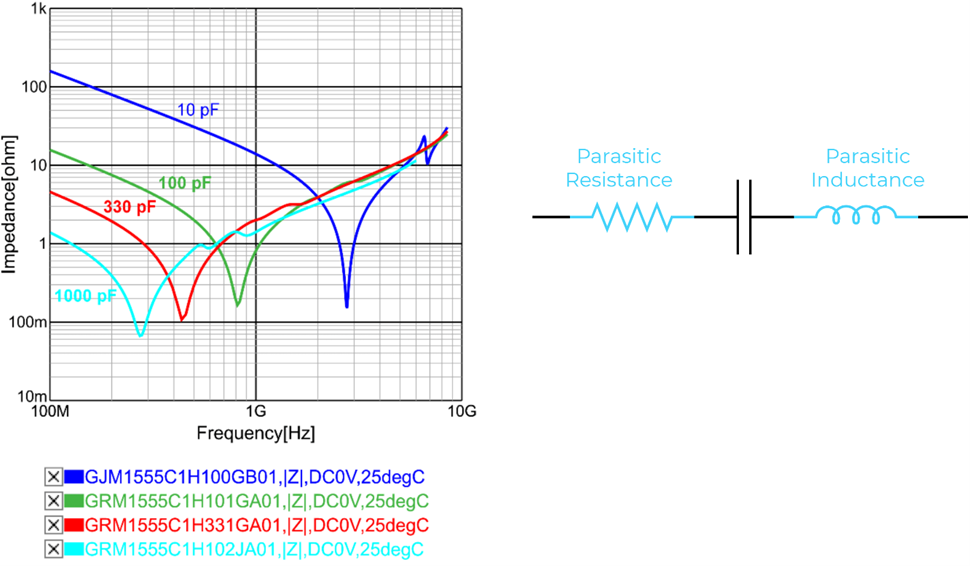

在Bypass电容设计中,需要注意的是,由于寄生电感的存在电容无法在全频段内保持低阻。随着频率升高,寄生电感与电容谐振,超过谐振频率之后,电容表现为感性,频率继续升高阻抗增大。

一般MLCC电容寄生电感为0.3nH,可以以此来计算不同容值电容的谐振频率。下图为Murata不同容值电容串联阻抗的测试值[1],可以看到,1000pF电容低阻区域(<3 Ohm)在1GHz以下,而10pF所覆盖的范围在2~3.5GHz附近。

图:MLCC阻抗随频率的变化及其等效电路

为了使全频段得到较低的阻抗,需要并联多个电容,容值从小到大排列。在4G/5G PA设计和应用中,一般采用100pF、100nF及1uF的Bypass电容,分别覆盖GHz、几十MHz及十MHz以下频率。其中第一个100pF量级电容大多在芯片内部实现,100nF及1uF级别电容需要在芯片外部实现。下图为慧智微5G L-PAMiF产品S55255-12应用手册中的Vcc Bypass电容设计建议[2],片外建议就近放置100nF及1uF两颗Bypass电容。

图:慧智微5G L-PAMiF S55255-12产品Bypass电容应用建议

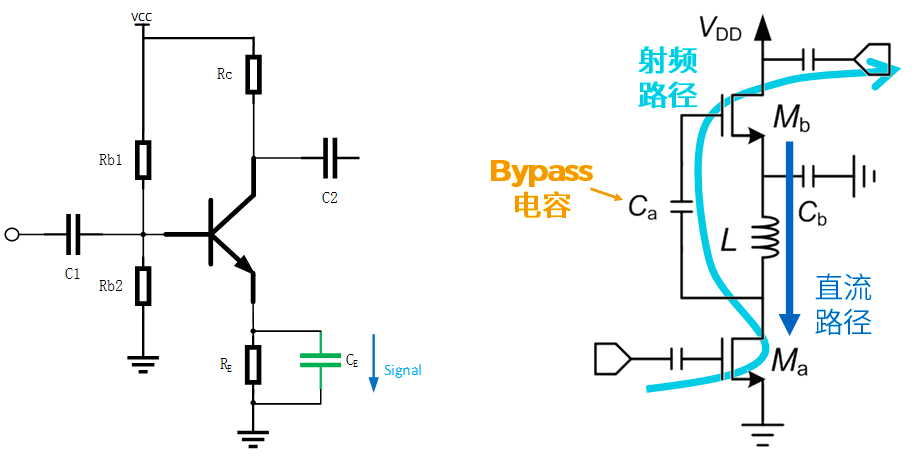

除了在电源提供低阻路径外,Bypass电容还可以在其他射频通路提供低阻路径。例如下图分别为在发射极提供射频旁路路径,减少发射极负反馈电阻 对射频增益的影响;以及利用电容Bypass特性,将直流路径与射频路径分开,在一路直流供电的Casecode连接叠管中,实现两级共源放大器[3]。

对射频增益的影响;以及利用电容Bypass特性,将直流路径与射频路径分开,在一路直流供电的Casecode连接叠管中,实现两级共源放大器[3]。

图:射极电阻Bypass及采用Bypass电容电流复用放大器

三、Decoupling电路

如果需要将不同的电路模块做隔离,防止他们之间的相互干扰,那么最好的方法是减少电路模块之间的线路的共用。不过,这通常在设计中是不现实的。不仅如此,在一些复杂电路设计中,甚至一些共用走线时的准则,如“电源要星型走线”等也无法实施,这时,就要设计好Decoupling电路,完成各电路模块间的Decoupling。下图为Decoupling电路在系统中的框图。

图:Decoupling电路在系统中的位置

典型的电源/射频Decoupling电路[4]如下图所示。在电路中,串联通路上采用了串联电感使串联通路在高频时表现出高阻,这可以帮助Bypass电容发挥旁路特性,确保高频噪声可以充分的旁路到地。其次,电路传输特性表现为低通特性,这样流经网络时高频电流将被抑制,只有低频电流可以流过,保持了供电的稳定。

图:典型Decoupling电路中的电流路径

如果说Bypass电路提供的低阻通路是为自身电路服务,那Decoupling电路就是为整体系统设计的去耦网络,需要将整个系统联合考虑。在Decoupling电路设计中,核心是要找到耦合线路以及信号环路,并采用有效的措施切断耦合线路,最小化信号的干扰环路。

在Decoupling电路设计中,有以下要点需要注意:

定位干扰源,并识别耦合环路。如果存在多个环路,则每个环路都需要做Decoupling处理。例如有些电路需要正压、负压及数字电路控制,在这些pin脚连接上都需要做去耦处理。

在Layout时,将Decoupling电路尽量靠近干扰源放置,以防止过长走线时走线上产生互感效应。例如芯片电源、数字控制端口的Decoupling电路应该靠近芯片端口就近放置。

Decoupling电路必要的时候需要加入损耗型元件,如电阻等。

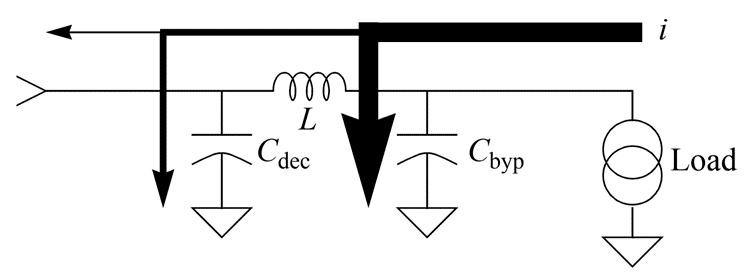

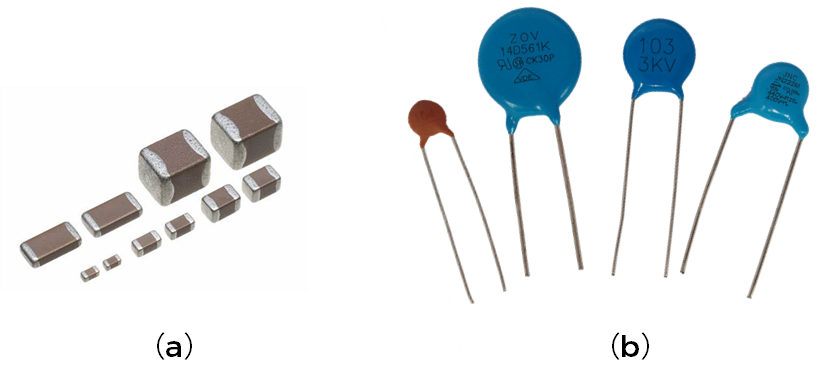

Decoupling电路中所使用的器件在关心的频率有良好的射频特性,例如Bypass电容必须在所关心的频率呈现低阻(如Bypass章节分析),串联电感要注意其谐振频率。一般Decoupling电路使用的是贴片陶瓷电容,而不用长引出脚的陶瓷电容、电解电容。如下图所示。

图:(a)适合做高频Decoupling的贴片电容;(b)不适合做高频Decoupling的长引出脚电容

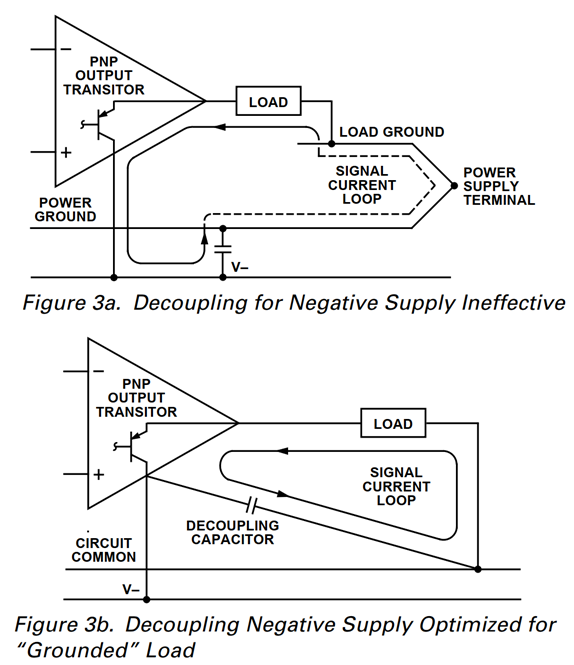

在Decoupling电路设计中,需要特别注意的是Decoupling电路接地点的选取。一定要识别并选取有效的Decoupling节点。下图针对高速运算放大器展示了两种负电源V-的Decoupling的设计方式[5]。

在第一种Decoupling中,选取节点在V-电源的某个位置中,这样选择之后,高频信号环路需要经过V-电源以及较长的地线才连接到Decoupling电容,电源及地线上接收到了大量的高频干扰,不是有效Decoupling。

第二种Decoupling中,将Decoupling电容直接跨接在在芯片V-电源出口及信号参考地上,高频信号保持在较少环路,对电源线及地线的低频影响小,是有效Decoupling。

图:非有效的Decoupling及有效的Decoupling

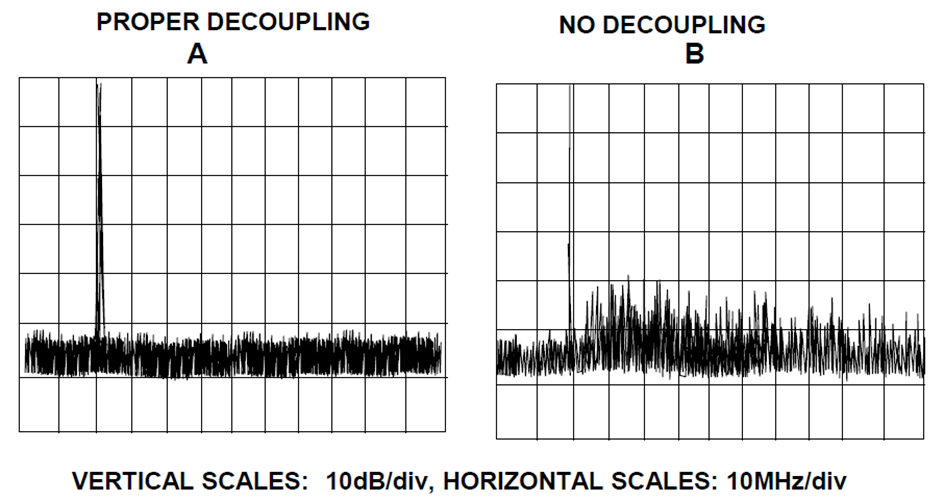

讨论了这么多decoupling的设计,那么在实际电路中decoupling到底有什么影响呢?我们以ADI高速低噪声运放AD9631为例进行说明。下图是AD9631驱动100Ω负载时的输出频谱(输出信号20MHz, )[6]。左图采用了合适的decoupling,频谱很干净,在2次谐波40MHz处谐波失真为-70dBc左右;右图是去掉decoupling后的频谱,可以看到明显的噪声。因此合适的decoupling电路十分重要。

)[6]。左图采用了合适的decoupling,频谱很干净,在2次谐波40MHz处谐波失真为-70dBc左右;右图是去掉decoupling后的频谱,可以看到明显的噪声。因此合适的decoupling电路十分重要。

图:Decoupling对AD9631性能的影响

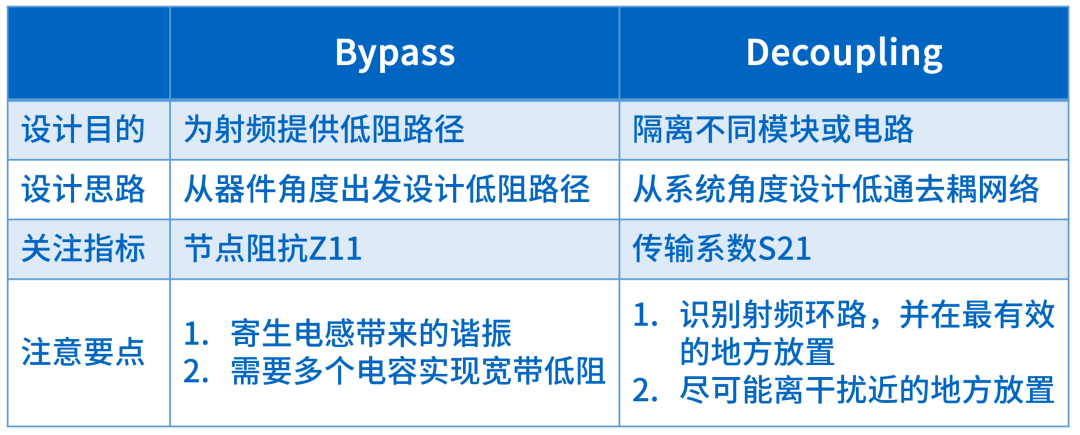

四、Depass与Decoupling的比较

通过以上比较,可以看到因为设计目标的不同,Bypass与Decoupling在设计方法和注意事项中有所不同。二者对比总结如下表:

审核编辑:汤梓红

-

旁路电容和滤波电容,去耦电容分别怎么用?2024-02-03 3091

-

[转] 去耦电容和旁路电容的区别2022-11-04 14428

-

旁路电容和去耦电容的基础知识2022-10-25 2601

-

旁路电容 和去耦电容 !#电容学习电子知识 2022-10-20

-

去耦电容和旁路电容的区别,终于有人说清楚了!2022-07-28 2197

-

旁路电容与去耦电容到底是什么?2021-06-23 5357

-

旁路电容、去耦电容及滤波电容的作用详解2021-06-22 6390

-

去耦电容和旁路电容相关资料分享2021-05-25 2222

-

旁路电容、去耦电容、滤波电容的作用分别是什么2021-03-17 3579

-

旁路电容和去耦电容总结2018-12-07 2763

-

浅谈滤波电容、去耦电容、旁路电容之间区别2018-10-07 30392

-

滤波电容、去耦电容、旁路电容作用2015-10-29 1644

-

去耦电容和旁路电容的区别2011-02-15 9096

全部0条评论

快来发表一下你的评论吧 !