将动态电压和频率缩放集成到指令精确的虚拟平台中

描述

在嵌入式系统中,诸如功耗之类的额外功能要求越来越重要。在 OFFIS 和 Imperas Software 的合作中,开放虚拟平台 (OVP) 技术已配备支持来表达和执行动态电压和频率缩放 (DVFS) 兼容的电源模型。虚拟平台上的软件可以通过DVFS访问实际功耗,进行电源管理。该技术已成功用于基于 ARM 的多核平台,运行合成裸机 DVFS 测试应用程序和 Linux 电源管理。

OFFIS 成立于 1991 年,是由下萨克森州、奥尔登堡大学以及计算机科学系和相关学院的教授组成的非营利组织。OFFIS 致力于技术转让,分为三个研发部门,专注于交通、健康和能源领域的 IT。Imperas Software 是一个由仿真和工具技术专家以及嵌入式软件应用专家组成的团队。

技术基线是基于 OVP 的模型,以及来自 Imperas 的模拟器引擎、多处理器调试器和软件分析工具。虚拟平台是基于(多)处理器的系统的软件模拟,其中包括与存储器和外围组件模型连接的指令精确(IA)处理器模型。这种平台的整体内存布局是完全目标兼容的,需要执行嵌入式软件的目标二进制文件以进行严格的功能验证。本质上,目标软件堆栈并不知道它没有在硬件上运行。

与基于硬件的开发和调试环境相比,虚拟平台的优势包括软件仿真环境中的完全可控性和可观察性、确定性软件执行、易于测试自动化以及更早的仿真环境可用性。并不是说基于硬件的环境应该被虚拟平台取代,而是这两种技术在嵌入式软件流程中是互补的。

该解决方案的关键是确保虚拟平台尽可能高效、快速地执行代码。这需要处理器、外围设备和行为组件的高质量仿真模型,以及执行这些模型的仿真引擎,以每秒执行高达 10 亿条指令的嵌入式软件。对于许多嵌入式处理器平台,Imperas 技术可以以比实时更快的速度执行软件。

OFFIS 与 Imperas 合作的目标是将电源模型集成到整体 Imperas 和 OVP 建模和仿真框架中,以支持电源管理配置和实际电源管理功能的功能测试。为了控制电源特性和对执行速度的影响,使 OVP 模型具有功耗意识的第一步是为 CPU 模型添加电源电压 (Vdd)、时钟频率和“降额”功能。减额只是减少与处理器设置的时钟频率相关的模拟指令数量。

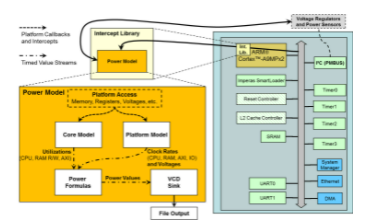

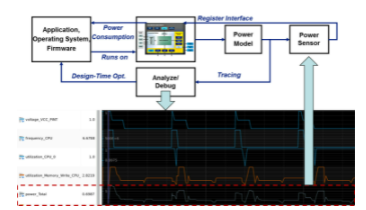

OFFIS 开发的技术称为时间价值流 (TVS),借助它,可以随时间记录、组合、汇总和跟踪任意状态或过程相关单元。TVS 技术已成功应用于 OVP 中,从处理器(例如处理器负载、空闲指令和等待中断)、内存子系统(例如读/写访问、不同 bank 的访问)、总线系统(例如读/写事务、事务长度)和外围组件。结合新集成的和软件可配置的电源电压和时钟频率(动态电压和频率缩放),实现了 Xilinx Zynq SoC 的 ARM 双核处理器 (ARM Cortex-A9MPx2) 子系统的功耗模型。活动、电压和频率迹线的应用组合,

可以将功率信息写入 VCD(Value Change Dump)接收器以显示以供分析。如前所述,可以将功率信息馈入功率传感器,该传感器可以映射到硬件平台的地址空间,从而允许软件访问以在运行时得出功率管理决策。

图中描绘了这种整体应用机制。在这个例子中,电源等动态物理属性的可见性,我们可以在纯虚拟原型中观察使用 DVFS 进行电源管理的效果、功耗以及应用程序的性能。

审核编辑:郭婷

-

随温度变化的动态电压缩放实现2023-09-13 471

-

SIMATIC S7-1500 PLC SIMATIC取消缩放指令2023-06-01 6054

-

SIMATIC S7-1500 PLC缩放化指令简述2023-05-26 10650

-

如何将memtool集成到i.MX8MM Android 12平台中?2023-05-16 802

-

如何将X-CUBE-NFC5代码集成到平台中?2023-02-02 644

-

如何在Arm计算平台中实现机密计算2022-08-05 3619

-

直线电机在平台中有哪些应用?2021-10-29 2198

-

学习ThreadX初步应用并将其移植到STM32平台中2021-08-24 859

-

Kubernetes平台中的日志收集方案2019-11-04 1826

-

基于虚拟仪器的DRVI可重构实验教学平台2019-04-24 2249

-

【Android安全】ARM平台代码保护之虚拟化2016-06-13 2711

-

通用变频器电压输入频率指令图2010-04-09 1200

-

用TPS62200作为OMAP1510的动态电压缩放器2009-12-21 1107

-

在虚拟仪器LabVIEW平台中串行通信模块的应用2009-09-26 490

全部0条评论

快来发表一下你的评论吧 !