IC 制造生命周期中的安全基础知识

电子说

描述

如今,供应链安全是一个热门话题。芯片供应商特别关注,因为他们提供最容易受到信息提取和操纵的组件。同时,原始设备制造商 (OEM) 对了解其芯片供应商供应链中的风险以及这些风险如何影响其最终产品具有既得利益。因此,虽然产品开发的双方都存在安全威胁,但特定于 OEM 生命周期阶段的风险也是一个问题。

这个由两部分组成的系列将着眼于芯片供应商和 OEM 之间的相互关系,以及他们必须如何合作以保护所有制造阶段的漏洞。第一篇文章确定了 IC 生产生命周期每个步骤中的威胁,并描述了如何缓解这些威胁。第二篇文章侧重于 OEM 特定的安全风险,并描述了最终产品制造商和芯片供应商如何承担责任。这些文章将表明 OEM 和芯片供应商可以通过在其每个生产阶段承担风险来防止大部分安全攻击。

IC 生命周期每个阶段的安全威胁

无论是由于代工厂的故意行为还是不良行为者的渗透,IC 生命周期的每个阶段都存在多种威胁,可能使最终产品面临风险。

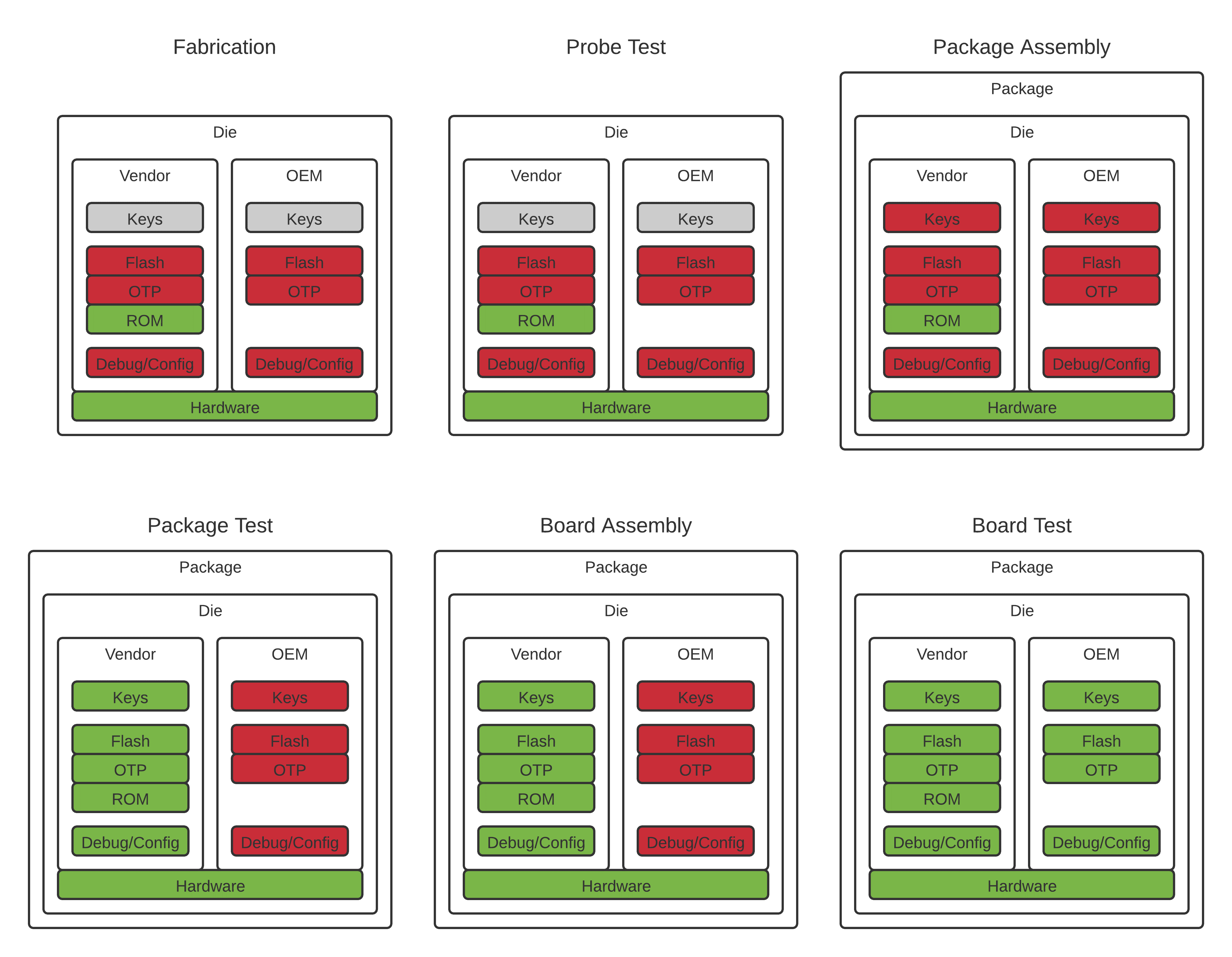

制造生命周期包括以下步骤,如图 1 所示。

制造

探针测试

封装组装

封装测试

电路板组装(OEM 拥有和控制)

电路板测试(OEM 拥有和控制)

图 1 上述概要显示了 IC 生命周期开发的六个关键阶段。资料来源:硅实验室

IC 开发从制造阶段开始,在该阶段设备在代工厂中进行物理制造。此时 IC 的 ROM 已编程,但所有其他存储器(OTP、闪存和 RAM)均未编程。下一步是探针测试,其中 IC 在从硅片上切下之前先进行功能测试。在这个阶段,没有安装永久配置,并且在制造过程中插入的任何数据都将作为测试过程的一部分被删除。

在封装组装阶段,将单个裸片放入封装中。这一步是一个完全机械的过程,不进行编程或测试。一旦进入封装,IC 就会进行封装测试,通常被硅供应商称为“最终测试”,因为这是他们运行的最终测试。

该测试有多种用途:寻找组装过程中的缺陷,检查设备是否存在参数问题,例如功耗过大或特性不合格。此外,它使用任何硅供应商提供的数据初始化设备。然后将设备出售给执行电路板组装的 OEM,然后将设备安装到系统中。接下来,在电路板测试中,IC 接受最终测试、配置和编程。

通过对 IC 生命周期步骤的基本了解,我们现在可以深入了解每个步骤中存在的威胁。在讨论这些步骤时,我们将使用 Silicon Labs 的制造生命周期作为 IC 开发模型。其他半导体供应商将大体相似,因此本概述应适用于大多数供应商。

制造

针对此步骤的攻击极不可能发生,因为它们成本高昂,并且需要生成至少一个新的掩码集、对设备的深入分析以及高度的专业知识。此外,这一步的任何攻击都不能轻易针对特定的最终产品。由于代工厂生产多个晶圆,每个晶圆上都有数千个设备,攻击者无法知道哪些设备最终会用于哪些最终产品。此外,在此开发阶段对设计进行的任何修改都会影响该制造设备的每个副本,从而使其更容易检测。但是,此阶段的漏洞确实会带来安全风险,如以下小节所述。

数据提取

代工厂的一种可能的攻击向量是访问使最终产品面临风险的机密信息。例如,如果 IC 在 ROM 中具有对称或私钥——或硬编码到寄存器等其他硬件中——代工厂可以轻松提取该值。同样重要的是要记住,任何可以从设计中轻松提取的数据也可以通过逆向工程从设备的物理副本中获得。例如,一些实验室将以不到 1 万美元的价格对 ROM 数据进行反处理和提取,这可能比从代工厂获取布局更具成本效益。为避免此问题,精心设计的产品绝不应包含机密信息。

逻辑变化

一个更合理的威胁是铸造厂修改设备以引入可利用的缺陷。这种修改可能包括修改 ROM 的内容或逻辑以改变设备的行为或引入额外的功能。虽然这些类型的更改既困难又昂贵,但基本操作完全在攻击者的能力范围内,可以破坏代工厂。

针对这种攻击的一个很好的对策是进行抽样测试,以验证生产线下随机设备的功能。例如,Silicon Labs 每年可以随机抽取几个样本,并运行测试来验证 ROM 的内容、验证逻辑以及测试其他功能。如果代工厂进行更改,这些测试将失败。虽然可能会引入此测试无法捕捉到的逻辑更改,但此类更改的效果将受到严重限制,可能会达到无用的地步。在受信任的站点(例如,公司总部)执行样品测试可以极大地降低代工厂对硬件进行更改并成功破坏旨在检测它的测试的风险。

篡改检测的未来改进,例如基于机器学习的图像分析,可能会进一步防止未经授权的芯片修改,但这些选项今天不可用。

设备复制

在这种类型的攻击中,代工厂生产过多的设备,然后作为合法设备出售。例如,攻击者可以用修改过的 ROM 过量生产部件,并将它们作为合法的 OEM 出售,绕过旨在捕获此类更改的测试。这种方法允许攻击者直接针对 OEM,因为这些设备不再流经供应商的供应链。

防止过度生产的最佳方法是在包测试时提供加密凭证。然后,OEM 可以检查这些凭据,以确保他们从该供应商处收到了正品设备。尽管代工厂可以生产物理上相同的设备,但他们无法为其生成有效凭证,并且 OEM 会检测到任何假货。

这种缓解需要标准的未锁定设备来安全地保存密钥。Silicon Labs 提供具有此功能的 Vault-High EFR 产品。使用安全级别较低的设备(例如 Vault-Mid 设备而不是 Vault-High 设备)的 OEM 可以通过使用像 Silicon Labs 的定制部件这样的定制编程服务来实现类似的效果(尽管保护级别较低)制造服务(CPMS)。在这种情况下,对设备内容的访问在发货之前被锁定,以便密钥可以保密地存储在非易失性存储器 (NVM) 中。

设备分析

器件分析是代工厂中最现实的威胁。设备在不安全的解锁状态下制造,提供对成品中不可用的逻辑和系统的访问。虽然访问空白的开放部件不会构成直接的安全威胁,但攻击者可以利用这个机会分析设备并寻找可以在配置和锁定部件上利用的弱点。

虽然这种威胁存在于制造过程中,但它更有可能发生在组装步骤中,下面将进行更详细的讨论。

探针测试

An exploit targeting probe test costs less than that of making modifications in the foundry as it only requires the test program or tester to be compromised. However, as with attacks targeting fabrication, probe test attacks are systemic and can’t easily target a specific end-product or OEM.

Malicious code injection

An attacker may attempt to inject malicious code onto the device during probe test. However, any content injected at this step will either be erased at package test or cause the package test to fail when the vendor can’t program the correct content. In addition, secure boot will prevent any attempt to install unauthorized code once enabled in package test. This threat is not realistic for well-implemented products and production lifecycles.

Device analysis

理论上,在探测测试中控制测试仪的攻击者可以执行设备分析,类似于通过代工厂的过度生产可以实现的分析。但是,攻击者更有可能在组装步骤中尝试获得此访问权限。

封装组装

由于这是供应商将设备放入最终外形尺寸的步骤,因此封装组装是攻击者最有可能窃取空白、打开的设备以进行复制和分析的地方。

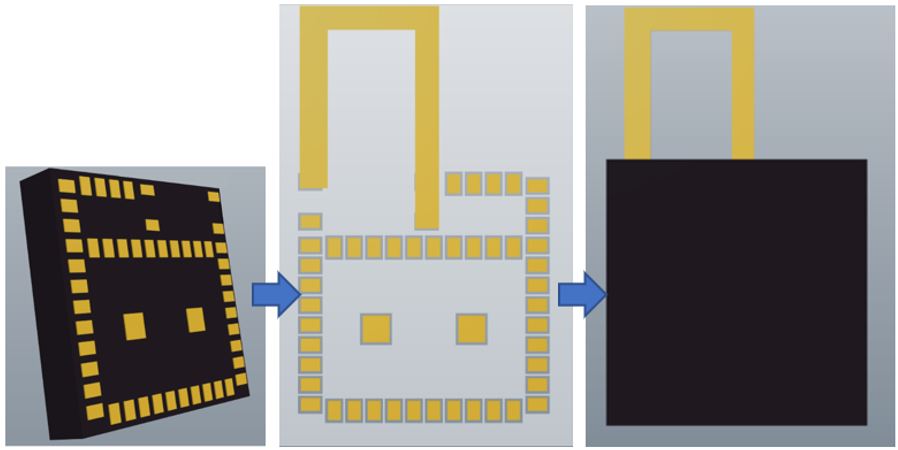

点击查看完整大小的图片

图 2 芯片制造商必须确保降低与开放样品相关的风险。资料来源:硅实验室

盗窃

窃取空白设备的目的是获取开放样本,以对攻击者有利的方式对其进行配置,然后将它们作为合法设备交付给目标 OEM。此策略允许针对特定的 OEM 或产品并绕过供应商的最终测试,否则会覆盖或检测修改。

与没有输入数量的制造步骤不同,组装现场接收并生产已知数量的 IC,因此通过比较这些数字应该很容易发现任何重大盗窃行为。

而且,与制造一样,我们可以通过在封装测试中对加密凭证进行编程来防止被盗的开放设备被假冒为正品。例如,为此目的,所有 EFR Vault-High 产品都配备了加密凭证,并且提供了 CPMS 以在没有 Vault-High 功能集的设备上配置凭证。

设备分析

此阶段设备分析的最明显示例是攻击者在安全引擎 (SE) 被编程和锁定之前窃取设备,并使用该访问权限来了解邮箱机制和 SE 硬件的功能。从理论上讲,这种访问可以让攻击者识别出一个弱点,然后可以将其转化为针对锁定 SE 的漏洞利用。

器件分析只需要从组装现场获取少量器件。虽然限制对开放样本的访问是理想的防御层,但应该假设攻击者将在某个时候获得对开放样本的访问权限。IC 的设计方式不应造成不可接受的风险或破坏系统的安全性。

Silicon Labs 采取了几个步骤来降低与开放样品相关的风险,包括审核组装承包商的流程和程序,跟踪内部用于开发的任何开放设备,以及在不再需要时销毁开放样品。此外,产品旨在保持安全,即使是针对具有开放样本和完全访问设计的攻击者。最后,内部和第三方渗透测试均由具有开放样本、全面设计知识和高度专业知识的个人执行。

硬件改造

今天,使用更改或附加组件修改包装所带来的风险相当小。这不是一个高风险的攻击媒介有几个原因。首先,组装距离终端系统足够远,因此很难针对特定的终端设备(如门锁)。此外,空间限制使得隐藏 IC 的任何添加变得困难。最后,抽样测试可以通过对几个单元进行 X 射线检测以识别意外组件来检测任何大规模攻击。

封装测试

有许多通用方法可以使包测试阶段的漏洞利用变得更加困难,包括限制对测试站点的访问和维护日志记录控制。首先,应遵守网络和 PC 的正常安全做法。例如,测试系统不应直接连接到 Internet,也不应使用可通信的登录凭据。供应商应对这些流程和系统进行定期审查,以确保它们不被更改或利用。这些简单的操作会使攻击者更难获得对测试系统的访问权限。

图 3 在封装测试站点,拥有不受其他供应商影响的受信任机器至关重要。资料来源:硅实验室

Silicon Labs 部署了多种技术来在其测试站点提供增强的安全性。例如,该公司委托不与其他供应商共享的安全强化测试人员。此外,Silicon Labs 为测试站点提供了一台受信任的机器,该机器不受其影响,可用于监控和支持测试人员。这台机器位于服务器机房中,没有本地接口,并且包含旨在抵御物理攻击的硬件。

恶意代码注入

在这个阶段最明显的攻击方法是注入恶意代码来编辑设备的行为。芯片厂商在此步骤提供的代码,例如 SE 固件,不会被板测试覆盖;但是,如果可以更改,则可以运送受损设备。

这种风险可以通过在 ROM 中使用带有公钥的安全引导来消除,从而确保只有正确签名的代码才能运行。如果攻击者试图修改程序代码,它将不再被正确签名,并且设备将停止运行。由于用于签名的密钥存储在硬件安全模块 (HSM) 中,受到严格控制,并且在任何生产环境中都不可用,因此攻击者极不可能为被操纵的图像生成正确的签名。

由于测试要求,固件编程后启用安全启动。尽管复杂,但这种生产流程使攻击者有可能破坏包测试,从而对恶意映像进行编程并禁用安全启动。

为了完全消除这种威胁,IC 应允许 OEM 验证设备的状态,而不受任何编程代码的影响。例如,Silicon Labs 设备有一个硬件寄存器,用于指示 SE 子系统是否已锁定,并允许 OEM 应用程序或测试程序验证设备配置是否正确。通过此验证,OEM 可以检测到任何封装测试更改或恶意代码,并丢弃这些更改的部分。

提取机密信息

如果在包测试期间对任何机密信息进行了编程,攻击者可能会通过破坏测试系统来寻求访问权限。对于标准嵌入式产品,与凭证关联的密钥是唯一存在的机密信息。对于在机上生成这些密钥的设备,将无法提取;但是,如果测试系统注入密钥,那么攻击者可以获得所需的访问权限,以便在编程时查看这些值。

使用机密的、OEM 特定信息定制的设备特别容易受到此类攻击的威胁。但是,遵循本系列文章中建议的芯片供应商可以提供达到或超过大多数电路板测试设施的安全级别。始终建议 OEM 与芯片供应商合作,以确定设备编程的最佳解决方案。

供应链安全需要分层方法

安全性是一个系统级问题,需要供应商和 OEM 在开发互联产品时作为值得信赖的合作伙伴共同努力。随着我们在构建物联网 (IoT) 方面取得进展,对于 OEM 来说,评估其芯片供应商在其制造生命周期中处理安全性的成功程度至关重要。在决定使用哪些供应商时,OEM 应考虑供应商提供的透明度和彻底性水平,以及其 IC 的成本和性能。

立即与您的供应商讨论他们的制造安全性以及他们如何帮助确保您的最终产品的安全性。

本系列文章的第二部分将解释 IC 制造生命周期的最后两个阶段,这与 OEM 特定的安全风险有关。

— Joshua Norem是 Silicon Labs的高级 系统 工程师 。

审核编辑 黄昊宇

-

关于生命周期中的aboutToAppear和onPageShow的理解和应用2025-06-30 117

-

ServiceAbility的生命周期介绍2025-05-28 566

-

什么是PLM产品生命周期管理系统?2024-11-23 4560

-

基于Rust语言中的生命周期2023-09-19 1763

-

在S32G2 RM中有“生命周期”,生命周期的完整含义是什么?2023-04-23 748

-

确保智能电表的全生命周期安全2023-03-06 1977

-

Vue入门Vue的生命周期2023-02-06 1513

-

Spring中Bean的生命周期是怎样的?2022-10-11 2180

-

探讨OEM制造生命周期的安全性问题2022-09-26 2054

-

Synopsys 启动硅生命周期管理计划2022-08-18 1512

-

了解产品制造生命周期中的安全风险问题2022-07-13 3930

-

基于闭环生命周期的知识集成与语义标注2017-12-01 886

-

安全软件开发生命周期与业务安全2017-09-08 1275

-

贯穿于全生命周期的功能安全2008-12-19 732

全部0条评论

快来发表一下你的评论吧 !