软件定义无线电中的尺寸、重量和功率与性能权衡

电子说

描述

软件定义无线电 (SDR) 出现后,射频 (RF) 世界彻底改变。这些设备将射频行业的主要技术范式从固定和笨重的模拟电子设备转变为灵活紧凑的基于软件的信号处理,显着增加了商用现货 (COTS) 无线电系统的适用范围。因此,SDR 现在主导着 RF 市场,用于各种应用。然而,每个应用都有自己的要求,包括尺寸、重量和功率 (SWaP)、性能和成本,因此开发人员必须仔细设计 SDR 以符合市场需求。在设计流程中必须评估的主要瓶颈是 SWaP 和性能之间的权衡:每个 SDR 由许多不同的组件组成,

在本文中,我们讨论了如何设计 SDR,以满足具有各种性能、通道数和数字信号处理器 (DSP) 处理能力的多个市场的需求,同时通常需要考虑 SWaP 和预算限制。事实上,与传统的模拟对应物相比,仅使用 SDR 本身就可以将射频系统的总尺寸和重量减少 80% 或更多,这非常适合多种应用,包括 MRI、雷达、频谱监测、点对点点链接,以及测试和测量。然而,关键市场需要进一步降低 SWaP 和成本,这是通过降低某些组件的性能或特性总数来实现的,例如减小调谐范围、接收 (Rx) 和发送 (Tx) 通道的数量、 DSP 能力和总带宽。

SDR、电源要求和性能规格概述

在讨论设计权衡之前,让我们回顾一下 SDR 的基础知识。SDR 本质上是一个收发器,具有复杂的嵌入式处理能力,以及用于通过软件更改无线电参数的灵活/可重新配置平台。通用 SDR 分为三个阶段:

无线电前端 (RFE)

数字后端

混合信号接口。

RFE 由一个或多个 Rx 和 Tx 通道组成,能够处理高达数十千兆赫 (GHz) 的宽调谐范围内的信号。此外,市场上带宽最高的 SDR 可提供每通道 3 GHz 的瞬时带宽,并与多达 8 个独立的 Rx/Tx 信号链一起工作。

另一方面,数字后端负责所有信号处理操作、控制功能、智能、数据存储和通信协议。该阶段由具有板载 DSP 功能的高端 FPGA 组成,针对调制、解调、上变频、下变频、数据打包和任何所需的特定应用功能(如安全方案或人工智能)进行了优化。FPGA 还与主机或网络进行通信,将数据打包成以太网数据包,并通过 SFP+/qSFP+ 链路以 10-400 Gbps 的传输速率进行传输。由于 FPGA 能够完全改变其内部结构,数字后端可以轻松地重新配置或即时升级,以适应最新的无线电协议和 DSP 算法。

最后,混合信号接口由专用的数模和模数转换器 (DAC/ADC) 组成。SDR 的每个阶段都由一组不同的组件组成,每个组件的设计和尺寸都可以设计为实现特定的 SWaP,高端 SDR 还兼容无线电处理软件,例如 GNU radio。

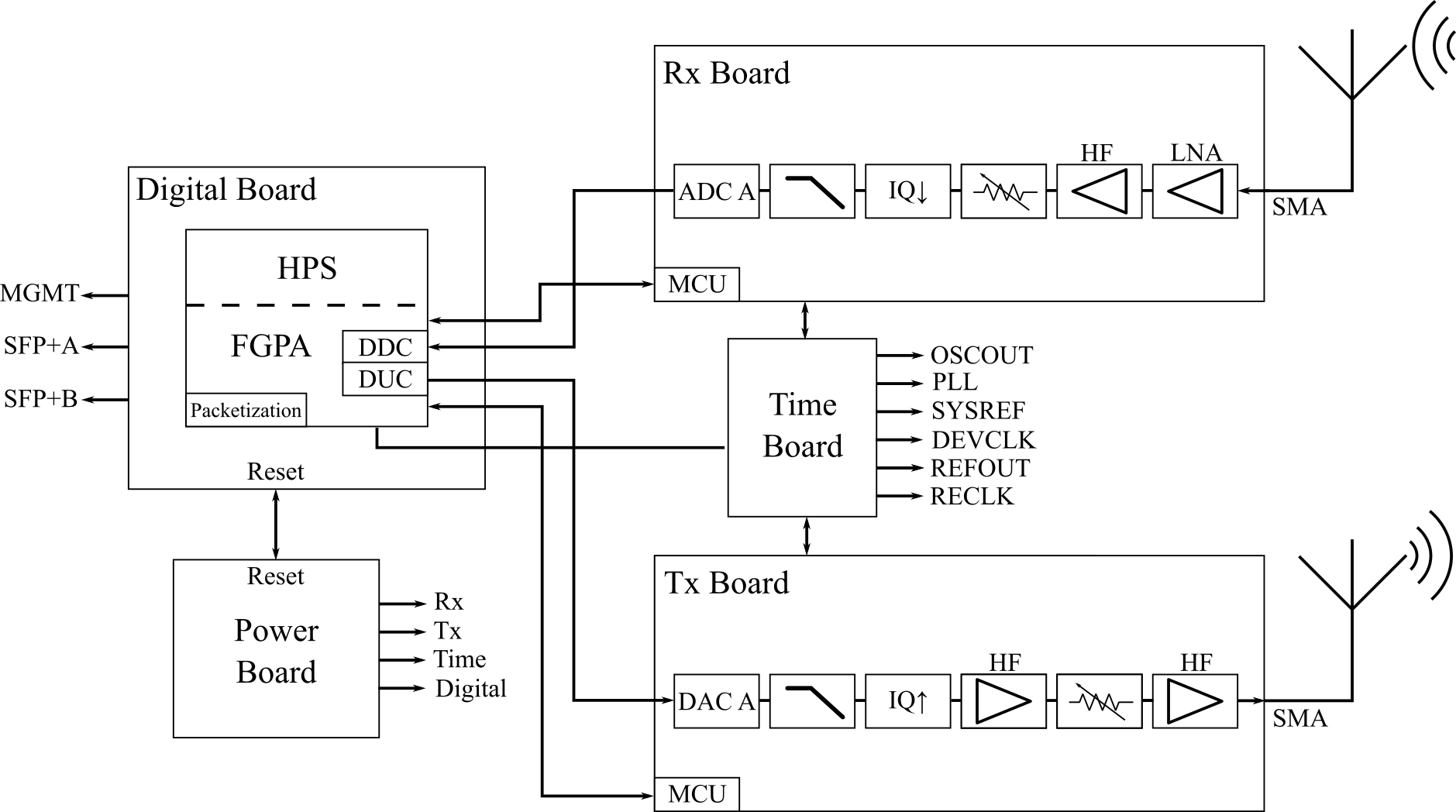

根据前面的硬件描述,市场上有几种不同的 SDR 配置。高性能 SDR 通常需要使用 5 个板:Rx 板、Tx 板、数字板、电源板和时间板(见图 1)。Rx 板只是接收信号的 RFE 的一部分,以 ADC 终止。Tx 板由 RFE 的传输通道组成,通常以 DAC 开头。每个 Rx 和 Tx 板都可以由多输入/多输出 (MIMO) SDR 中的多个并行通道组成。数字板提供了一个接口来控制、配置和发送/接收 RFE 通道的数据,所有这些都由时间板保持同步。电源板只是将线路电力转换为 RFE、数字和计时板可用电压水平的电源。最后,

点击查看完整大小的图片

图 1:SDR 板架构。(来源:每恶习)

任何电子系统中最基本的限制是功率要求:任何需要定制 PCB 设计的应用也需要功率预算。这是因为电源方案及其局限性在很大程度上取决于应用程序,因此对于具有不同目标的类似项目,电源预算可能会有很大差异。例如,使用电池供电的 SDR 的功率预算与连接到电网的 SDR 的预算有很大不同。此外,电源必须从电源板馈送到 SDR 收发器中的所有其他模块。

由于每块电路板都需要特定的稳定和干净的电压电平,并且必须不受电源波动的影响,因此稳压器是配电中的关键组件。这些组件是集成电路,无论负载或输入电压如何变化,都能提供恒定的输出电压,并且在功率预算中也必须考虑到它们。

然而,由于必须执行大量计算,SDR 的最大功耗来源是 FPGA。FPGA 的功耗可以通过软件进行优化,通过减少运算次数和优化信号处理链。繁重的计算会消耗大量的能量。例如,JESD204 收发器消耗大量功率。

另一个重要因素是 RFE:RFE 的功耗随着特征数量、工作带宽、调谐范围和通道数量的增加而增加。一些组件比其他组件需要更多的功率,因此在设计流程中必须为每个组件权衡功率和性能之间的权衡。

就像功率需求一样,性能需求也高度依赖于应用,这可以用无线电链路预算来描述。无线电链路预算方程用于确定如何更改设计以实现一定的性能水平,这由接收功率强度表示(方程 1)。计算出链路预算后,可以检查设计是否能够满足性能要求(例如误码率、信噪比 (SNR) 和线性度)。

| RxPower(dBm) = TxPower(dBm) + 增益(dBm) – 损耗(dBm) | (1) |

SDR 领域有几种不同的性能要求,对设计和应用有不同的影响。在这里,我们讨论一些最重要的:

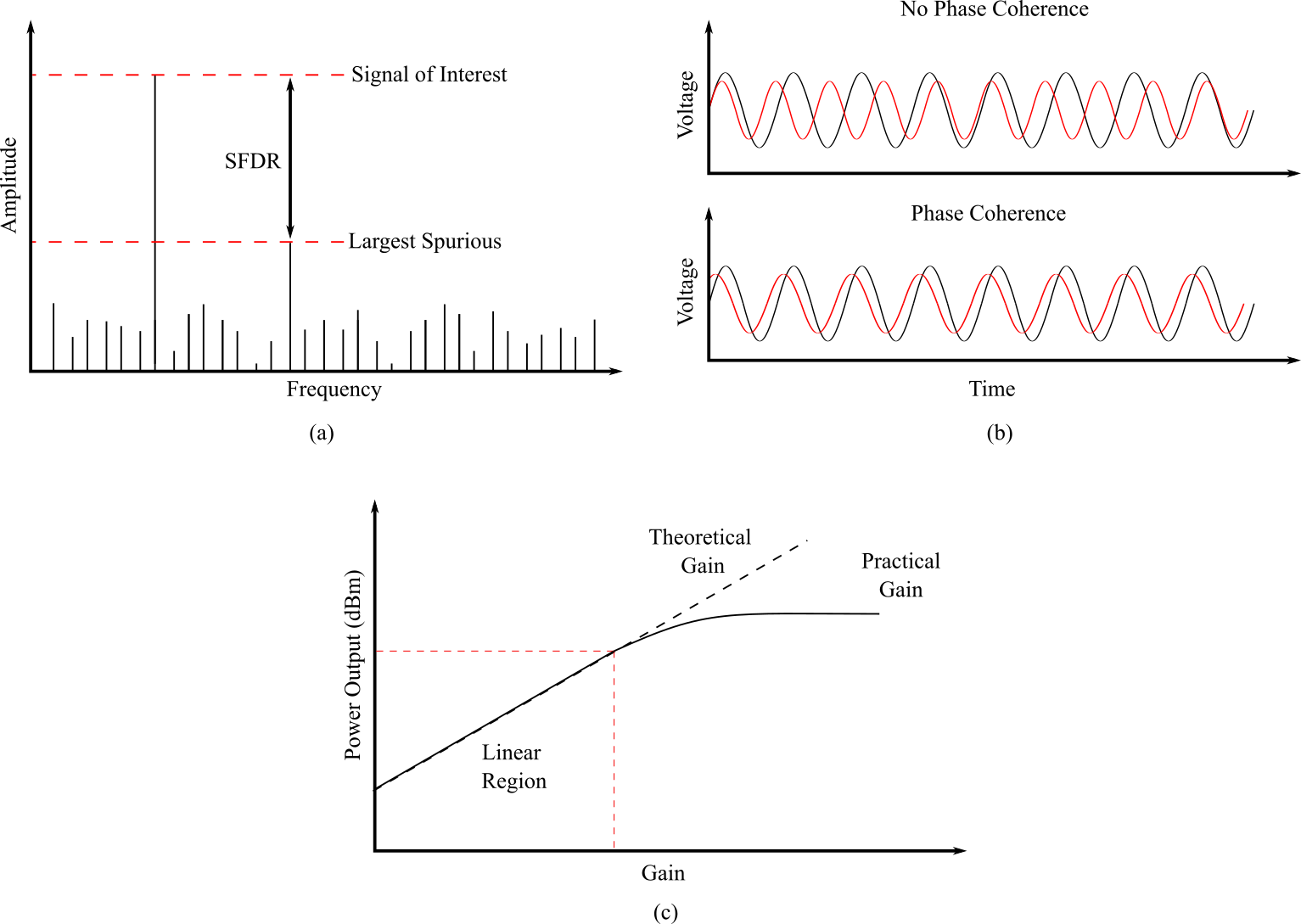

动态范围:也称为无杂散动态范围 (SFDR),定义了基波谐波强度与输出中最高杂散信号之间的比率。它用于定义 SDR 的动态性能。这可以在图 2a 中看到。

相位一致性:量化 SDR 模块的相位同步程度。它依赖于时钟板的质量和时钟分布,因为时钟信号必须由所有组件正确共享。这可以在图 2b 中看到。

信噪比 (SNR):它是信号功率与接收到的总射频噪声之间的比率。它可能是无线电系统最重要的参数之一,具体取决于应用,并描述了在给定外部和内部条件的情况下接收到的电磁 (EM) 信号的质量。它取决于环境条件(降水、闪电、湿度、温度)、RFE 的电子设备(热噪声、散粒噪声、闪烁噪声)和外部 EM 发射器(传输线、发电厂、发电机、电话)。

灵敏度:接收器可以检测到的最低信号。它与 SDR 和 SFDR 密切相关。

数据吞吐量:描述数据发送到主机或网络的速度。在 MIMO 和频谱监测应用中尤为重要。

调谐范围: SDR 可以接收和发送的最大频率范围。这显着影响了设备的适用范围。

RF 输出增益: Tx 信号链末端的输出功率,它定义了可以传输多少功率。

RF Input Gain:接收机输入端的 LNA 增益,极大地影响 SNR 和整体信号增益。

线性度:描述信号链引入的失真量(谐波和互调),特别是来自放大器的失真。这可以在图 2c 中看到。

点击查看完整大小的图片

图 2:性能指标包括 (a) SFDR、(b) 相位相干性和 (c) 线性。(来源:每恶习)

尽管有许多与功率对比相关的限制在性能权衡方面,仅向系统添加 SDR 就可以通过将射频/模拟和大多数计算功能集成在一个系统中来显着降低整个系统的复杂性。然而,特别提款权本身提出了一些挑战。例如,调谐范围越高,时钟方案就越复杂,以应对频率的增加。这也增加了 RFE 的复杂性,进而显着影响功率要求。无线电链的数量也增加了功耗,因此 MIMO 板将比单通道 SDR 具有更高的功率需求。事实上,当不需要接收(或发送)功能时,某些应用需要仅具有发送(或接收)功能的 SDR。功率需求也随着 RFE 增益(输入和输出)和 ADC 分辨率的增加而增加,因此实现更好的 SNR、SFDR、线性度和灵敏度通常伴随着所需功率的增加。最后但同样重要的是,FPGA 中 DSP 操作的数量和复杂性是影响功耗的主要因素之一。例如,在需要对大量数据进行大量快速傅立叶变换 (FFT) 处理的应用中,FPGA 的效率将大大降低。这也凸显了 FPGA 和 RFE 之间需要平衡的必要性,因为 RFE 性能的降低实际上会增加功耗,因为需要 FPGA 所需的更多处理功率。FPGA中DSP运算的数量和复杂度是影响功耗的主要因素之一。例如,在需要对大量数据进行大量快速傅立叶变换 (FFT) 处理的应用中,FPGA 的效率将大大降低。这也凸显了 FPGA 和 RFE 之间需要平衡的必要性,因为 RFE 性能的降低实际上会增加功耗,因为需要 FPGA 所需的更多处理功率。FPGA中DSP运算的数量和复杂度是影响功耗的主要因素之一。例如,在需要对大量数据进行大量快速傅立叶变换 (FFT) 处理的应用中,FPGA 的效率将大大降低。这也凸显了 FPGA 和 RFE 之间需要平衡的必要性,因为 RFE 性能的降低实际上会增加功耗,因为需要 FPGA 所需的更多处理功率。

除了功率,另一个重要的权衡是尺寸/重量与性能。在这种情况下,要求越小,电路板的问题就越多。例如,混合信号板可能会受到串扰、接地干扰、一般 EMI 效应和寄生阻抗的严重影响。如果来自数字电路的噪声到达模拟信号路径,噪声性能就会下降。此外,随着 IC 尺寸减小且没有足够空间放置大型散热器,散热也成为问题。一种有效的方法是使用差分信号和适当的接地。此外,模块化 SDR,例如来自 Per Vices 的 SDR,可以通过根据应用移除/添加功能板来适应任何应用,从而使用相同的设备提供更紧凑的解决方案。

应用程序及其各自的要求

在讨论 SWaP 限制时,卫星部署始终是最有问题的应用。机载 SDR 必须非常紧凑和轻便,以减少有效载荷,尤其是在纳米卫星任务中。因此,在设计电路板时必须仔细考虑,以确保在紧凑的空间中散热和信号完整性都可以接受。此外,电力需求由太阳能电池板和车载电池决定,因此能源供应可能会受到很大限制。卫星需要多个射频通道,包括遥测和控制 (TT&C)、下行链路/上行链路和导航。但是,必须尽量减少通道总数以符合 SWaP 要求。在这种情况下,SDR 可以帮助优化 SWaP,因为可以远程重新配置信道参数(频率、调制、用途),

在地面站中,尺寸/重量要求较为宽松,但必须始终考虑功耗,尤其是在偏远地区应用时。最重要的性能参数是通道灵敏度(主要由 SNR 和 SFDR 定义)和调谐范围。因此,使用具有更高分辨率和采样频率的 ADC 是有意义的。这在来自太空的下行链路信号中尤为重要,其中高频信号(X 和 K 波段)受到环境条件的严重衰减。高端 ADC 显着增加了功耗,结合更高的数据吞吐量和快速的信号处理导致固有的更大 SWaP 要求,这对于性能和成本最重要的地面站通常不是问题。

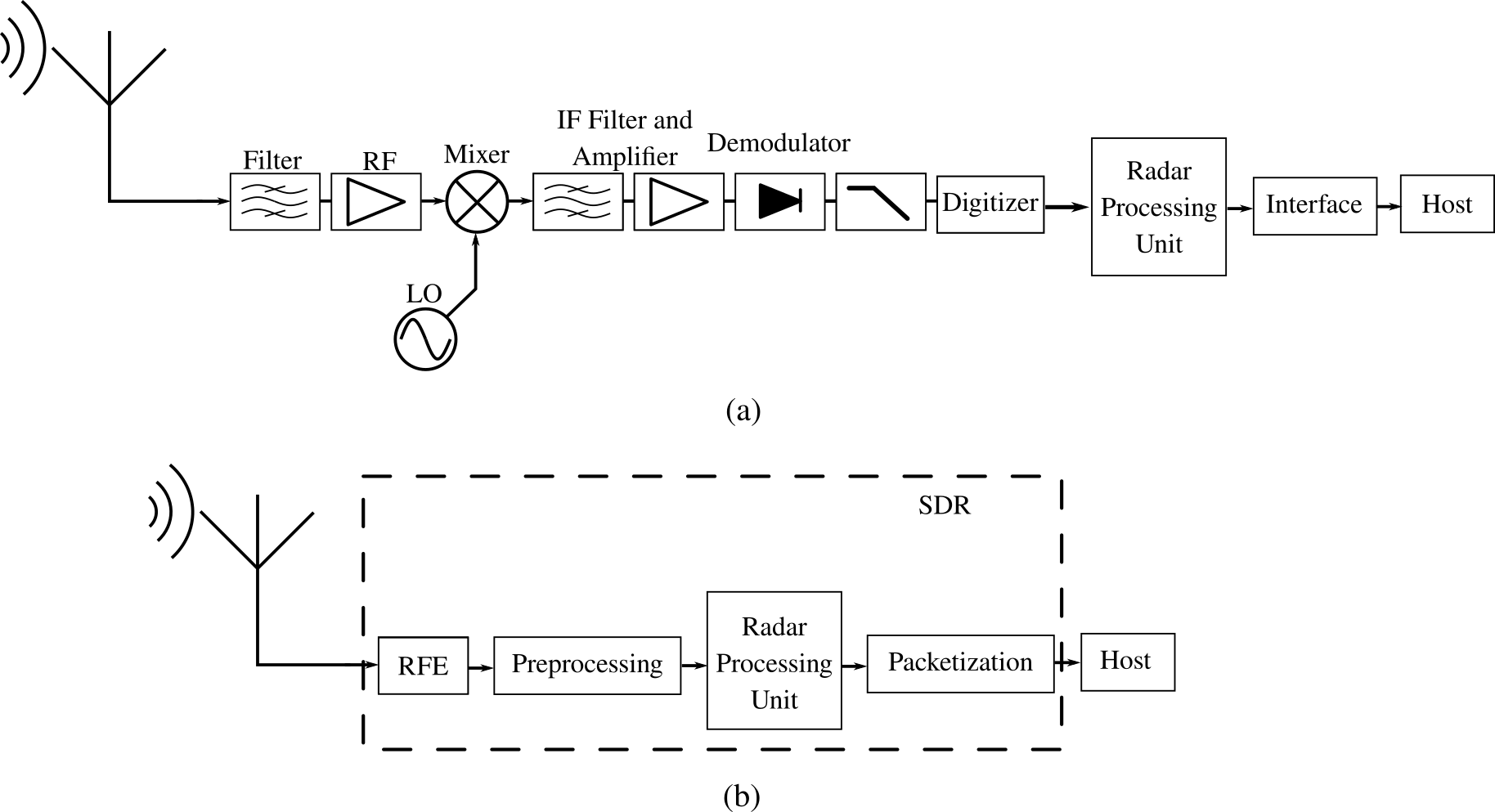

在复杂的雷达系统中,SDR 可以通过替换大型和笨重的传统模拟系统来大大降低 SWaP 要求(图 3)。SDR 可以在单个解决方案中实现波形生成、定时处理、RFE 和完整的信号处理链,从而减小雷达的总尺寸和复杂性。此外,关键雷达应用可以显着受益于 MIMO SDR 的低噪声系数和出色的相位相干性和稳定性,以紧凑的外形尺寸达到高性能水平。

点击查看完整大小的图片

图 3:使用 (a) 传统模拟射频解决方案和 (b) 基于 SDR 的射频系统的雷达接收器。(来源:每恶习)

另一个值得一提的应用是频谱监测。在这些应用中,高数据吞吐量是强制性规范,因为必须实时接收大量数据并将其发送到主机。例如,当一次监测 1 GHz 的频谱块时,需要高性能设备。高端 COTS SDR,例如Cyan 模型来自 Per Vices,通过 4×40/100Gbps 以太网链路传输数据,由于需要 FPGA 打包的数量,它以增加功率要求为代价满足频谱监控要求。此外,还需要快速 FFT 处理,这大大增加了功率预算。随着使用非常灵敏的线性放大器,消耗量也会增加,从而确保具有高检测能力的平坦且宽的检测带宽。因此,设计具有有限 SWaP 要求的有效频谱监控解决方案非常困难,但在许多高性能频谱监控应用中,这不是问题。

结论

SDR 在市场的各个方面都主导着射频行业。从硬件到软件的范式转换确保了更好的灵活性、更高水平的可重构性并降低了 SWaP 要求。然而,一些关键应用仍然需要具有优化 SWaP 属性的 SDR。在设计级别,必须为每个应用程序评估两个主要权衡:性能与功耗以及性能与尺寸/重量的权衡。在第一个方面,具有高性能的高端组件需要大量功率,因此通过减少功能数量或正确组件的性能水平可以显着提高 SWaP。在第二种情况下,关键应用程序所需的尺寸减小通常会降低 SDR 的整体性能,这可以通过减少特征的数量来补偿。一般来说,性能的提高会导致 SWaP 预算的增加,但适当的优化可以在不降低整体性能的情况下优化 SWaP。在这种情况下,模块化 SDR 非常可取,因为它提供了可由应用工程师定制的 COTS 解决方案,因此可以针对特定任务进行优化。

审核编辑 黄昊宇

-

软件无线电的定义和特点(1)#软件无线电未来加油dz 2023-07-03

-

高中频采样使宽带软件定义无线电触手可及2023-06-14 1799

-

什么是软件无线电?2022-04-15 13140

-

软件无线电中ADCDAC性能分析及应用讲解2021-09-16 976

-

软件无线电中ADCDAC性能分析及应用总结2021-08-04 864

-

什么是软件定义无线电(SDR)?2021-06-17 3857

-

接收机在软件定义无线电中的电磁兼容问题2021-06-10 1572

-

软件无线电技术中的关键技术——软件无线电的架构2021-04-08 6628

-

软件无线电设计解决方案2019-07-29 1794

-

基于FPGA的软件定义无线电参考设计2019-07-04 1962

-

软件无线电、无线电的技术概述及应用2018-08-21 4420

-

真正实现软件定义无线电设计2015-08-14 3969

-

实现软件定义无线电和认知无线电的自适应特性2010-03-05 584

全部0条评论

快来发表一下你的评论吧 !