考虑数据采集应用中的采样时钟抖动

电子说

描述

许多数据采集 (DAQ) 应用需要隔离式 DAQ 信号链路径,以实现稳健性、安全性、高共模电压,或消除可能在测量中引入误差的接地回路。ADI 的精密、高速技术使系统设计人员能够以相同的设计实现高 AC 和 DC 精度,而无需牺牲 DC 精度以获得更高的采样率。然而,为了实现高 AC 性能,例如信噪比 (SNR),系统设计人员需要考虑采样时钟信号或控制采样和转换的转换启动信号上的抖动引入的误差。在 ADC 中保持 (S&H) 开关。随着感兴趣的信号和采样率的增加,控制 S&H 开关的信号上的抖动成为更主要的误差。

当 DAQ 信号链被隔离时,用于控制 S&H 开关的信号通常来自用于多通道同步采样的背板。系统设计人员必须选择具有低抖动的数字隔离器,以使进入 ADC 的 S&H 开关的最终控制信号具有低抖动。由于高数据速率要求,LVDS 是精密高速 ADC 的首选接口格式。它还对 DAQ 电源和接地层产生最小的干扰。本文将解释如何解读 ADI 公司 LVDS 数字隔离器的抖动规范,以及在连接精密高速产品(如ADAQ23875 )时哪些规范很重要DAQ µModule® 解决方案。本文中概述的指南适用于使用具有 LVDS 接口的其他精密、高速 ADC。当与ADN4654千兆位 LVDS 隔离器结合使用时,还将在 ADAQ23875 的上下文中解释计算对 SNR 的预期影响的方法。

抖动如何影响采样过程

通常,时钟源在时域中有抖动。在设计 DAQ 系统时,了解时钟源的抖动量很重要。

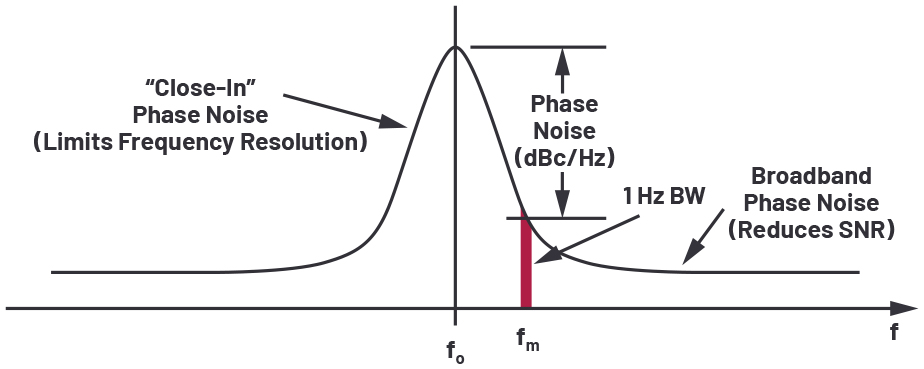

图 1 显示了非理想振荡器的典型输出频谱,其中 1 Hz 带宽内的噪声功率是频率的函数。相位噪声定义为指定频率偏移 f m处 1 Hz 带宽内的噪声与基频 f o处的振荡器信号幅度之比。

点击查看完整大小的图片

图 1. 相位噪声引起的振荡器功率谱。

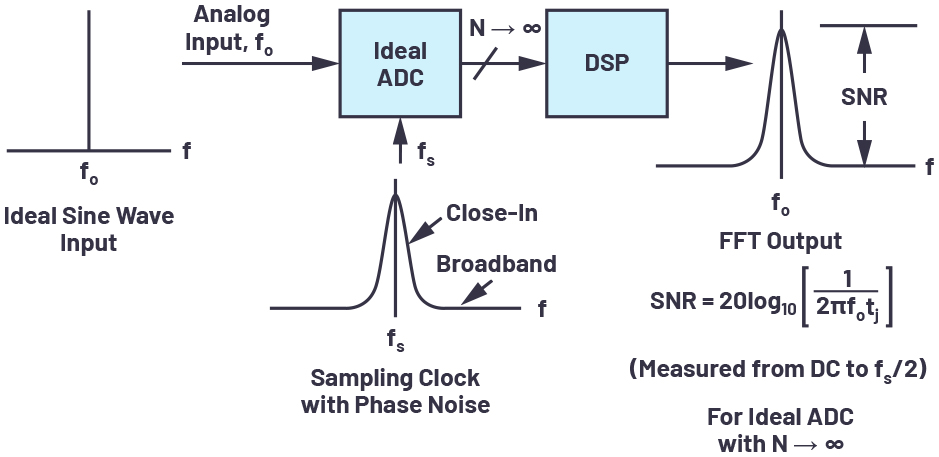

采样过程是采样时钟与模拟输入信号的乘积。这种时域中的乘法相当于频域中的卷积。因此,在 ADC 转换过程中,ADC 采样时钟的频谱与纯正弦波输入信号进行了卷积,因此在 ADC 输出数据的 FFT 频谱中会出现采样时钟上的抖动或相位噪声,如图图 2。

点击查看完整大小的图片

图 2. 使用相位噪声采样时钟对理想正弦波进行采样的效果。

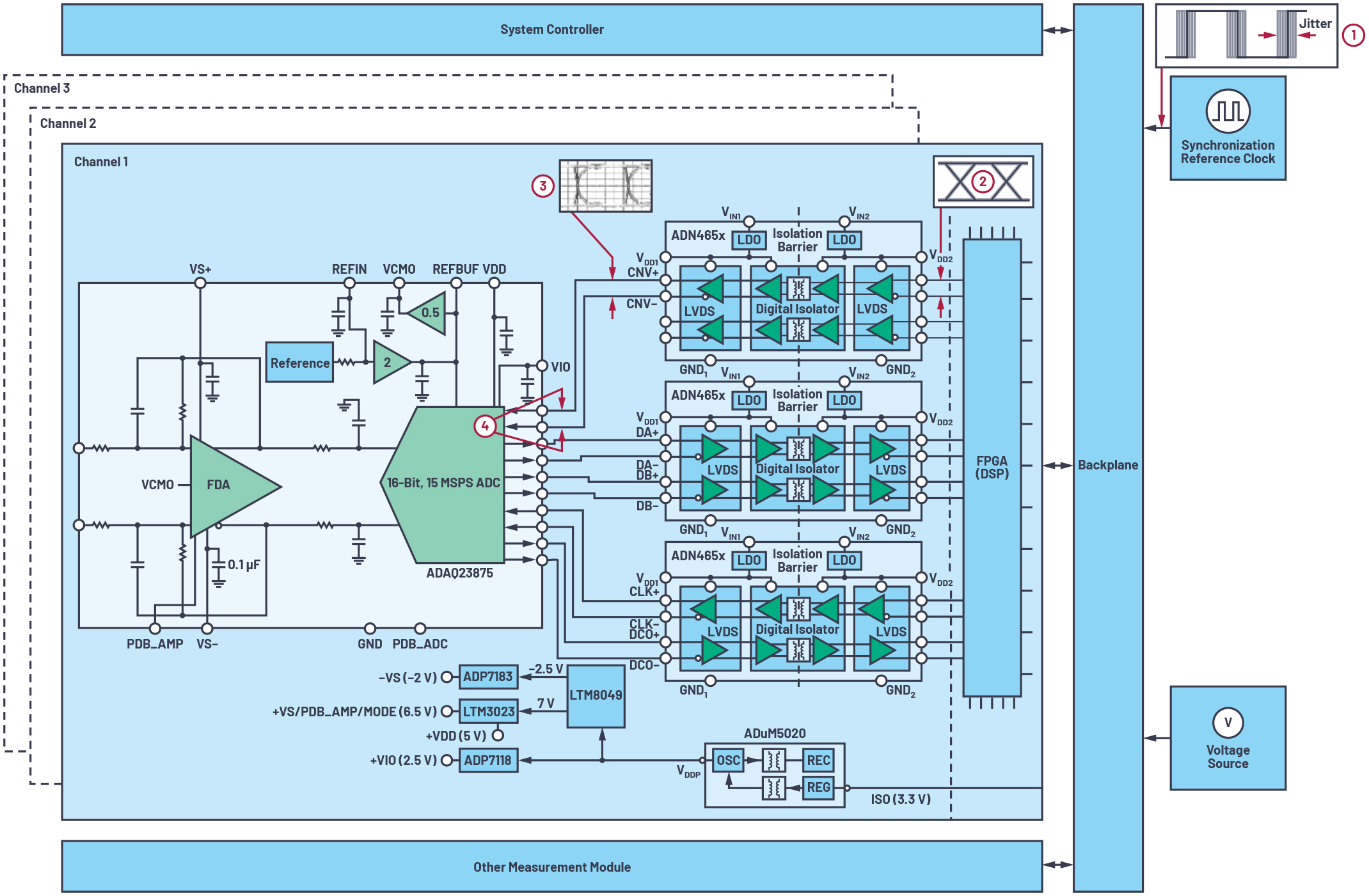

隔离精密高速数据采集应用

多相功率分析仪是隔离式精密高速 DAQ 应用的一个示例。图 3 说明了具有通道间隔离的典型系统架构,以及用于与系统计算或控制器模块通信的通用背板。在本例中,我们选择了 ADAQ23875 精密、高速 DAQ 解决方案,因为它的解决方案占位面积小——可以轻松地将多个隔离式 DAQ 通道安装在一个小外形尺寸中,从而减轻用于现场测试用例的移动仪器的重量。DAQ 通道通过 LVDS 千兆位隔离器 (ADN4654) 与主机箱背板隔离。

隔离每个 DAQ 通道使每个通道能够直接连接到具有显着不同共模电压的传感器,而不会损坏输入电路。每个隔离 DAQ 通道的接地跟踪具有一定电压偏移的共模电压。使 DAQ 信号链能够跟踪与传感器相关的共模电压,无需输入信号调理电路来适应大输入共模电压并为下游电路消除高共模电压。隔离还为用户提供了安全性,并消除了可能影响测量精度的接地回路。

同步所有 DAQ 通道的采样事件在功率分析仪应用中至关重要,因为与采样电压相关的时域信息不匹配会影响后续计算和分析。为了跨通道同步采样事件,ADC 采样时钟通过 LVDS 隔离器来自背板。

在图 3 所示的隔离式 DAQ 架构中,以下抖动误差源会影响控制 ADC 中 S&H 开关的采样时钟的总抖动。

1. 参考时钟抖动

采样时钟抖动的第一个来源是参考时钟。该参考时钟通过背板连接到每个隔离的精密高速 DAQ 模块和插入背板的其他测量模块。它作为 FPGA 的时序参考;因此,FPGA 内部的所有事件、数字模块、PLL 等的时序精度都取决于参考时钟的精度。在一些没有背板的应用中,板载时钟振荡器用作参考时钟。

2. FPGA 抖动

采样时钟抖动的第二个来源是 FPGA 添加的抖动。重要的是要记住 FPGA 内部有一条触发到执行的路径,并且 FPGA 内部的 PLL 和其他数字模块的抖动规范有助于系统的整体抖动性能。

3. LVDS 隔离器抖动

采样时钟抖动的第三个来源是 LVDS 隔离器。LVDS 隔离器具有附加的相位抖动,有助于提高系统的整体抖动性能。

4. ADC的孔径抖动

采样时钟抖动的第四个来源是 ADC 的孔径抖动。这是 ADC 固有的,并在数据表中定义。

点击查看完整大小的图片

图 3. 通道间、隔离式 DAQ 架构。

在相位噪声方面给出了参考时钟和 FPGA 抖动规范。要计算对采样时钟的抖动贡献,需要将频域中的相位噪声规范转换为时域中的抖动规范。

从相位噪声计算抖动

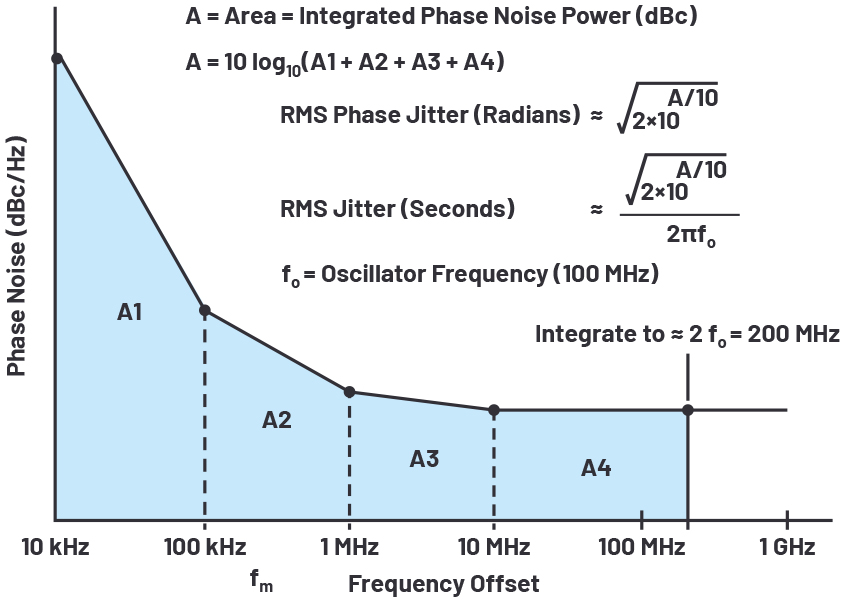

相位噪声曲线有点类似于放大器的输入电压噪声谱密度。与放大器电压噪声一样,振荡器非常需要低 1/f 转角频率。振荡器通常根据相位噪声来指定,但要将相位噪声与 ADC 性能联系起来,必须将相位噪声转换为抖动。为了使图 4 中的图表与现代 ADC 应用相关,出于讨论目的选择振荡器频率(采样频率)为 100 MHz,典型图表如图 4 所示。请注意,相位噪声曲线近似于几个单独的线段,每个线段的端点由数据点定义。

点击查看完整大小的图片

图 4. 从相位噪声计算抖动。

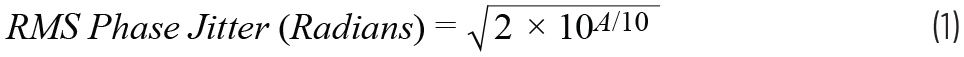

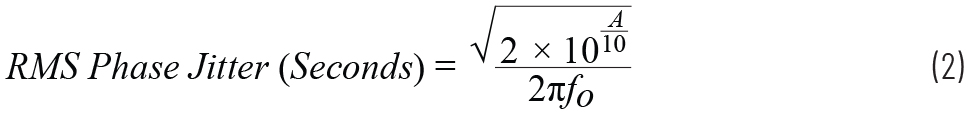

计算等效均方根抖动的第一步是在感兴趣的频率范围内获得积分相位噪声功率,即曲线的面积 A。曲线分为几个单独的区域(A1、A2、A3、和 A4),每个由两个数据点定义。假设振荡器和 ADC 输入之间没有滤波,积分的上限频率范围应该是采样频率的两倍。这近似于 ADC 采样时钟输入的带宽。为积分选择较低的频率也需要一些判断。理论上,它应该尽可能低才能获得真正的 rms 抖动。然而,在实践中,通常不会针对低于 10 Hz 左右的偏移频率给出振荡器规格——但是,这肯定会在计算中给出足够准确的结果。如果该规范可用,则在大多数情况下,100 Hz 的较低积分频率是合理的。否则,使用 1 kHz 或 10 kHz 数据点。还应考虑到近端相位噪声会影响系统的频谱分辨率,而宽带噪声会影响整个系统的 SNR。可能最明智的方法是分别整合每个区域并检查每个区域的抖动贡献幅度。如果使用晶体振荡器,与宽带贡献相比,低频贡献可以忽略不计。其他类型的振荡器可能在低频区域具有显着的抖动贡献,因此必须确定它们对整个系统频率分辨率的重要性。每个单独区域的集成产生单独的功率比。然后将各个功率比相加并转换回 dBc。一旦已知积分相位噪声功率,则以弧度为单位的 rms 相位抖动由下式给出:

除以 2πf 0后,将以弧度为单位的抖动转换为以秒为单位的抖动:

有关详细信息,请参阅“ MT-008 教程:将振荡器相位噪声转换为时间抖动”。

在这个由两部分组成的系列的第二篇文章中,我们通过探索如何量化参考时钟、FPGA、数字隔离和 ADC 孔径中的抖动,以及如何计算整体抖动性能来完成对抖动引入的误差的讨论。

[本文所有图的图片来源均为 Analog Devices。]

审核编辑:汤梓红

-

如何估算采样时钟抖动2012-04-01 2576

-

时钟抖动和相位噪声对采样系统的影响2012-05-08 1642

-

请教大神们,labview数据采集在采样频率边界会发生抖动2026-01-04 510

-

【数据采集分享】数据采集的时间问题2014-12-03 7473

-

【数据采集分享】数据采集采样术语2014-12-09 5468

-

改变数据采集的采样时钟频率,输出的波形频率就变了2015-01-08 3981

-

labview DAQ数据采集时钟的采样率选择2015-04-29 12792

-

在MCU系统中如何利用ADC技术进行数据采集2017-12-19 2524

-

分布式数据采集系统中的时钟同步2009-03-29 2288

-

开源硬件-TIDA-01035-为最大程度提升 SNR 和采样速率而优化抖动的 20 位隔离式数据采集 PCB layout 设计2016-03-31 4384

-

高速ADC在低抖动采样时钟电路设计中的应用2017-11-27 1319

-

如何去正确理解采样时钟抖动(Jitter)对ADC信噪比SNR的影响2021-04-07 10894

-

计算隔离式精密高速DAQ的采样时钟抖动的简单步骤分享2022-11-13 1700

-

计算隔离式精密高速DAQ的采样时钟抖动的简单步骤2023-06-15 1540

-

选择数据采集器时需要考虑的因素2024-11-28 1715

全部0条评论

快来发表一下你的评论吧 !