IBIS的模型结构与文件结构

描述

本人最早接触SI仿真的时候,只是进行一个简单的流程操作,其中涉及到的原理、模型知之甚少,再后来慢慢的接触到了深一点的东西开始自己搭建电路了解到了IBIS。用于电路仿真的模型有好多,可能IBIS是最常用和最方便的一个,一般这个东西都是芯片厂家提供的,其中的一些原理又是一个很复杂的事情。下面简单整理IBIS中的构造:

一 IBIS简介

1.IBIS(Input/Output Buffer Information Specification):输入输出缓冲器,是一个行为级模型,描述的是电压与电流、电压与时间的关系,也是一种基于V/I曲线的对于输入输出端口快速准确建模的方法,是反映芯片驱动和接受电气特性的一种国际标准。

2.IBIS 本身只是一种文件格式,它说明在一标准的IBIS 文件中如何记录一个芯片的驱动器和接收器的不同参数,但并不说明这些被记录的参数如何使用,这些参数需要由使用IBIS 模型的仿真工具来读取。

二 IBIS模型结构

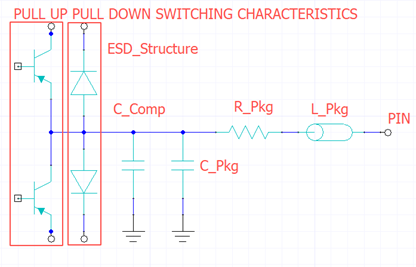

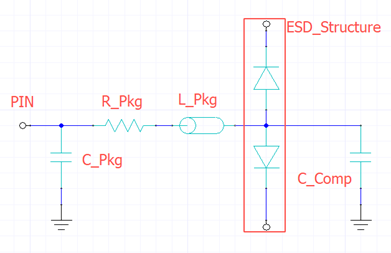

IBIS的模型结构分为输入和输出,如下图:

1.输出结构:包含一个PMOS、一个NMOS、两个ESD保护二极管、芯片的电容和封装寄生参数

C_PKGR_PKGL_PKG是整个芯片的等效电容、电阻、电感特性

C_Comp为硅片上脚的压焊盘电容 (结电容)。

2.输入结构:包含两个ESD保护二极管、芯片的电容和封装寄生参数

C_PKGR_PKGL_PKG是整个芯片的等效电容、电阻、电感特性

C_Comp为硅片上脚的压焊盘电容 (结电容)。

三 IBIS文件结构

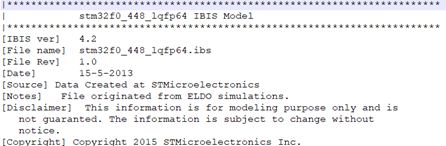

1.头文件

这部分包含了IBIS的版本、文件名、版权等信息,如下图:是下载于ST官网的STM的IBIS模型的头文件:

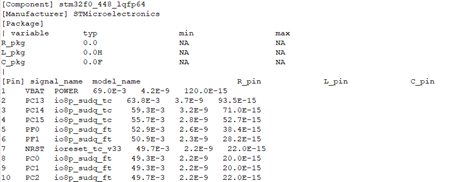

2.器件描述

包含器件模型名称、器件名称、厂商、封装和引脚等信息,如下图:

3.模型描述

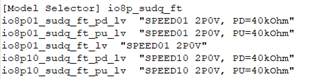

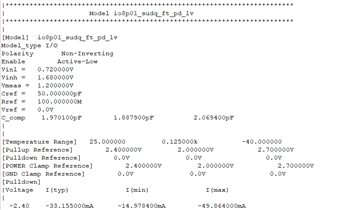

这部门定义了模型对应的缓冲器类型、Pulldown、Pullup、 Power_Clamp、Gnd_Clamp的IlV数据表;Ramp数据;描述波形上升/下降沿的VIT数据表等,如下图:

四 IBIS在信号完整性中的应用

IBIS在信号完整性仿真中有不可或缺的作用,它可以作为一个源端和接收端。它可以被大数的EDA软件识别,并且在有些仿真的软件中没有IBIS模型,是不能进行时域仿真的。在IBIS模型的基础之上,我们可以分析传输线上的信号完整性问题,包括源端到负载端的阻抗、串扰、反射、时延等时域问题。

IBIS模型会把每个I/O或pin分为几种状态(输入、输出、浮空),把这几种状态配置成几种模型,通过调用I/O或pin的几种模型来模拟输入输出。

审核编辑:汤梓红

-

IBIS模型如何导入到LTspice中?2024-01-03 1356

-

请问如何获得AD8000的IBIS模型?2025-03-24 2110

-

IBIS 模型2008-07-30 11677

-

IBIS模型2013-11-06 2885

-

请问有人知道IBIS模型怎么使用吗?2017-02-13 16233

-

跪求ibis仿真模型2017-12-06 4904

-

高速互连IBIS仿真模型概述2018-09-03 2970

-

哪里可以找到IBIS模型?2019-07-19 5328

-

如何将CML逻辑添加到IBIS模型中?2020-04-13 1899

-

CH569/565能提供仿真文件IBIS模型吗?2022-06-15 835

-

MPOA的模型结构,MPOA的模型结构是什么?2010-04-07 712

-

Vivado IBIS模型创建及导出方式2020-12-31 8616

-

AN-715: 走近IBIS模型:什么是IBIS模型?它们是如何生成的?2021-03-21 1336

-

初识IBIS模型2023-07-14 4145

-

IBIS模型入门介绍2023-09-28 6339

全部0条评论

快来发表一下你的评论吧 !