跨时钟域信号处理问题

描述

跨时钟域(Clock Domain Crossing,CDC)信号处理问题,首先要考虑的就是亚稳态。

1.亚稳态

亚稳态是指在设计的正常运行过程中,信号在一定时间内不能到达稳定的0或者1的现象。

在多时钟设计中,亚稳态是不可避免的,可以减少亚稳态的发生和传播,消除亚稳态的有害影响。

为什么会产生亚稳态?

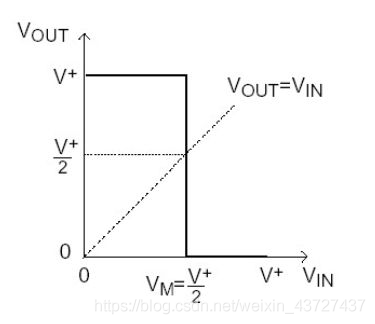

存储元件,如交叉耦合反相器、SR锁存器、D锁存器和D触发器等都有两个稳定的状态,即0和1,也就是能存储0和1这两个状态。亚稳态就是既不是0又不是1的状态。在分析元器件时,把器件抽象为理想器件以简化分析,但实际的元器件并不是理想的,一个理想的CMOS反相器的电平传输特性如下所示:

理想的CMOS反相器件的电平传输特性:

在0 < VIN < VM时,VOUT= V+

在VM < VIN < V+时,VOUT=0

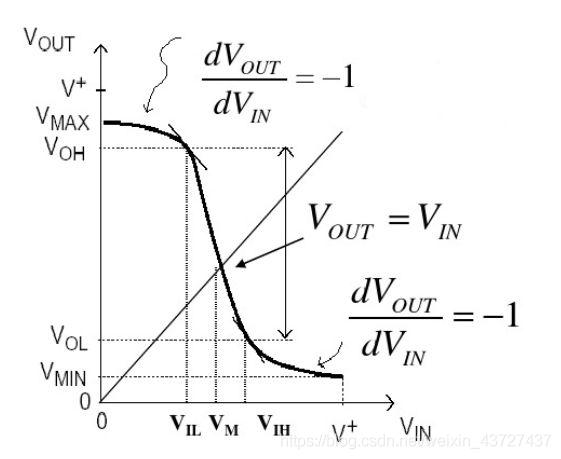

刚好在VM这个点就能完成“突变”,界限明确。实际上变化时一个过程的。实际的CMOS反相器电平传输特性如下:

在0 < VIN < VIL时,VOH < VOUT < VMAX

在VIH < VIN < V+时,Vmin < VOUT < VOL

在VIL

如果在后一级的判断电路把低于VOL电压判断为0,把高于VOH的电压判断为1,那么在输入VIL–VLH这个范围的电压产生的VOUT后一级电路就不能判断当前是0还是1,有可能是0,有可能是1,不能准确预测它的输出。

实际情况下,没有一个点来作为分界线,实际电路做不出来。实际上是高于VH才算1,低于VL才算0,VH>VL,也就是说高阈值VH和VL之间是由一段距离的。

当输入数据不满足寄存器的建立时间和保持时间的时候,寄存器很可能捕捉到输入数据的电平在未定义的电平区间,就是亚稳态。

不是每个违反寄存器建立时间和保持时间的信号翻转都会导致亚稳态。一个寄存器进入亚稳态和从亚稳态进入稳态的时间依赖与制造商的制造工艺和使用环境。大部分情况下,寄存器会很快的进入一个定义的稳态中。

亚稳态的危害

由于亚稳态的输出在稳定下来之前可能是毛刺、振荡、固定的某一电压值,因此亚稳态除了导致逻辑误判之外,输出在0~1之间的中间电压值还会使下一级产生亚稳态(导致亚稳态的传播)。逻辑误判有可能通过电路的特殊设计减轻危害,亚稳态的传播扩大了故障面,难以处理。

电平信号的逻辑误判一般只会对电路造成几个时钟的延时,后面还会稳定在需要的电平,不会造成逻辑错误。

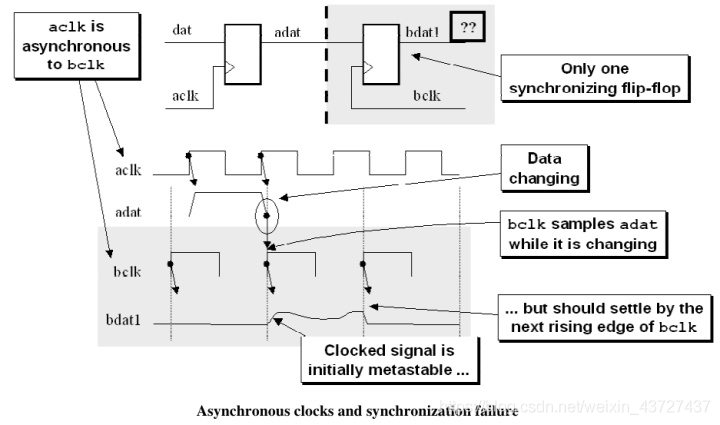

亚稳态信号的稳定时间通常比一个时钟周期要短的多。一般情况下不会超过一个或者两个周期,取决于触发器的性能。

如果亚稳态超过一个或者两个周期,那么就会被下一个触发器采样到,这样就会造成亚稳态的传播。

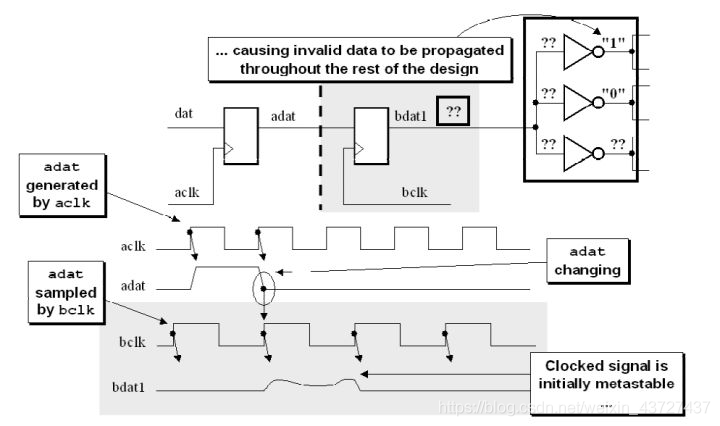

上图的bdat1的亚稳态在下一个时钟沿还没稳定,就造成了亚稳态的传播。这里可以选择更快的触发器,减少亚稳态收敛的时间。

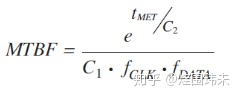

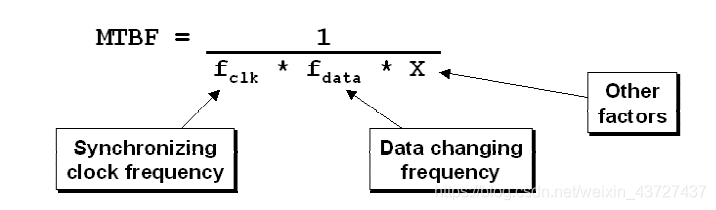

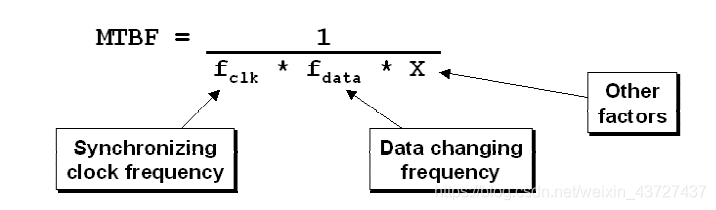

亚稳态的量化公式

设计人员采用平均故障间隔时间(MTBF:mean-time-between-failure)这个指标来估算从问题出现并导致故障的两个事件间的平均时间。MTBF越高,说明设计的稳定性越好。如果发生了故障,只是说明没有解决亚稳态的问题,并不是系统本身真的出现了问题。

C1和C2代表器件的相关的常数,器件的建立时间和保持时间越小,C2越小,MTBF就越大。所以可以通过更快的触发器,来减少亚稳态发生的概率。

数据变化频率越小,采样时钟越低,MTBF越大。

减少亚稳态的方法

亚稳态是不可避免的,是器件的固有属性。可以减少亚稳态的发生和传播,避免亚稳态带来的消极影响。

减少亚稳态的方法有以下几种:

(1)使用同步器:比如常用的2级或者多级FF打拍的方法

(2)降低频率:如果能满足功能要求,降低频率能够减少亚稳态的发生。

(3)避免变化过快或者过于频繁的信号进行跨时钟采样。

(4)采用更快的触发器:更快的触发器,也可以亚稳态的产生

同步器

信号跨时钟边界,一般有两种场景:

(1)信号跨时钟边界,可以漏掉某些值

(2)信号跨时钟边界,不能漏掉任何值

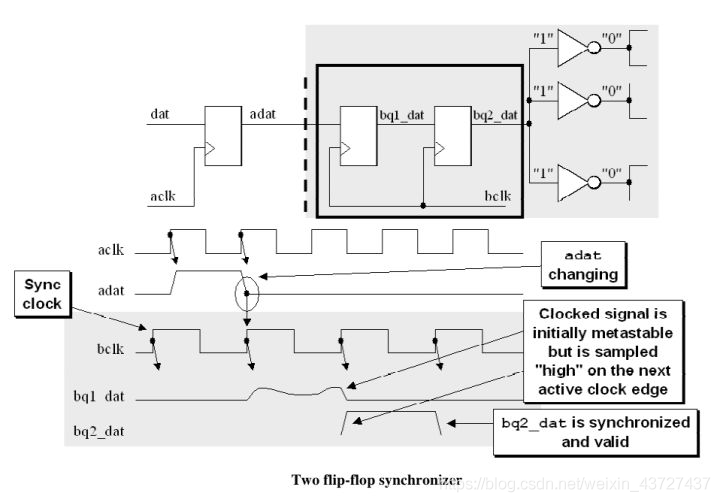

两级触发同步器

(1)如果亚稳态维持的时间不止一个周期,在下一个时钟上升沿没有稳定,那么第二级的FF也会进入亚稳态,这种情况的概率是1/MTBF

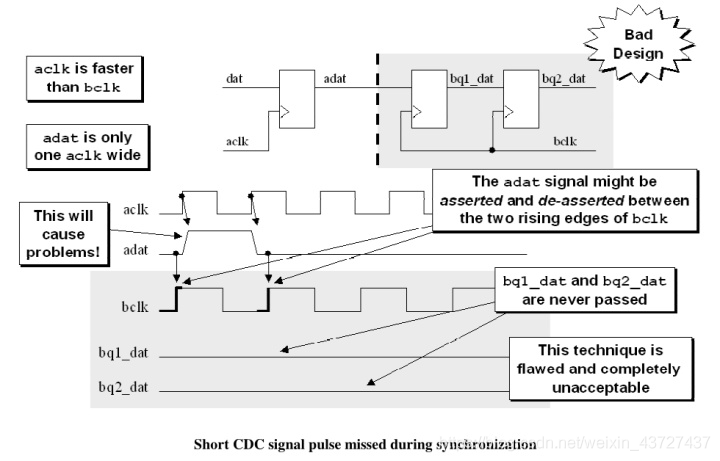

(2)第一级亚稳态在下一个时钟上升沿稳定,但是被是识别为0,那么第二级的FF输出bq2_dat就是0,说明信号跨时钟采样失败。但是这种情况不会造成亚稳态的传播,也就是不会影响后面的设计。针对这种情况,一般会改变设计,不会让快时钟域的单cycle脉冲,跨时钟到慢的时钟内采样。

三级或多级同步器

在高速、超高速设计中,两级的MTBF可能还不够,为了保险会采样三级或多级同步器。

3级FF的MTBF是2级FF的MTBF的7倍。

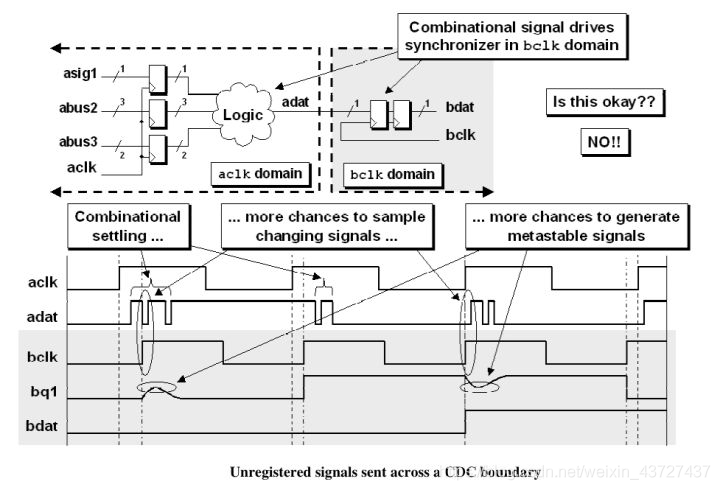

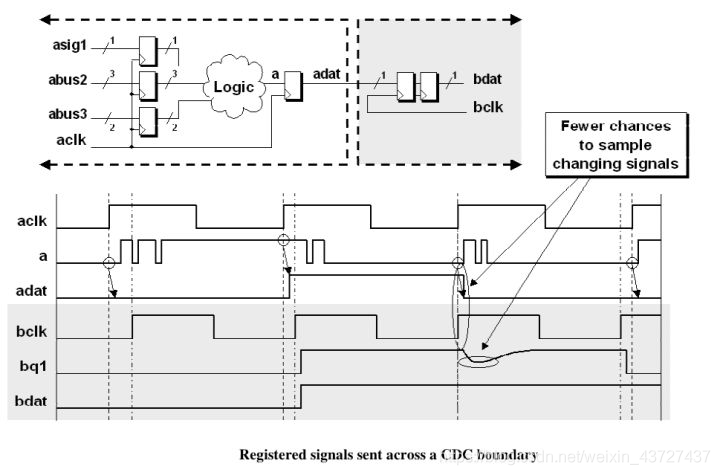

同步器的输入:源时钟寄存

采用同步器的另外一个要求:通常,需要跨时钟的信号,需要在源时钟经过一级FF进行寄存输出。即,跨时钟信号必须是寄存器的输出,中间不能有组合逻辑。如果输入不是寄存器的输出,是组合逻辑的输出,会是如下情况:

可以看到,adat是组合逻辑的输出,变化的频率更快了,根据MTBF公式:

数据变化太快,会减少MTBF,增加亚稳态发生的概率。如果adat是FF的输出,根据FF的特性,输出在一个时钟周期内是不会改变的,数据的变化频率不会超过时钟频率,这样就能降低跨时钟信号变化的频率,减少亚稳态发生的概率:

在使用同步信号时,要求理解了其中的原理,要求输入信号必须是源时钟域的寄存器输出。

2. 跨时钟信号处理方法

跨时钟域的信号可以分为单bit信号和多bit信号。

单bit信号跨时钟域的处理

信号跨时钟域,根据两个异步时钟之间的关系可以分为:

(1)信号从快时钟域到慢时钟域

(2)信号从慢时钟域到快时钟域

单bit信号一般采用同步器来做CDC(clock domain crossing)。由于在CDC时,会在源时钟域做寄存器输出,所以信号的变化频率不会超过源时钟的频率,所以这里可用两个时钟间的快慢来分类。

快时钟域到慢时钟域

信号从快时钟域到慢时钟域CDC如下图所示:

当在aclk中生成的信号adat被送到了另一个时钟域bclk中采样,由于采样时间太靠近第二个时钟的上升沿,发生的同步失败。同步失败是由于输出bdat1变为亚稳态,而在bdat1再次被采样时没有收敛到合法的稳定状态。

如果是电平信号进行CDC,不用考虑时钟快慢,直接用同步器就可以,因为总能被采样到。

快时钟到慢时钟的(单bit)信号处理,主要问题是信号在快时钟域中,可能会多次改变,这样慢是可能来不及采样导致数据丢失。这个问题被称为信号宽度问题,在CDC检查工具中,如果快时钟的信号宽度不足,就会报出CDC违例。

快时钟到慢时钟的(单bit)信号处理分为两种:

(1)采样丢失是被允许的。单bit信号一般不会是这种情况,如果是,直接用同步器同步就行。

(2)采样丢失不被允许。这样就用其他手段来保证数据不丢失。主要原理是保证快时钟与的信号宽度满足一定的条件,使得慢时钟域有足够时间采样到。

信号宽度的“三时钟沿”要求

比较安全的宽度是,快时钟域的信号宽度必须是慢时钟域周期的1.5倍以上。也就是要持续3个时钟沿以上(上升沿和下降沿都算)。这个被称为“三时钟沿”要求。

下面是一个CDC信号只持续一个周期的例子:

发送时钟域的频率高于接收时钟域,而CDC脉冲在发送时钟域只有一个周期宽,这样CDC信号可以在慢时钟上升沿之间变动,不会被捕获到慢时钟域。

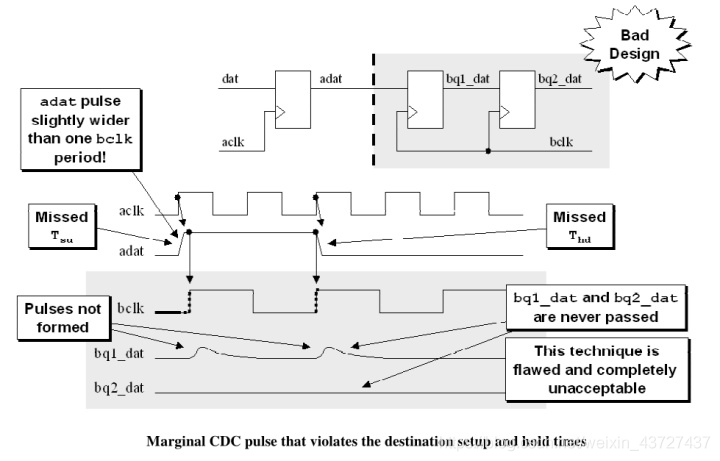

如果CDC信号宽度超过慢时钟周期,但是不足1.5个周期,也会发生问题。

如上图所示,信号宽度超过了一个慢时钟周期,但是可能会setup和hold time违例,导致信号采样失败。

信号宽度问题的解决方法:

通过保证信号宽度满足超过慢时钟周期的1.5倍,来解决这个问题,这是最直接,也是跨时钟最快的方法。可以通过system verilog加“断言”的方式来检测是否满足条件。

但实际中很少用这种方法,因为设计可能会变,设计人员在改变设计时,可能会忘记这个限制。

所以,通常还是通过“握手”的方式来保证数据被采样到。

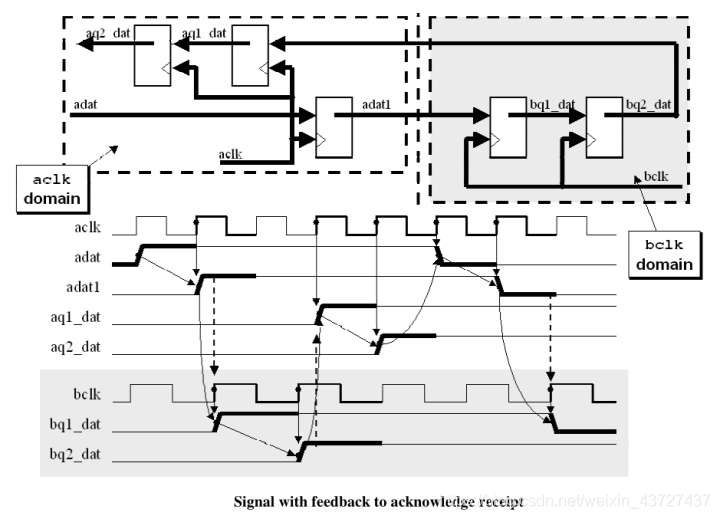

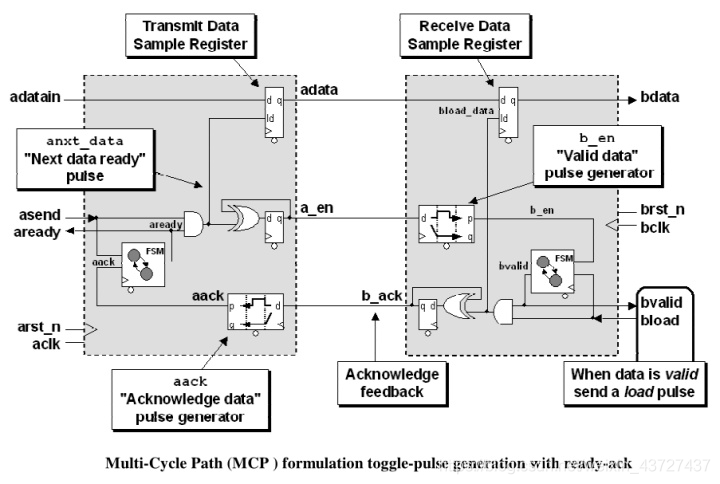

通常的做法是:发送一个使能控制限号,将它同步到新的时钟域,然后通过另一个同步器将同步信号作为确认信号作为确认信号传回发送时钟域,如下图所示:

优点:

同步反馈信号是一种非常安全的技术,可以识别第一个控制信号并将其采样到新的时钟域中。

缺点:

在允许控制信号改变之前,在两个方向上同步控制信号有相当大的延迟。也就是时候,在应答信号到来之前,是不允许源信号改变的。

在实际的芯片设计中,脉冲(宽度有限)信号的同步都是采用这种握手机制来处理。

慢时钟到快时钟域

慢时钟域到快时钟域的CDC,直接使用信号同步器就可以了。

目标时钟频率必须是源时钟频率1.5倍或者以上,才能算慢时钟到快时钟的CDC。

只有满足快1.5倍以上,才能满足“三时钟沿要求”。才能保证快时钟域能够采样到慢时钟域的脉冲。

如果目标时钟域只快一点,为保险起见,还是用握手机制。

有的设计中为了保险和以后修改的方便,或者不清楚时钟之间的关系,都会按照握手机制来处理。

多个信号跨时钟的处理

不同同步器的芯片上的走线也可能不同,导致延时不一样。会导致后端走线难度增大。

在CDC检查的时候,会有专门的规则来检查是否采样了多bit信号用同步器聚合使用的情况。

多个信号CDC策略可以分为以下几种:

(1)多个信号合并,在可能的情况下,将多个CDC合并为1位的CDC信号

(2)多周期路径发。使用同步负载信号安全地传递多个CDC位。

(3)使用格雷码传递多个CDC位。

(4)使用异步FIFO来传递多位信号

(5)使用DMUX电路结构进行多位信号传递

多个信号合并

有时候并不需要将多个信号做CDC。下面是将两个信号合并为1位信号做CDC。

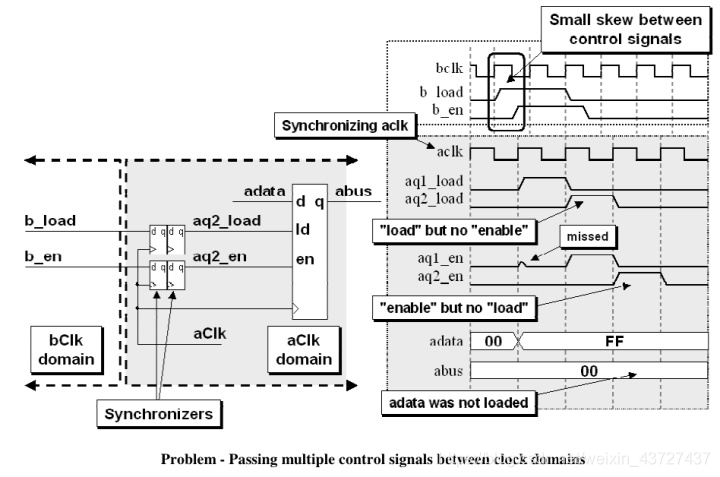

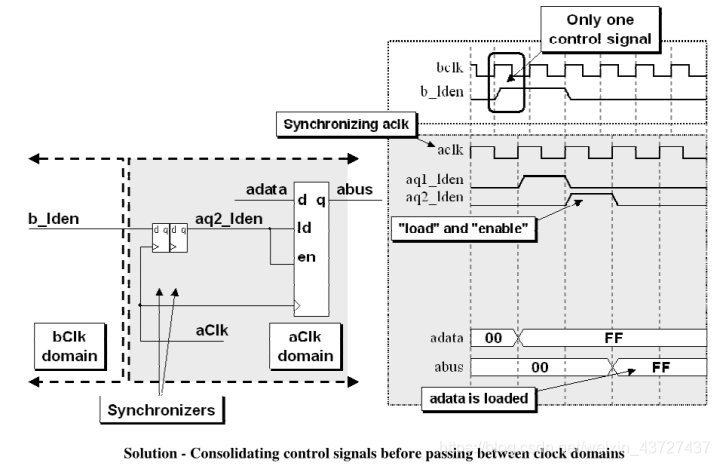

下图中,接收时钟域中的寄存器需要加载信号和使能信号崔你那个将数据值加载到急促器中。如果负载和使能信号都是在同一个发送时钟边缘上驱动的。那么控制信号之间的小偏差就有可能导致两个信号在接收时钟域中同步到不同的时钟周期。在这种情下,数据不会被加载到寄存器中,就会出问题。

解决方法是,将控制吸纳后b_load和b_en合起来;b_lden = b_load & b_en同步到aclk时钟域中。

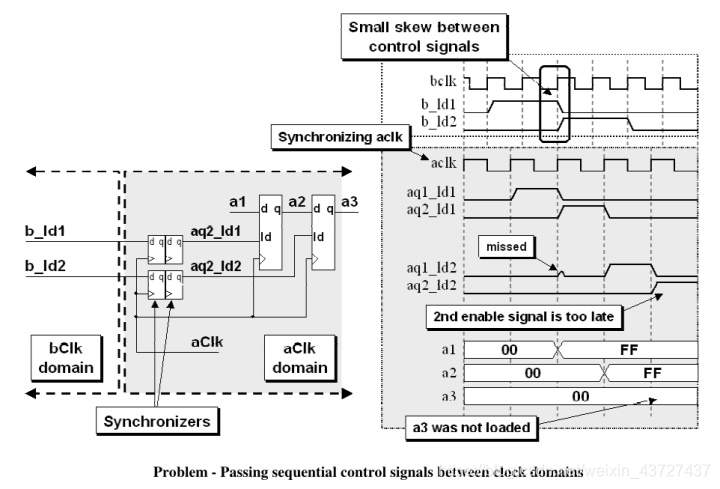

下面这个例子中,显示了两个使能信号,aen1和aen2,它们从发送时钟域依次驱动到接收时钟域,以控制流水线数据寄存器的使能输入。问题是同步器并不能保证两个cycle一定能同步过来,下面的同步器花了3个cycle才tongue完成数据,导致流水线寄存器不能“流水”起来。

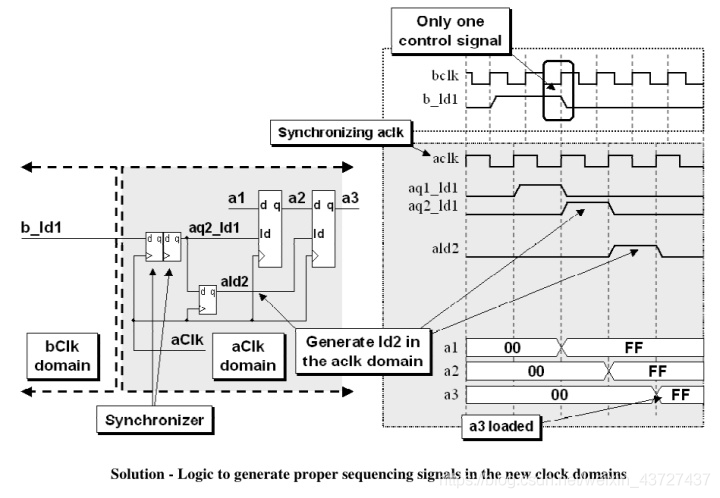

该问题的解决方案是只向接收时钟域发送一个控制信号,并在接收时钟域内生成第二个相移流水线使能信号。

多周期路径(Multi-Cycle Path,MCP)

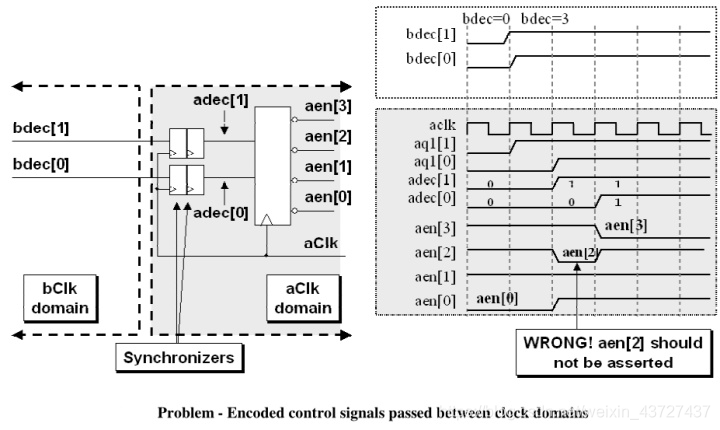

下图显示在时钟域之间传递两个编码控制信号。如果这两个编码信号在采样时略有偏差,则在接收时钟域中的一个时钟周期内可能会产生错误的解码输出。

多位数据问题可以用“多周期路径法(MCP)”来解决。

MCP方法是指直接不同步将数据发生到目标时钟域,但是同时送一个同步过的控制信号到目标时钟域。数据和控制信同时发送,允许数据在目标寄存器的输入端进行设置,同时控制信号在到达目标寄存器的负载输入端之前做同步。

MCP优点:

(1)不需要在发送时钟域计算适当的脉冲宽度

(2)发送时钟域只需要将enable toggle到接收时钟域,表示数据已经被传递完成,已经准备好被加载,使能吸纳后不需要返回到初始逻辑电平。

MCP方法的实质是,不同步多位的数据,只同步一位的控制信号,通过握手保证控制信号能够正确传输,然后在目标时钟域通过控制信号来采样数据。

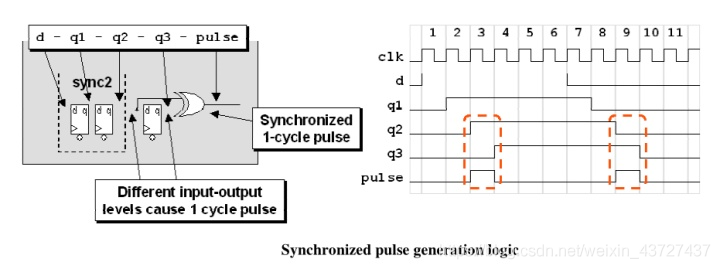

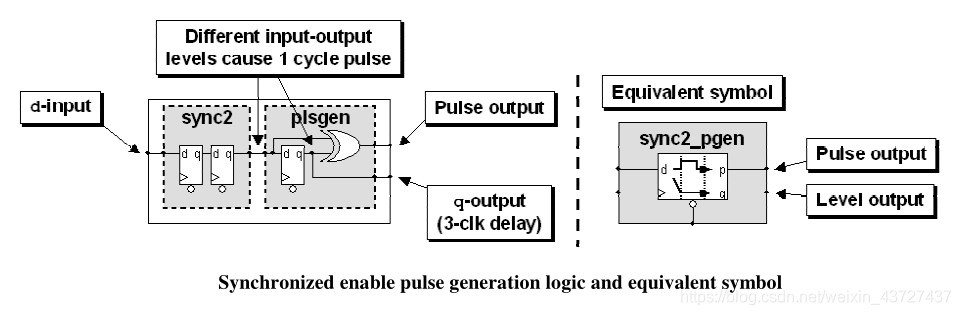

MCP需要用到“同步脉冲器”:

同步脉冲器的符号表示如下:

多周期路径法有两种方法来传递多位信号:

多周期路径法的思想十分有用,但是实际中用来传递多位信号比较少见,因为逻辑过于复杂。但是MCP方法用来传递单bit的信号却十分有用。

格雷码

对于计数器的CDC,大部分是不需要的,如果需要,那就使用格雷码。

格雷码每次只允许更改一个位,从而消除了跨时钟域同步更改多个CDC位所带来的问题。

需要注意的是:格雷码必须是计数到2^n才是每次改变一个bit。

如果计数器是从0-5计数,那么从5–0的计数就不止一个bit改变,就失去了只改变一个bit的初衷。

格雷码最常见的应用是在异步fifo中,通常异步fifo的深度都是2^N。原因如上,就算浪费面积,也需要把FIFO深度设置为2 ^ N.

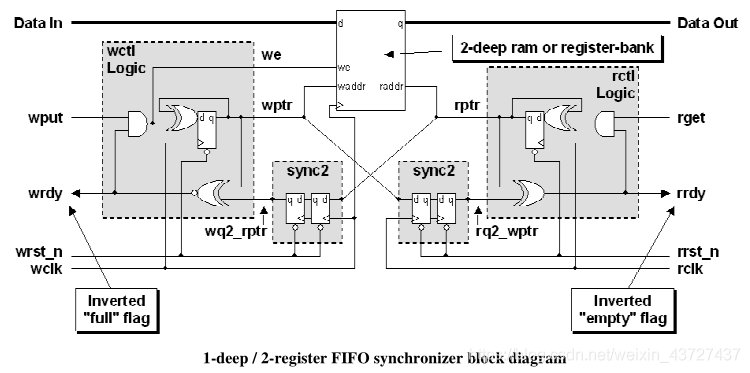

异步FIFO(AFIFO)

就是深度为2的AFIFO,来进行多bit数据的CDC. 如下图所示:

2个寄存器搭建的AFIFO,地址只需要一位。相比MCP方法,逻辑简单,可以复用AFIFO代码(一般公司都有芯片验证过的AFIFO代码),而且延时也比MCP方法小。

DMUX(数据分配器)

有一个输入端和多个输出端1,其逻辑功能是一个输入端的信号发送到多个输出端中某一个,简称DMUX,作用与MUX正好相反。

3.SpyGlass CDC流程

数字电路的集成度越来越高,设计也就越复杂。系统很少都只工作在一个时钟频率之下。一个系统中往往会存在多个时钟,这些时钟之间有可能是同步的,也有可能是异步的。一个系统中,异步时钟之间存在信号通道,则就会存在CDC(clock domain crossign)。

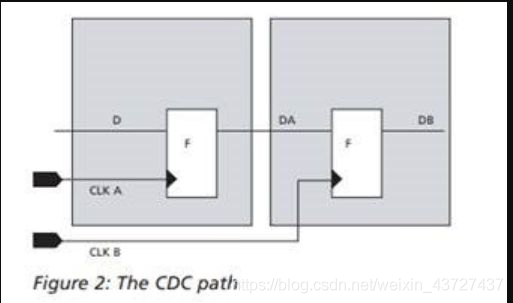

下图中,CLKA和CLKB之间没有固定的相位关系,是异步时钟。前半部分设计属于时钟域CLKA,后半部分设计属于时钟域CLKB。DA信号从时钟域CLKA进入到时钟域CLKB,是一个跨时钟域的信号,这条路径被称为CDC path。

CDC(Clock Domain Crossing)是前端设计中最常见的问题。在RTL中要恰当的处理每个异步的控制信号和数据信号,否则就会出现亚稳态,造成严重的function false。

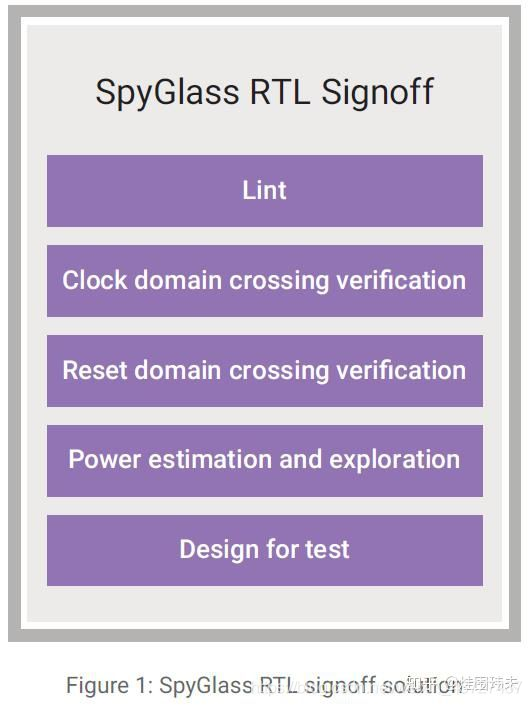

SpyGalss是目前业界唯一可靠的RTL Sign off解决方案,可以帮助客户在设计早起发现潜在问题,保住产品质量,极大的减少设计风险,降低设计成本。

包括五大模块:lint,CDC(跨时钟域检查),LP(低功耗),Constraint(约束),DFT(可测试性)。

SpyGlass CDC分析使你能够识别设计中的CDC问题。SpyGlass CDC tool是中Formal Check Methodology工具,相比写case跑仿真来找CDC问题,靠SpyGlass能更早,更全,更快的发现CDC问题。它能够:

(1)管理是多时钟域设计

(2)系统地处理CDC问题

(3)检查和报告任何不同步的信号:时钟和复位

SpyGlass CDC与静态时序分析相比:

(1)STA对async interface不太好使,只适合sync模块分析

(2)CDC paths总是需要设置成false paths

(3)一般在design的后期能在netlist level做才有意义

SpyGlass CDC与功能仿真相比:

(1)黑盒测试很难穷举

(2)白盒测试需要assertions

(3)需要覆盖CDC的所有test branches

(4)很难幸运的覆盖所有,一般只能发现部分问题

(5)一般在design后期才发现问题

当soc design设计的clock domain太多,用到很多第三方IP,及设计人员水平参差不齐时,用SpyGlass CDC来检查保证RTL质量是十分必要的。

在工程的block-level和SOC集成的两个不同阶段,所用的CDC Goal也是有所不同的。Block-level关心的是模块内部,只有模块内部检查没问题后才能做deliver,而SOC集成主要关心的是模块间interface 的CDC问题。

审核编辑 :李倩

-

如何处理好FPGA设计中跨时钟域间的数据2021-07-29 0

-

看看Stream信号里是如何做跨时钟域握手的2022-07-07 0

-

跨时钟域信号的几种同步方法研究2012-05-09 1077

-

揭秘FPGA跨时钟域处理的三大方法2022-12-05 1603

-

CDC单bit脉冲跨时钟域的处理介绍2021-03-22 3454

-

如何解决单bit和多bit跨时钟处理问题?2021-03-22 6740

-

总线半握手跨时钟域处理2021-04-04 2789

-

介绍3种方法跨时钟域处理方法2021-09-18 22215

-

基于FPGA的跨时钟域信号处理——MCU2021-11-01 485

-

全面解析跨时钟域信号处理问题2022-07-21 966

-

关于跨时钟域信号的处理方法2022-10-09 5922

-

三种跨时钟域处理的方法2022-10-18 7507

-

FPGA跨时钟域处理方法(二)2023-05-25 969

-

从处理单bit跨时钟域信号同步问题来入手2023-06-27 1559

-

如何处理跨时钟域这些基础问题2024-01-08 571

全部0条评论

快来发表一下你的评论吧 !