带有时钟使能和同步清零的D触发器

接口/时钟/PLL

49人已加入

描述

每个 Slice 有 8 个 FF 。四个可以配置为 D 型触发器或电平敏感锁存器,另外四个只能配置为 D 型触发器,但是需要记得是:当原来的四个 FF 配置为锁存器时,不能使用这四个 FF 。

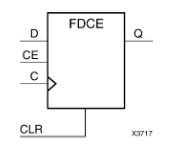

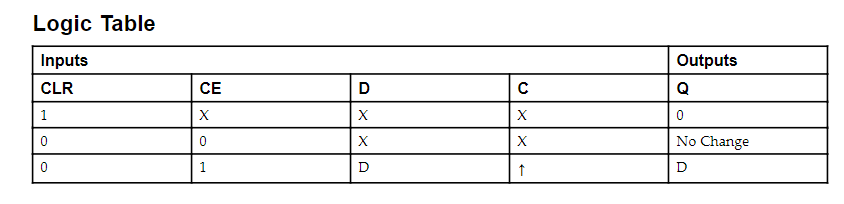

FDCE

简介

带有时钟使能和异步清零的 D 触发器

当时钟使能(CE)为高并且异步清零信号 CLR 为低时,该 D 触发器将数据输入 D 端传递到输出 Q 端。

当CLR为高,不管输入是什么,输出 Q 端值为 0。

原语

FDCE #(.INIT(1'b0) // Initial value of register (1'b0 or 1'b1)) FDCE_inst (.Q(Q), // 1-bit Data output.C(C), // 1-bit Clock input.CE(CE), // 1-bit Clock enable input.CLR(CLR), // 1-bit Asynchronous clear input.D(D) // 1-bit Data input);

真值表

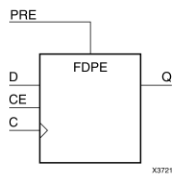

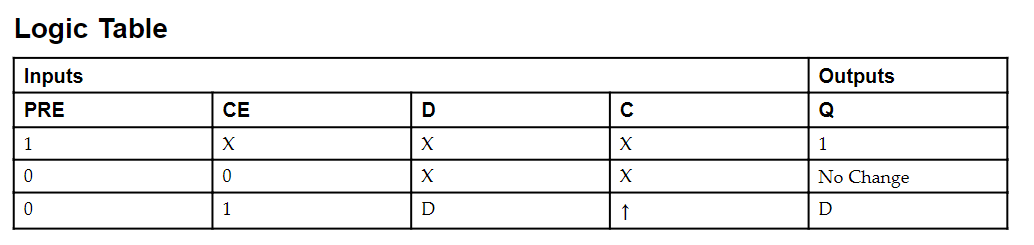

FDPE

简介

带有时钟使能和异步置位的 D 触发器

当时钟使能(CE)为高并且异步置位信号 PRE 为低时,该 D 触发器将数据输入 D 端传递到输出 Q 端。

当 PRE 为高,不管输入是什么,输出 Q 端值为 1。

原语

FDPE #( .INIT(1'b0) // Initial value of register (1'b0 or 1'b1)) FDPE_inst ( .Q(Q), // 1-bit Data output .C(C), // 1-bit Clock input .CE(CE), // 1-bit Clock enable input .PRE(PRE), // 1-bit Asynchronous preset input .D(D) // 1-bit Data input);

真值表

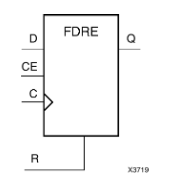

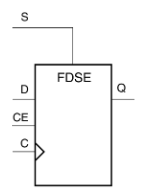

FDRE

简介

带有时钟使能和同步清零的 D 触发器

当时钟使能(CE)为高并且同步清零信号 R 为低时,该 D 触发器在时钟上升沿将数据输入 D 端传递到输出 Q 端。

当 R 为高,不管输入是什么,输出 Q 端值为 0。

原语

FDRE #( .INIT(1'b0) // Initial value of register (1'b0 or 1'b1)) FDRE_inst ( .Q(Q), // 1-bit Data output .C(C), // 1-bit Clock input .CE(CE), // 1-bit Clock enable input .R(R), // 1-bit Synchronous reset input .D(D) // 1-bit Data input);

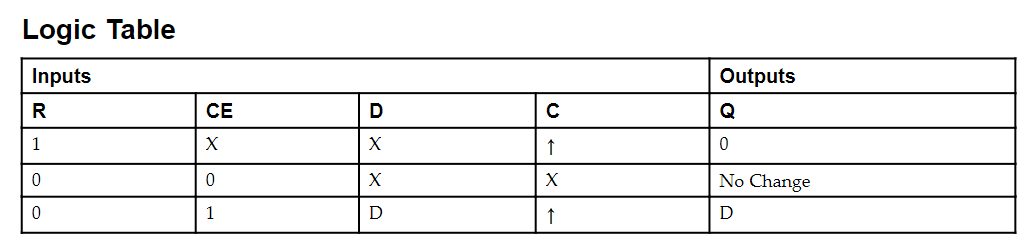

真值表

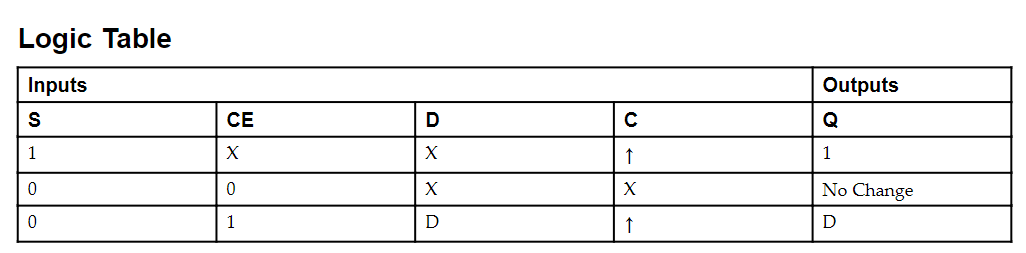

FDSE

简介

带有时钟使能和同步置位的 D 触发器

当时钟使能(CE)为高并且同步置位信号 S 为低时,该 D 触发器在时钟上升沿将数据输入 D 端传递到输出 Q 端。

当 S 为高,不管输入是什么,输出 Q 端值为 1。

原语

FDSE #( .INIT(1'b0) // Initial value of register (1'b0 or 1'b1)) FDSE_inst ( .Q(Q), // 1-bit Data output .C(C), // 1-bit Clock input .CE(CE), // 1-bit Clock enable input .S(S), // 1-bit Synchronous set input .D(D) // 1-bit Data input);

真值表

审核编辑:彭静

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

CDx4HC74 具有清零和预设功能的双路D类正边沿触发的触发器数据表2026-02-09 143

-

74ls163是同步清零吗2024-10-18 4310

-

怎么判断同步清零和异步清零2024-07-23 7771

-

SN74LVC1G175单D型异步清零触发器数据表2024-06-03 553

-

带时钟使能的八边三格D型触发器数据表2024-05-15 410

-

具有清零和预设功能的施密特触发输入双路正边沿触发式D型触发器SN74HCS74数据表2024-05-09 486

-

具有时钟使能端的八路 D 类触发器SNx4HC377数据表2024-05-06 451

-

D触发器的类型详解 同步复位和异步复位D触发器讲解2023-08-31 20865

-

rs触发器和rs锁存器的区别是什么2023-08-28 6704

-

什么是D触发器,D触发器如何工作的?2023-06-29 52277

-

D触发器实现的原理2022-09-19 6919

-

D触发器,CLK突变时,输入D也突变,触发器的输出应该如何判定?2022-01-25 10701

-

简单的verilog设计同步清零触发器求助2015-07-30 12044

-

D触发器2008-10-20 3217

全部0条评论

快来发表一下你的评论吧 !