对 3D 技术前景的看法

电子说

描述

在工业中,我们看到越来越多的系统示例是通过利用 2.5D 或 3D 连接的异构集成来构建的。在本次采访中,imec 高级研究员、研发副总裁兼 3D 系统集成项目总监 Eric Beyne 回顾了趋势并讨论了构建下一代 3D 片上系统所需的技术。各级报告的进展将使系统设计和开发进入下一个层次,有望在系统的功率-性能-面积-成本 (PPAC) 指标方面获得巨大回报。

未来几年哪些主要趋势将标志着您的研究领域?

Eric Beyne:“传统的 CMOS 技术规模化——产生单片 CMOS 单芯片片上系统 (SOC)——将通过技术、材料和器件架构的创新持续到下一个十年。CMOS 缩放越来越多地得到设计-技术-协同优化 (DTCO) 的补充,以提高系统的功率、性能、面积和成本 (PPAC)。但随着成本和技术复杂性的增加,这些方法不再在系统级别提供足够的收益。对于数据密集型高性能应用程序尤其如此,这些应用程序受到所谓的内存墙的挑战——难以足够快地访问数据。

为了进一步优化系统的 PPAC 指标,半导体行业越来越关注多芯片异构集成解决方案。

采用这种方法,可以分别优化芯片上的不同功能(使用不同的(节点)技术),并且可以在系统的子组件之间实现更短、更快的连接。第一个“异构”实现(例如高带宽存储器 (HBM))主要依赖 2.5 或 3D 小芯片方法,涉及单独设计和处理的小芯片裸片。芯片间通信主要使用标准化接口物理层 (PHY) IP 块实现,将应用程序限制为延迟容忍功能,例如最后一级内存缓存。

尽管小芯片方法大大拓宽了异构系统集成的范围,但我们将见证向真正的 3D-SOC 设计的演变,其中不再需要中间接口 PHY 层。这些 3D SOC 将通过巧妙地共同设计不同的 3D 分区和实现直接的 die-to-die 3D 互连来实现。”

imec 正在探索哪些途径来克服未来的挑战?

“实现最佳 3D SOC 需要重新设计系统架构,需要对电子设计自动化 (EDA) 工具进行创新,以便在一个视图中实现不同设备的协同设计。

在这种情况下,imec 与其在 EDA 软件方面的合作伙伴合作,开发用于自动网表分区和 3D 路径优化的解决方案。在这种情况下,我们最近报道了一种新的 3D 设计流程——与 Cadence 合作开发。该软件有助于预测所提议的 3D 分区是否会产生强大且功能齐全的 3D SOC,从而使异构集成更接近工业现实。

其他贡献来自 3D 集成技术开发——这是 3D SOC 的关键推动力。与我们的材料和设备供应商一起,我们开发了多种 3D 互连技术,涵盖从毫米(封装堆叠)到小于 100 纳米(晶体管堆叠)的各种互连间距。我们开发了高效的冷却解决方案(例如基于冲击的冷却),以更有效地处理日益密集的高性能片上系统中不断增加的功率。”

还有其他值得一提的技术发展吗?

“背面供电 (BSPD) 是另一项很有前途的技术开发,可帮助实现高性能应用的 3D SOC。

在 BSPD 网络 (BSPDN) 中,电源传输和电源转换从逻辑芯片的正面移到其背面 - 到目前为止,它仅用作载体。因此,可以通过变薄的背面直接向先进的微处理器核心芯片供电,而无需通过电阻较高的正面。这可以放宽对高级 IC 系统电源的要求,该系统越来越受到功率密度、缩放晶体管的较低电源电压(因此,更大的电流)以及激进的 IR 压降的挑战。我们的一位合作伙伴最近宣布,它将在其未来的技术节点芯片之一中实施 BSPDN 概念。

我们现在可以设想一个多核处理器,它由一个内存缓存晶片组成,堆叠在一个先进的微处理器核心逻辑晶片的顶部,使用细间距晶片对晶片键合。电源通过 BSPDN 直接提供给核心逻辑晶体管。这种逻辑存储器结构随后可以堆叠到包含内部和外部互连的第三个芯片上——使用旧的技术节点进行优化。”

我们在实现后端供电网络方面取得了哪些进展?

“为了实现 BSPDN,需要一种专用的晶圆减薄工艺(低至几 100 纳米),以及处理将器件晶圆背面电连接到正面的纳米硅通孔 (n-TSV) 的能力。 . n-TSV 可以降落在第一个正面金属上,也可以降落在晶圆正面的埋入式电源轨 (BPR) 上。

Imec 在其 3D 集成计划的框架内开发这些流程。我们所谓的 n-TSV-last 方法包括使用低温晶圆对晶圆键合技术将第一个晶圆(包括晶体管)的“有源”正面键合到第二个载体晶圆。第一个晶圆的背面被减薄,通过n-TSV图案化和钨填充以及背面金属化完成该工艺。

其中一个挑战与晶圆键合工艺有关,该工艺固有地会引起第一片晶圆的变形。这对图案化 n-TSV 所需的背面光刻步骤提出了挑战,尤其是达到与逻辑标准单元结构相匹配的所需对准精度的能力。Imec 及其合作伙伴开发了替代方法,以实现更好的叠加精度并改进 BSPDN。”

您能否详细介绍一下imec 的3D 集成技术对行业的附加价值?

“今天,一些商业 '3D' 产品使用 TSV 和 Sn 微凸块的组合来实现异构裸片到裸片或裸片到中介层堆叠。虽然研究显示 TSV 微缩的良好前景,但生产中最先进的 Sn 微凸块间距在约 30µm 时已饱和。问题在于互连间隙:芯片到芯片的微凸块连接还没有赶上可以充分利用 TSV 的程度。

在imec,我们正在突破今天可能的界限。我们已经展示了一种基于 Sn 的微凸块互连方法(在凸块金属化下使用大马士革)产生低至 7µm 的互连间距,并制定了将该间距降至 5µm 的路线图。

通过使用我们的 Cu/SiCN 芯片到晶圆混合键合方法,我们可以进一步减小互连间距(低至 3µm)。按照这种方法,芯片使用电介质对电介质键合方法堆叠,然后是金属对金属连接——不使用微凸块。最大的挑战与芯片放置在晶圆上的纯度和精度有关。

使用我们的晶圆对晶圆键合解决方案可以获得最高的互连密度。这些发展是由逻辑存储器堆叠驱动的,需要远低于 1µm 的互连间距。今天,我们获得了 700nm 间距,并希望将其降低到前所未有的 500nm。”

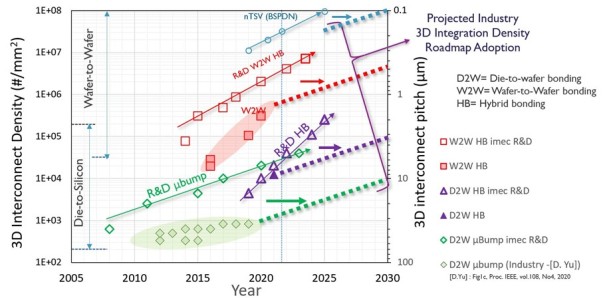

3D 互连 imec 研发路线图

是什么让 imec 的 3D 系统集成计划在全球半导体行业中独树一帜?

“Imec 提出了不同 3D 集成技术的行业路线图,其 3D 互连密度的范围接近 8 个数量级。这些 3D 集成技术中的每一种都满足不同的需求,因此针对不同的终端应用,例如智能手机、DRAM 芯片或高性能计算系统。最佳选择是在层次驱动的 3D 互连密度和最终解决方案的成本之间进行权衡。

为了在系统级别获得尽可能多的好处,我们不断突破各种选项的界限。为此,我们与我们的设备、计量和材料供应商密切合作,并得到 EDA 软件开发商和针对不同终端应用的公司的支持。这种独特的合作伙伴生态系统使我们能够加速真正的 3D SOC 的开发,并在系统级别获得最佳的 PPAC 增益。

审核编辑 黄昊宇

-

3D打印技术强势进军医疗APP?时辰未到!2012-12-08 8092

-

3d全息声音技术解析2013-04-16 2888

-

什么叫3D微波技术2019-07-02 1361

-

基于3D打印技术的武器装备研制2019-07-16 3036

-

3D打印磁体2020-05-27 2373

-

浩辰3D的「3D打印」你会用吗?3D打印教程2021-05-27 8036

-

3D显示技术的原理是什么?有哪些应用?2021-05-31 3146

-

UWB技术前沿2021-07-26 2540

-

解读裸眼3D技术2012-02-28 7353

-

最新裸眼3D技术揭秘2012-08-17 11714

-

3D打印技术是什么?未来3D打印技术对城市空间的影响2017-05-17 2513

-

3D打印技术用于定制美食的前景及潜力2018-11-02 3261

-

铠侠展望3D XPoint前景,3D NAND技术成熟占据主导2020-01-02 5226

-

3D视觉技术广阔的应用前景2024-07-29 848

-

技术前沿:半导体先进封装从2D到3D的关键2025-01-07 3204

全部0条评论

快来发表一下你的评论吧 !