RISC-V的 CPU 验证挑战

电子说

描述

RISC-V 正受到整个半导体行业的关注。它提供了一个开源解决方案的诱惑,任何人都可以利用它来创建自己的 CPU 或自定义加速器。

当然,深入挖掘并出现挑战。RISC-V 是新的,还没有多年现场验证经验的好处。这意味着精心选择和执行的 CPU 验证策略至关重要。这也意味着“黄金参考模型”的可用性是必须保护的关键组件。如果没有已知的良好参考,就不可能对验证结果有信心。拥有自定义指令集模拟器 (ISS) 对成功至关重要。

CPU 设计和相关指令集架构 (ISA) 的正确验证是 CPU 核心工程组必须解决的最具挑战性的活动之一。与固定功能设计或模块不同,CPU 是可编程的,旨在执行许多不同的任务。最终,它是由其 ISA 的广度和深度以及程序员利用 ISA 的不同方式来定义的。即使使用超级计算机,考虑到指令、内存利用率、数据模式等的所有组合,实现对 CPU 的 100% 验证也需要数千年的时间。

相反,CPU 验证小组必须更聪明地工作,并专注于进行“足够”的验证以发现最有可能出现的问题。“足够”的定义基于特定的 CPU 和 ISA 变化——例如广泛的功能集与狭窄的集中集——以及可能是安全关键或通用的最终应用程序市场,例如。

大型处理器公司花费数年时间和数亿美元为其特定处理器和指令集开发验证流程和方法。他们从时间和经验中受益,即便如此,多年来的显着问题表明,针对每种可能的情况验证 CPU 设计是多么困难。

在构建用于 CPU 验证的方法、流程和工具集时,RISC-V 设计和验证小组有很多选择。例如,一些团体可能更喜欢基于经验的 Accellera 通用验证方法 (UVM) 标准,而另一些团体可能更喜欢 C。任何一种方法都是合适的。

同样,在模拟平台方面有多种选择,通常根据经验或已经使用的模拟平台做出决定。较新的公司权衡投资于 EDA 行业的事实上的标准模拟器或开源模拟器(如 Verilator)的优缺点。虽然没有任何答案适用于所有情况,但在前进之前就验证环境达成一致是必须的。

该流程的另一个关键组成部分是所选 ISA 的 CPU 参考模型。可能很容易认为它可以在内部开发,这是一个固有的风险提议。开发 CPU 是一项艰巨的任务。最好寻找一个经过验证的外部参考模型,即验证 CPU 和 ISA 所依据的“黄金”标准。

装备验证流程

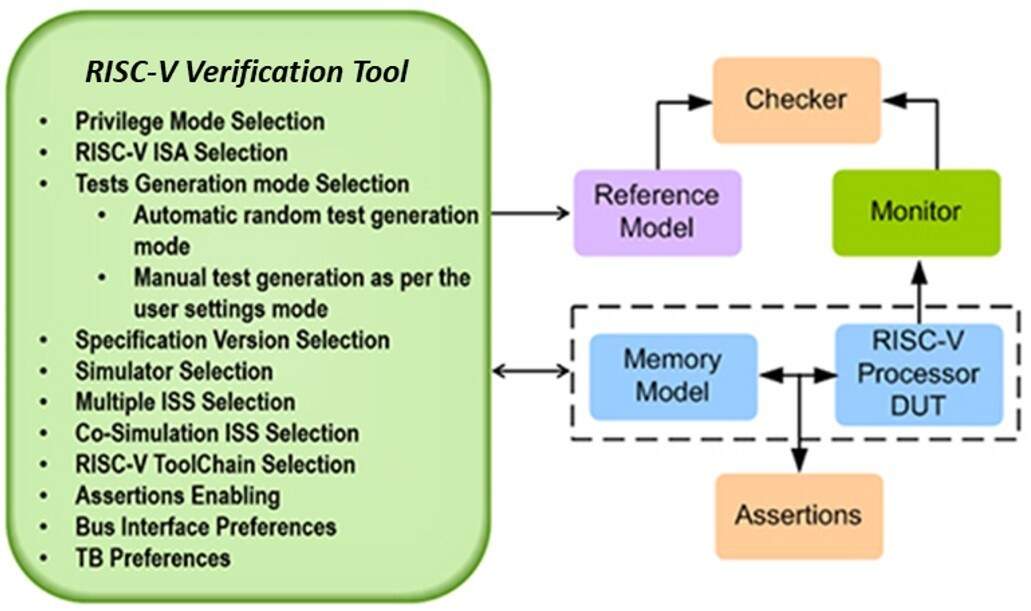

RISC-V 验证流程应包含大量组件,以确保 RISC-V CPU 开发人员实现其验证目标。(图片:SmartDV)

有了这么长的标准列表,确定一个符合所有条件的验证流程似乎是一项无望的任务。一个 RISC-V CPU 验证平台是一个完整的环境,用于严格验证基于 RISC-V 的新 CPU 设计,专门为 RISC-V CPU 开发人员实现对其设计的全面验证。它与 SystemVerilog/UVM 和基于 C 的流程以及所有行业标准的模拟器和 Verilator 兼容。支持所有 RISC-V ISA 的测试套件以及经过验证的黄金参考模型。

RISC-V CPU 或定制加速器的商业验证流程将为验证组提供对其验证结果的急需信心,并创造开放式协作和创新。

-

开芯院采用芯华章P2E硬件验证平台加速RISC-V验证2025-07-18 2596

-

rIsc-v的缺的是什么?2024-07-29 1209

-

RISC-V为何如此重要?2024-04-29 1299

-

Imagination:RISC-V CPU的重要力量2024-03-07 1528

-

新思科技收购Ansys,拓展RISC-V验证及验证解决方案2023-12-27 1287

-

RISC-V和RISC-V AI的未来(特邀讲座)2023-07-14 1192

-

基于形式的高效 RISC-V 处理器验证方法2023-07-10 1813

-

RISC-V入云!赛昉科技联合中国电信完成首个RISC-V云原生轻量级虚拟机验证2023-05-11 914

-

RISC-V拿什么挑战ARM?2023-01-16 1689

-

RISC-V CPU调试机制的设计原理2022-10-18 3217

-

RISC-V的挑战分析2022-02-25 3929

-

RISC-V中国峰会:RISC-V产业及生态发展2021-06-22 3786

-

RISC-V规范的演进 RISC-V何时爆发?2021-02-11 4391

-

RISC-V如何填补CPU知识空白2020-09-25 3431

全部0条评论

快来发表一下你的评论吧 !