基带视频中Logo插入的设计方法

电子说

描述

在典型的最后一英里广播分发系统中,有线电视运营商通过卫星接收来自内容提供商的广播节目,使用集成接收器/解码器 (IRD) 对其进行解码,然后重新编码基带视频(在编码器盒中)所需的分辨率、比特率和压缩标准。接下来,他们将多个节目流结合起来,最终分发给最终消费者。

一些国家要求有线电视运营商在传输给最终消费者的视频中插入他们的标志。本文讨论了在基带视频中插入静态徽标的各种机制及其优缺点。此外,本文还描述了我们认为为实现低成本解决方案而采用的独特设计方法。

视频编码器

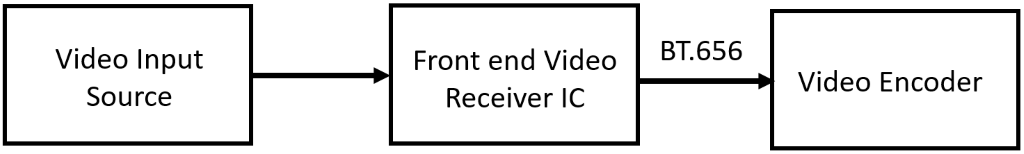

视频编码器通过各种模拟/数字接口接收视频内容,如复合 (S-Video)、分量 (YPbPr)、HDMI、DVI 和 3G-SDI,通常与视频前端 IC 连接,如图所示在图 1 中。

图 1:编码器系统中的视频接口

视频前端包括一个视频接收器 IC——它可以是一个 ASIC 或一个编程为用作视频接收器的 FPGA——它将前端视频信号解码为基带视频。该 ASIC/FPGA 的输出通常是 BT.656 标准格式的并行端口数字视频总线,连接到视频编码器进行压缩和持续传输。

标识插入的设计方法

标识图像需要在编码操作开始之前插入到基带视频帧中。将静态徽标插入视频流有多种设计可能性,如下所示:

在视频输入源之后和前端接收器 IC 之前使用标准徽标插入器。

选择一个前端视频接收器解决方案,它可以执行将视频解码为 BT.656 以及插入徽标的双重功能。

使用在基于 Arm/GPU 的处理器上运行的基于软件的视频编码器系统在原始捕获的视频中执行徽标插入。

上述每种方法几乎没有缺点和限制。选项 1 需要为徽标图像编程和配置采购和维护外部硬件。

选项 2 涉及使用领先制造商提供的支持屏幕显示 (OSD) 的视频前端收发器 ASIC。这些都有其自身的限制,包括徽标大小、混合能力、IC 成本以及每个视频输入接口对外部存储器(如 DDR2)的要求。此外,在收发器之后,需要将数据呈现给视频接收器,以将数据解码为数字 BT.656 格式,以便与标准编码器设备连接。

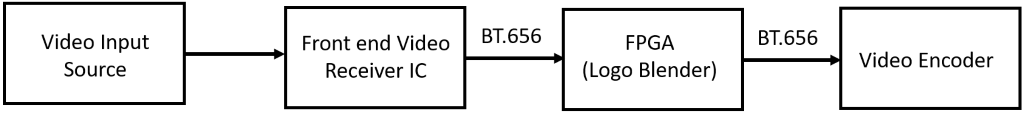

选项 3 是更好的解决方案,前提是视频编码器是基于软件的,它提供了将徽标图像混合到作为帧缓冲区存储在 DDR 中的原始视频像素中的可配置性。但是,如果视频编码器是一个没有提供标识插入的 ASIC,那么这个选项会自动被排除,我们必须依赖选项 1 或 2。在这种情况下,要实现一个低成本的多- 输入视频编码器的通道系统,在 Ittiam,我们决定使用一种创新方法,包括低成本 FPGA,在视频前端 IC 之后和基于 ASIC 的视频编码器之前混合徽标图像,如图 2 所示。

图 2:编码前在数字视频路径中插入徽标

此选项提供了一种低成本的多通道解决方案,因为单个 FPGA 能够对多个视频通道执行徽标混合操作(上图中仅显示一个通道以进行说明)。用于存储徽标图像的 SPI 闪存连接到 FPGA。FPGA 可以在配置的适当位置读取这些徽标图像并将其与输入基带视频流混合。

选择的 FPGA 可以是低成本的,因为该设计使用 FPGA 的内部 RAM、逻辑元件和常见的 DSP 乘法器硬件块来执行混合操作所需的像素乘法操作。

FPGA RTL IP 旨在将 SPI 闪存配置为 QSPI 模式,以满足 FIFO 读写接口的数据速率要求。QSPI 接口足够快,可以在 BT.656 像素时钟读取单行徽标数据之前将一行徽标写入或缓冲到 FPGA 的 FIFO 块中以进行混合操作(这决定了 QPSI 操作频率在 FPGA 设计中)。透明度因子(α,或alpha)可由用户在FPGA中配置,并且该因子可以被FPGA中实现的alpha混合算法用于执行标识插入操作。

结论在Ittiam Systems

开发的硬件设计中,上述方法已成功设计并实现了在基带视频中插入徽标图像。这种设计的优点是它具有最小的延迟并降低了硬件解决方案的总体成本。

审核编辑:郭婷

-

请问数字基带信号中的“基带”是什么意思呀?2024-12-12 519

-

在allegro软件中插入公司LOGO的方法2015-07-13 15325

-

有没有人做过视频基带传输的实验?那种可以传输模拟视频的。2015-08-07 3900

-

【原创】教程-AD怎样导入平滑logo2020-05-26 3423

-

CAD中如何插入图框?CAD插入图框方法教程2021-04-25 7264

-

怎么插入视频啊2021-05-20 2126

-

将企鹅的Logo换成自己喜欢的任意图片或公司logo的方法2021-12-20 860

-

LOGO!在医疗器械自动控制中的应用The applicat2009-06-06 840

-

华为NodeB基带单板的配置方法2009-06-30 3183

-

AD09制作LOGO方法2016-03-11 1917

-

关于AD中如何添加LOGO的方法2016-04-11 2167

-

如何在PCB中放置LOGO的两种方法,让你随心所欲地在PCB上放置LOGO2018-07-06 26084

-

如何在PCB中放置LOGO2019-08-19 7049

-

LOGO!存储卡的功能2023-01-17 9031

-

如何在播放视频过程中插入音频2024-12-26 2410

全部0条评论

快来发表一下你的评论吧 !