基于IDEA导出个人IP库设计的jar包

FPGA/ASIC技术

描述

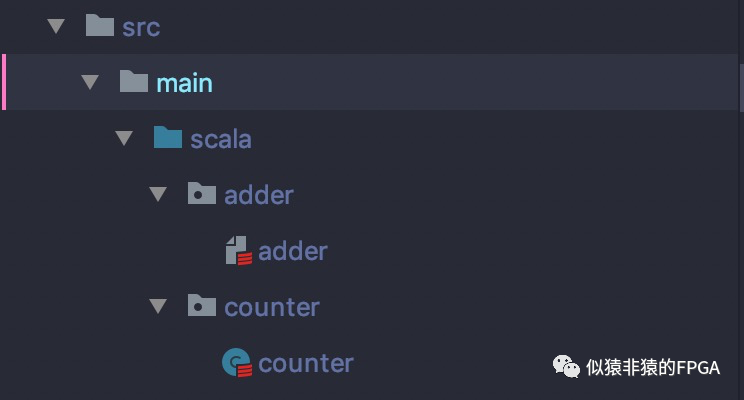

实例的工程目录结构如下所示:

工程中有两个pacakge:adder和counter。

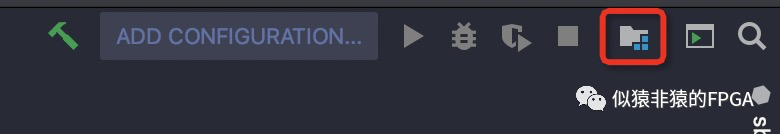

通过IDEA右上方下面的按钮进入Project Structure(或者通过File->Project Structure)进入:

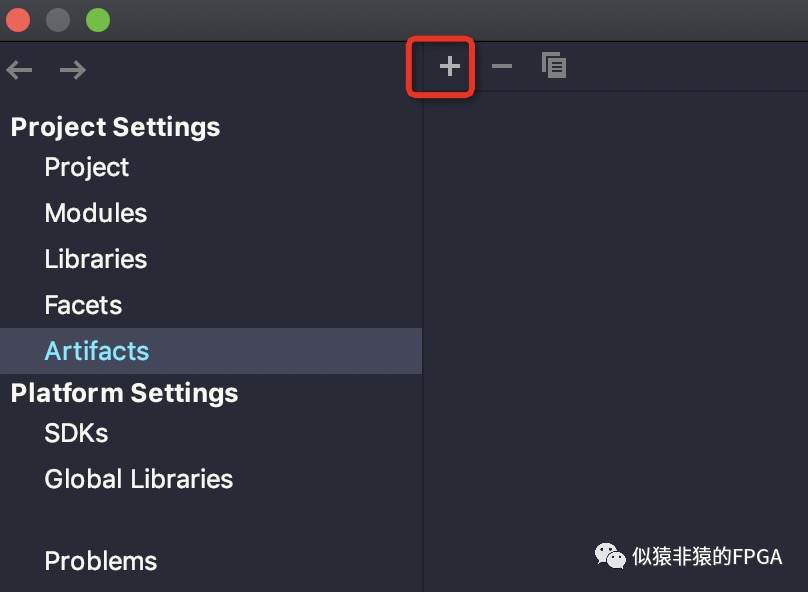

在Artifacts界面里点击红框中的“+”号选择JAR->From modules with dependencies.

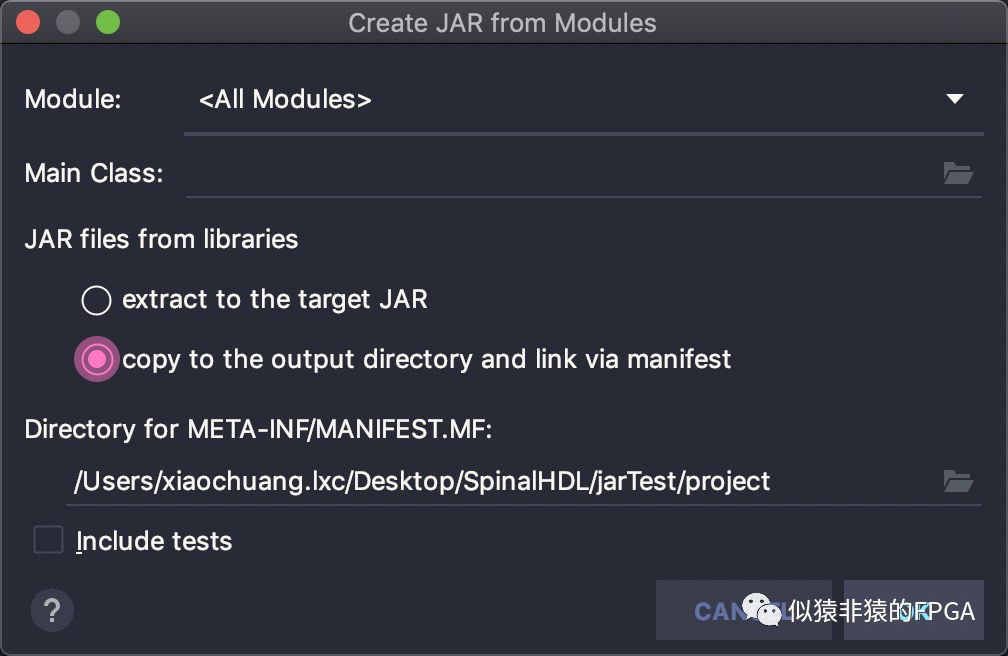

选择“copy to the output directory and link via manifest”。Directory for META-INF/MANIFEST.MF的路径可保持默认目录或另行指定目录。随后点击OK。

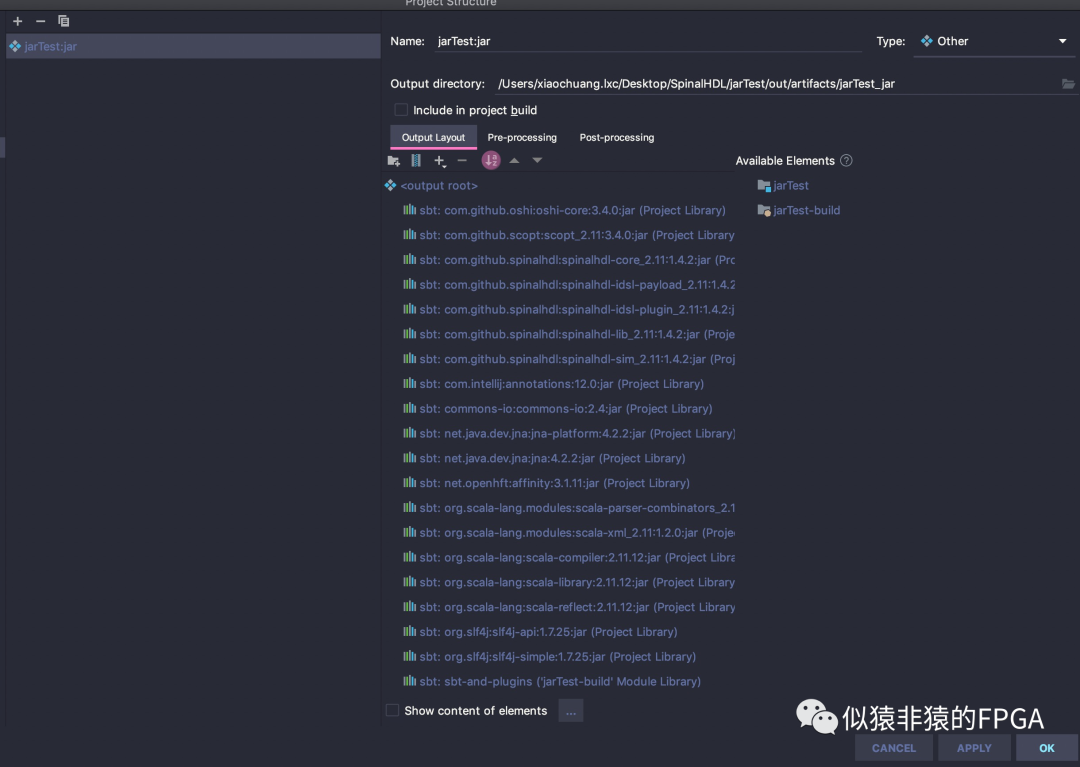

在下面的Output layout里,可以删除不必要的“零碎儿”:

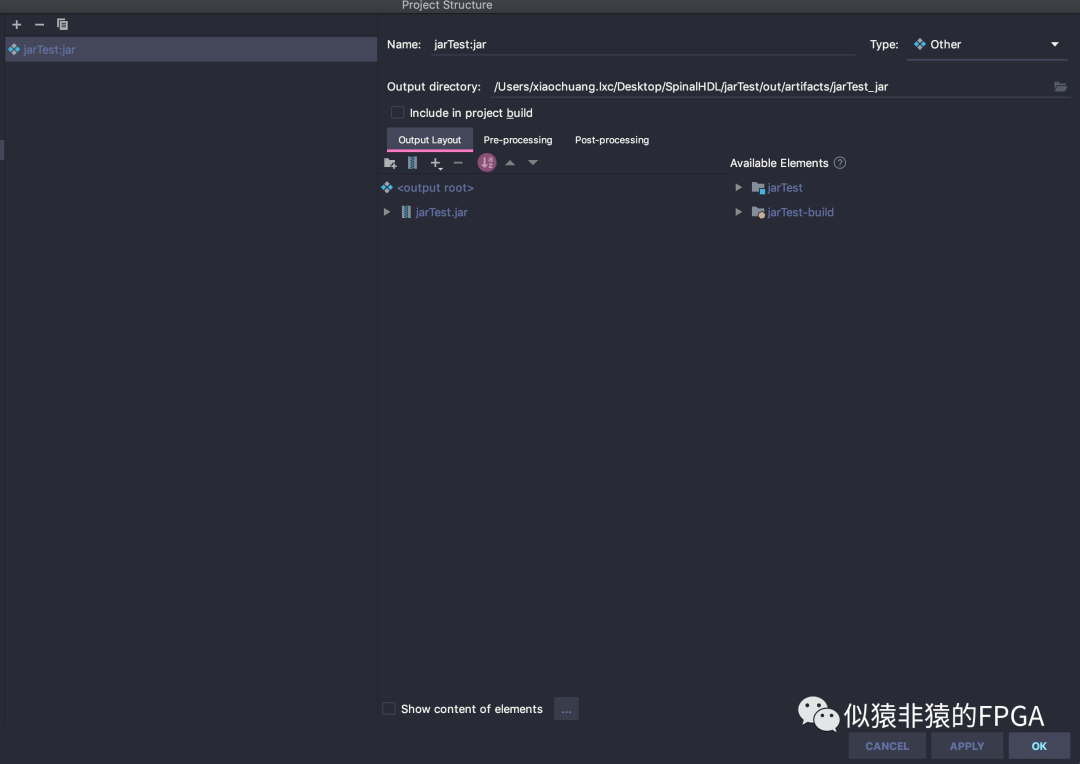

最后只保留我们自己的设计:

点击OK,配置完成。

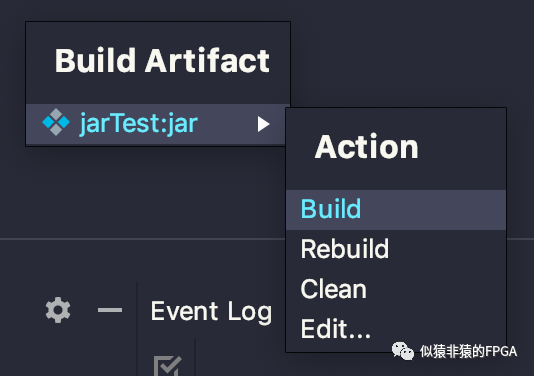

通过菜单栏Build->Build Artifacts导出生成jar包:

最后会在工程目录的out文件夹下生成jar包:

jar包生成后,我们就可以在其他的工程中导入jar包或者提供给他人。

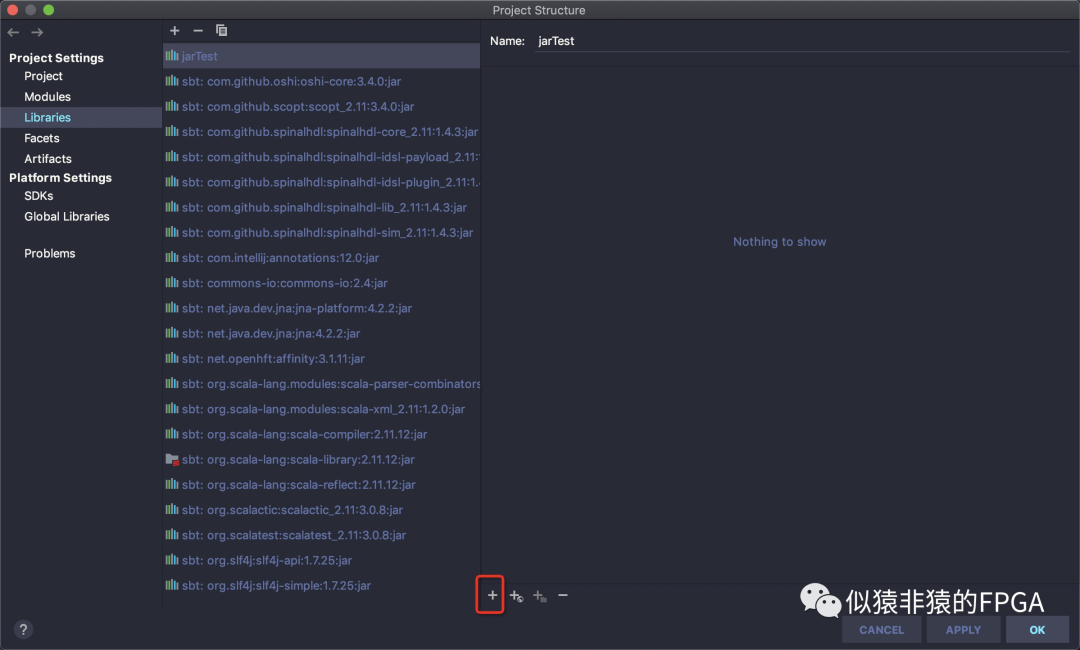

通过 File->Project Structure导入jar包:

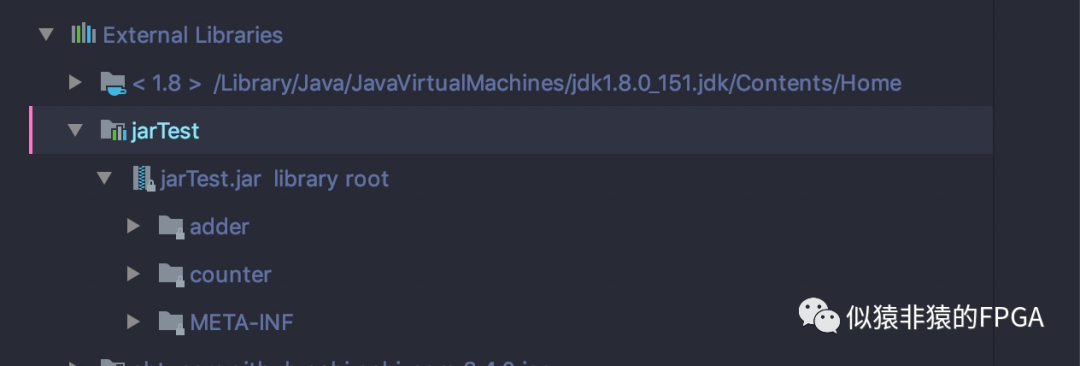

导入后即可使用:

我们即可像使用SpinalHDL一样即可使用:

审核编辑 :李倩import counter._import spinal.core.SpinalSystemVerilogobject counterApp extends App{SpinalSystemVerilog(counter())}

-

实际上手体验maven面对冲突Jar包的加载规则2024-08-08 1071

-

常见的存储Idea数据库的地方2023-12-06 2023

-

如何实现动态上传jar包热部署2022-06-20 2086

-

鸿蒙三方库移植及开发项目如何打入Jar包中2021-03-19 4293

-

docker运行之jar包2020-07-18 1931

-

几种Linux下后台启动jar包的方法介绍2019-07-22 3600

-

JAR文件包及jar命令详解2019-07-12 1478

-

请问如何打jar包和运行jar包?2018-07-05 3545

-

统计java代码行数和jar包中.class代码的行数2018-03-19 1305

-

jar与war之间不得不说的事2017-12-12 5642

-

RXTX_java开发的jar包2016-09-26 749

-

关于JAVA不能打包成jar包的问题2014-12-09 2432

-

tomcat跑iMatrix平台源码需删除几个jar包2013-10-11 2831

-

TANDBERG推出个人网真解决方案EX902010-04-02 903

全部0条评论

快来发表一下你的评论吧 !