DC-DC开关电源的开关波形产生高频振荡的原因

电源/新能源

描述

大家好,欢迎回来。

上一期我们分析了DC-DC开关电源的静态纹波产生的原因、动态响应时产生的过冲和下冲,并提供一些改善方法:技术分享 | DCDC开关电源实战经验之静态纹波及动态响应调试方法

这一期为大家分享的是:DC-DC开关电源的开关波形产生高频振荡的原因,以及优化方案。

BPSemi

- DC-DC开关波形-

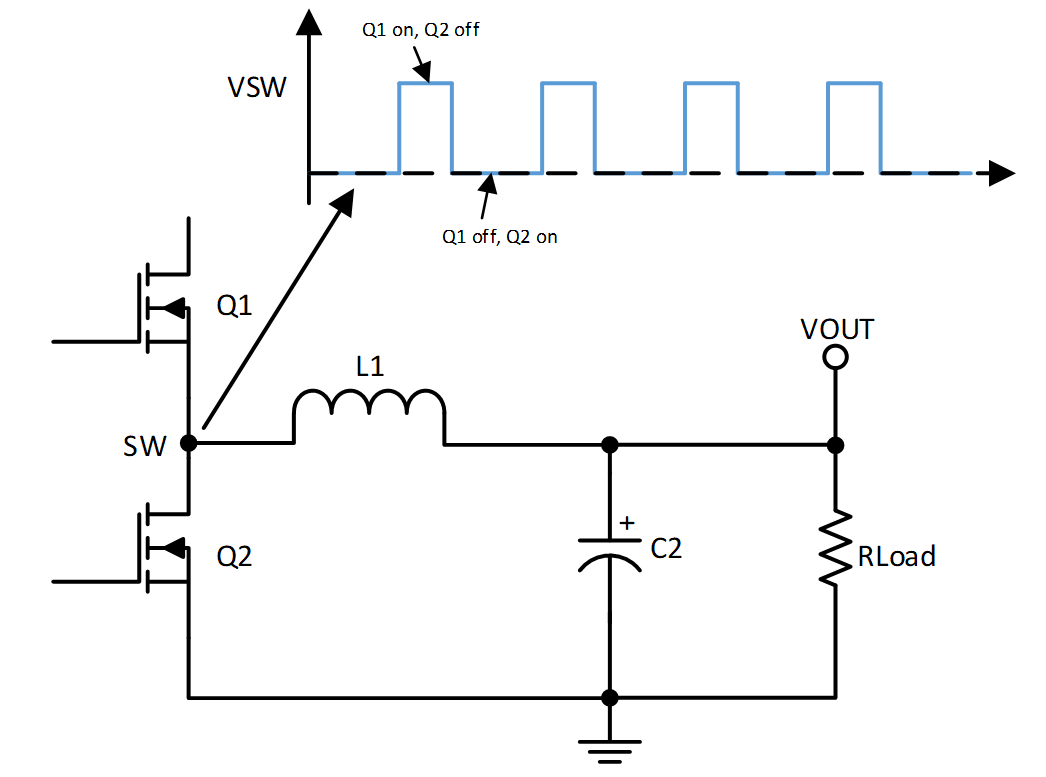

开关波形,顾名思义就是开关节点的波形,是上下管交替导通产生的周期性脉冲波,也是考量电源设计可靠性的重要指标:

为何要测量开关波形?从开关波形我们能得到什么信息呢?下面为大家介绍一下测量开关波形的目的:

01

判断上下管是否有直通的风险

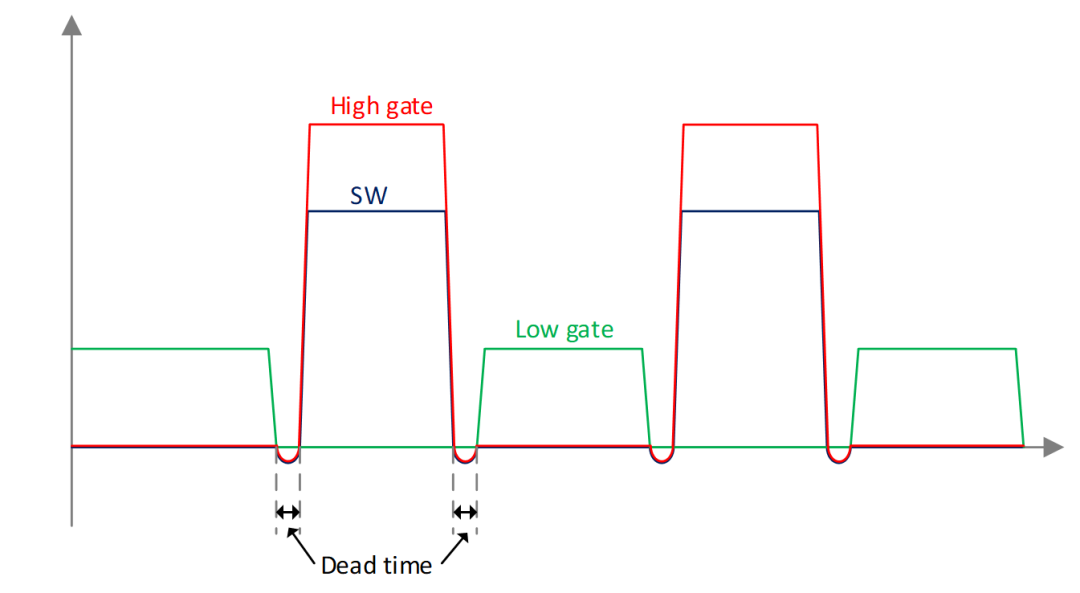

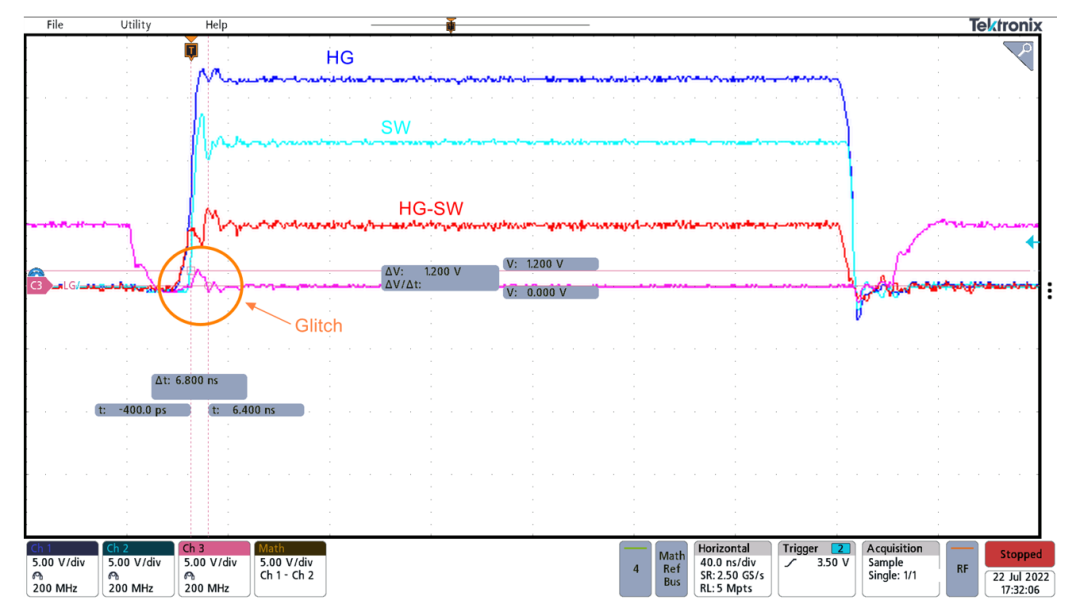

MOS驱动信号和SW波形如下图所示:

为了避免上管和下管同时导通,MOS驱动在上下管切换时加上死区时间(dead time),此时上管和下管同时关断,电流从下管的体二极管(body diode)流过,因此可以看到SW有一个小的负电压(体二极管导通压降)。

通常情况下,由于存在死区时间,不会有同时导通的风险,但是有的MOS开关速度较慢,在没有完全关断时,另外一个MOS就开始导通,从而导致出现直通,这种情况需要更换MOS搭配。

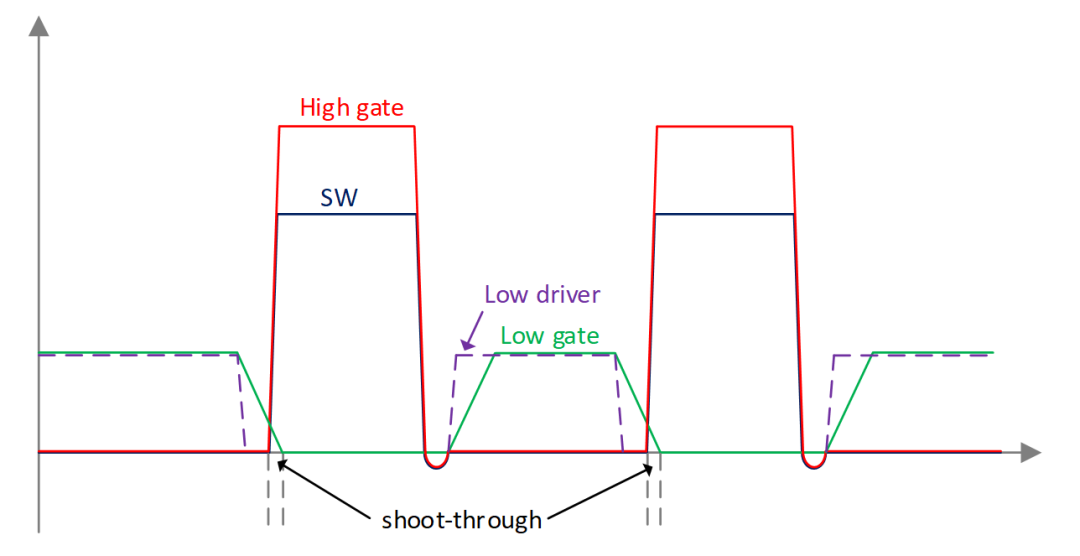

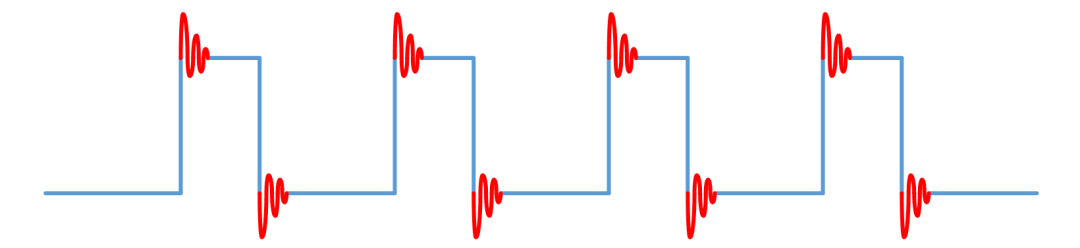

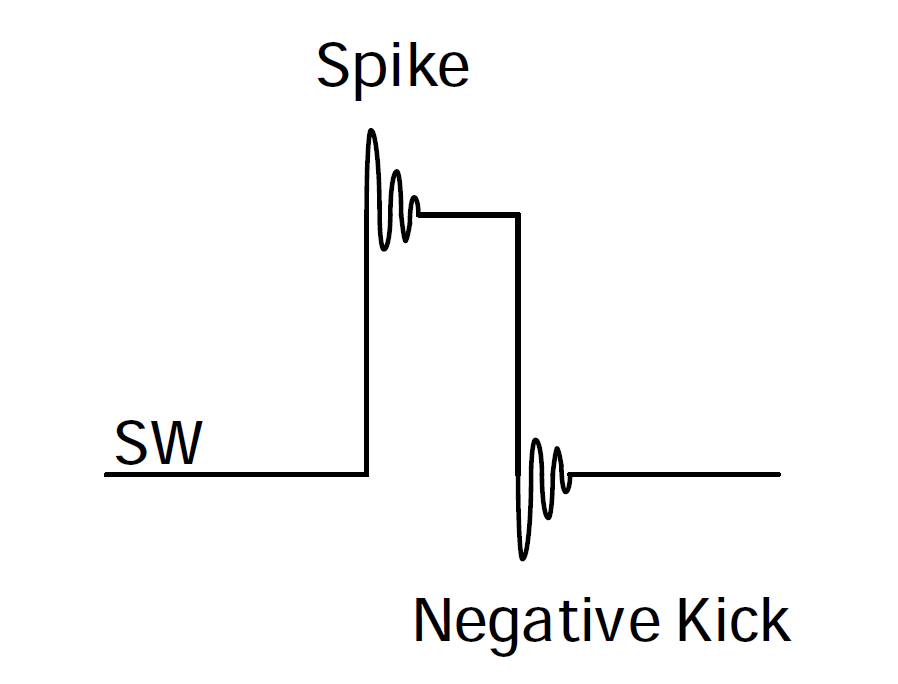

另外,理想状态下,开关波形是标准的脉冲波,但是由于PCB走线和元器件存在各种寄生参数,实际的开关波形一般会存在一些振荡,如下图所示:

在上管导通时可能会导致下管驱动信号出现一个小尖刺,如果电压足够高,并且持续时间较长,就会导致下管导通,出现直通。

02

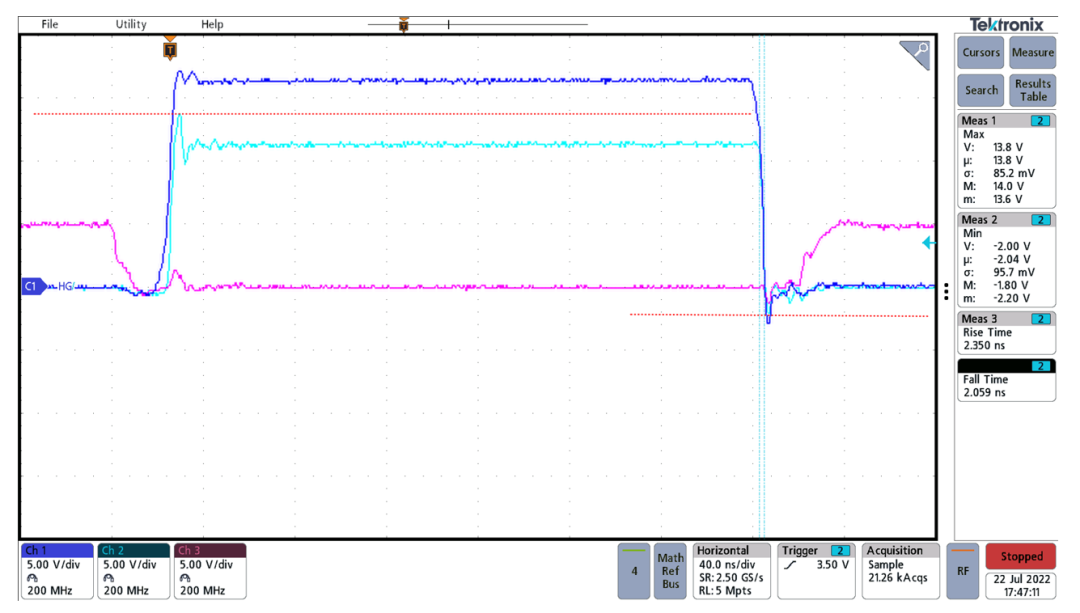

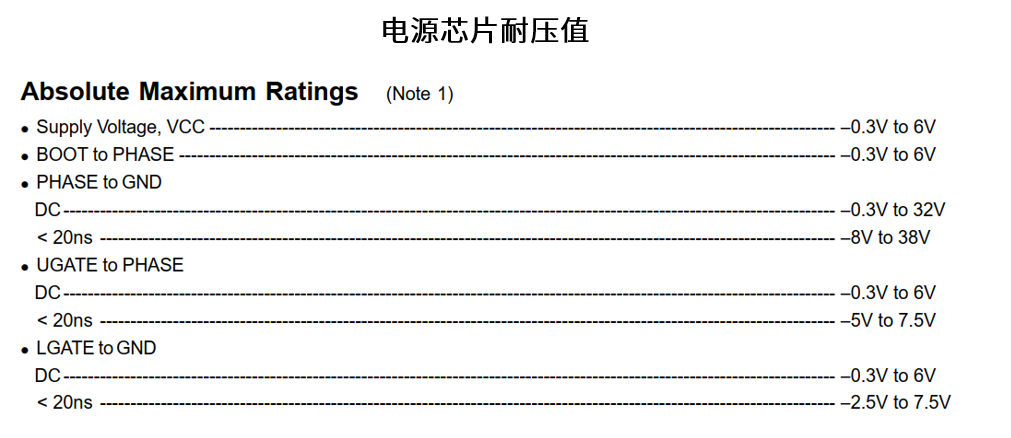

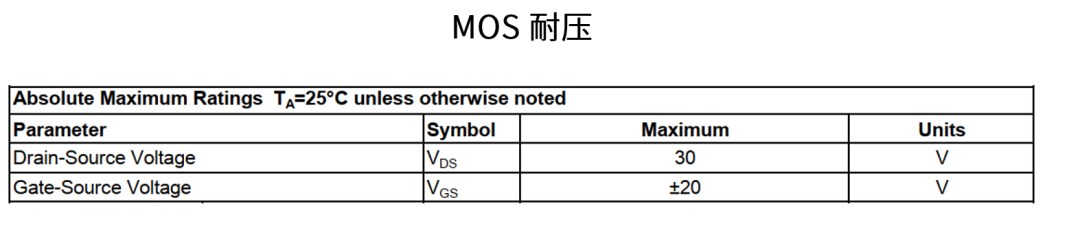

判断是否超过器件耐压

电源芯片或者MOS都有自身的耐压,超过耐压可能会导致器件失效,因此需要通过量测开关波形来确认是否有超过耐压的风险。

03

判断系统稳定性

通过量测开关波形的抖动,可以确认系统的稳定性,抖动越小则越稳定(此方法需要在稳态负载下测试)。

BPSemi

- 开关波形高频振荡-

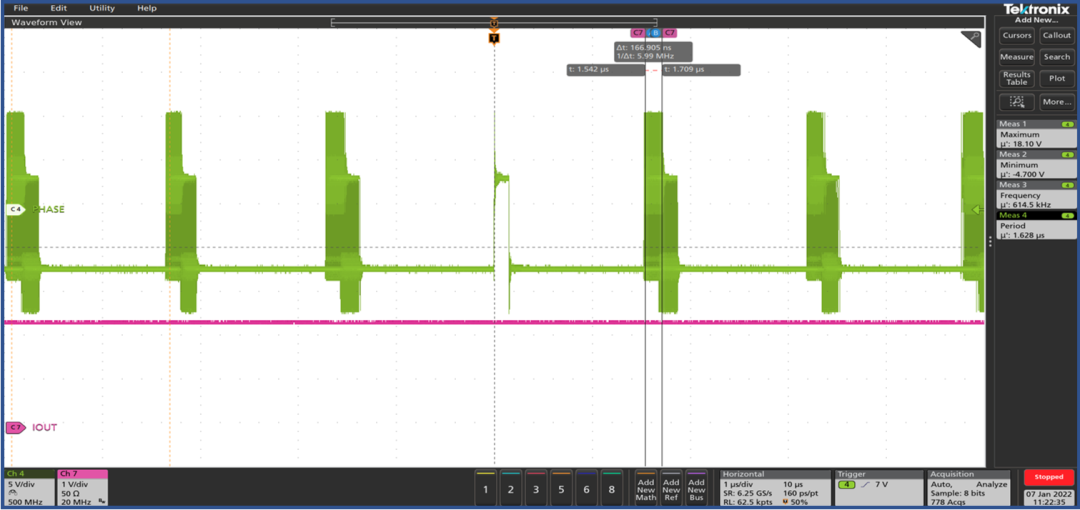

通过一些实测波形我们可以看到,在上管导通或者关断时,开关波形都会产生较明显的振荡,那么这些振荡产生的原因是什么呢?又会造成什么影响?下面将为大家详细介绍一下。

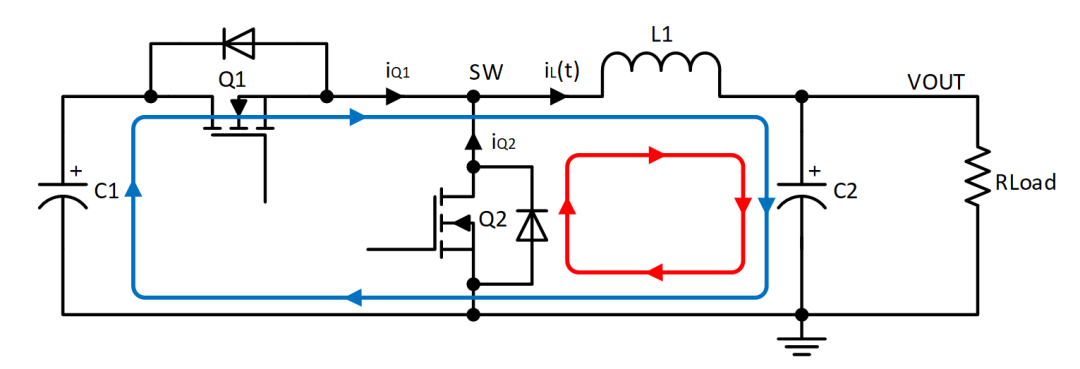

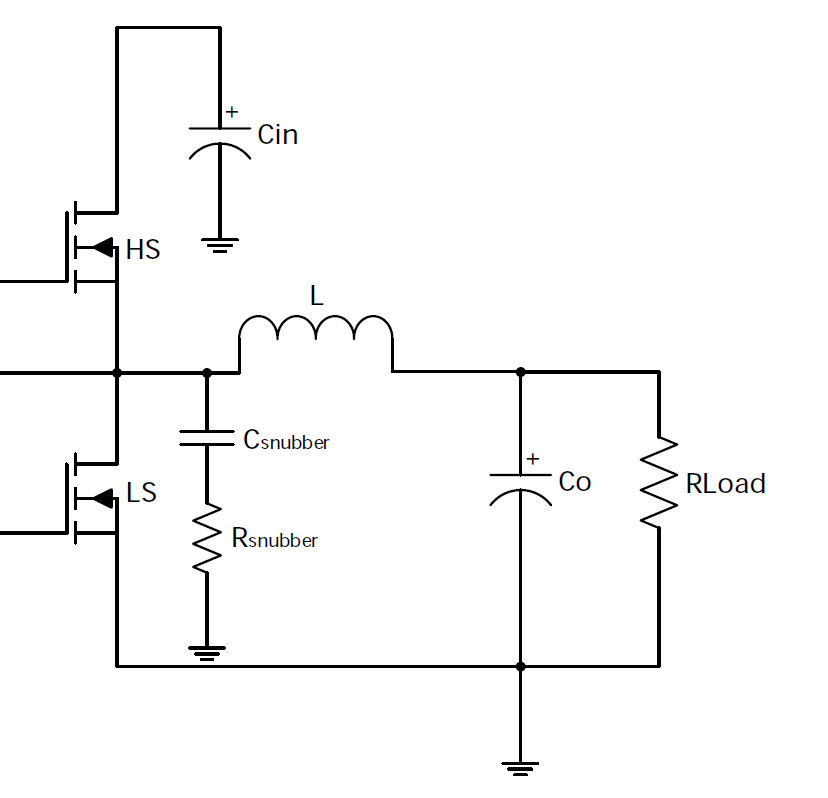

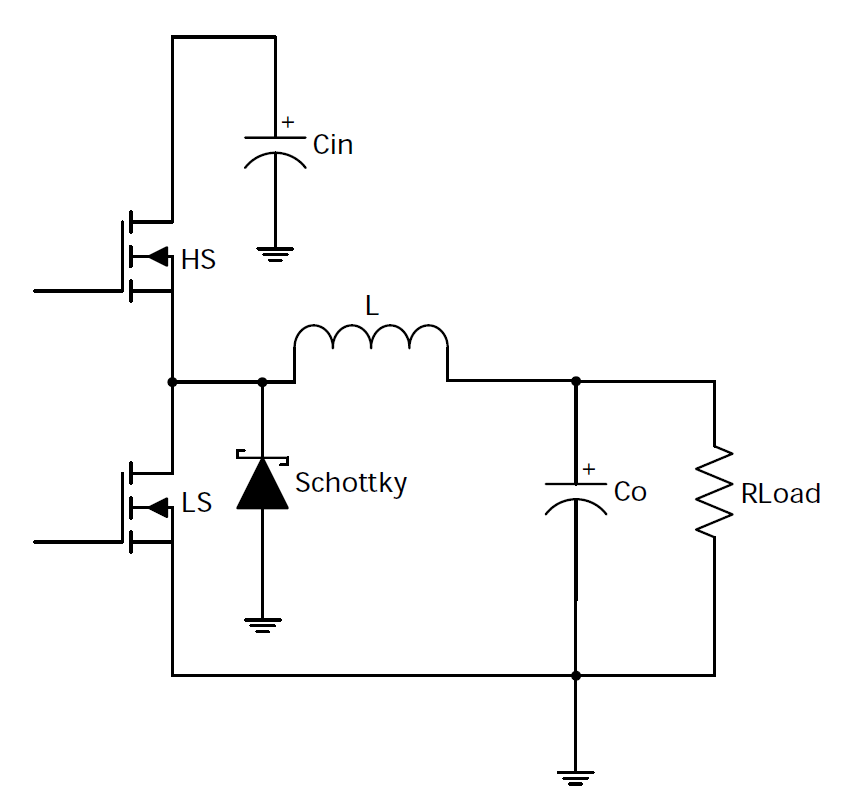

在这之前,我们先回顾一下开关电源的工作原理,如下图所示:

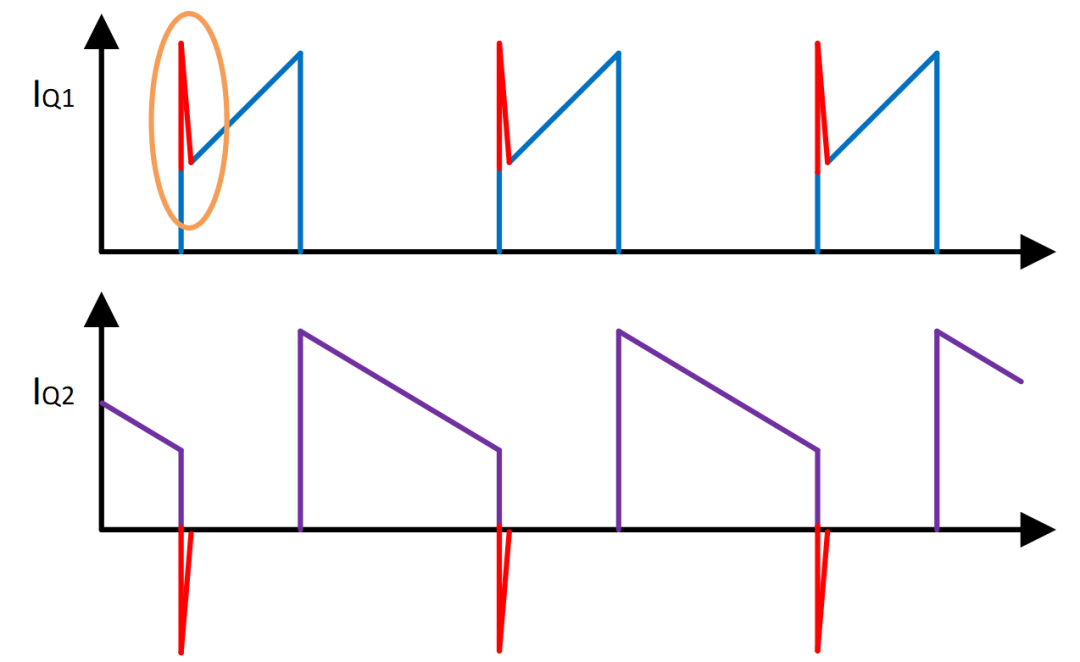

可以看到MOS在导通和关断时,MOS的电流在非常短的时间内出现剧烈变化(从0到电感电流),这就导致了很大的电流变化率di/dt。

并且,由于下管存在体二极管,在上管导通时会存在反向恢复电流,这就导致了上管的电流在导通瞬间出现一个非常大的电流尖峰,这就形成了更大的电流变化率di/dt。

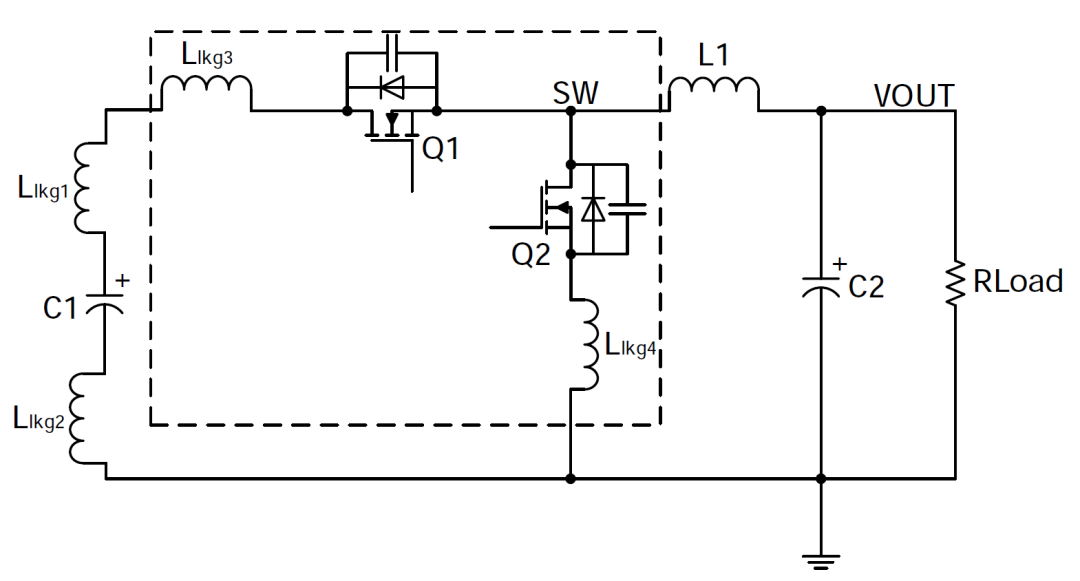

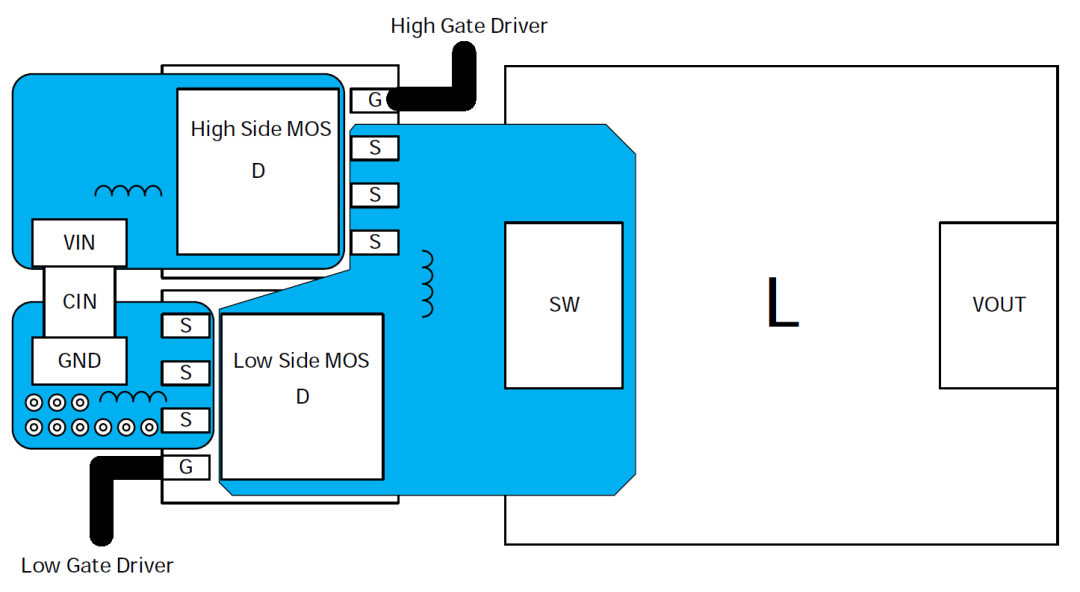

前面有提到,由于PCB走线和元器件存在寄生电感和寄生电容,在如此剧烈的电流变化条件下,会形成明显的LC振荡(同时有寄生电阻,实际为RLC阻尼振荡)。

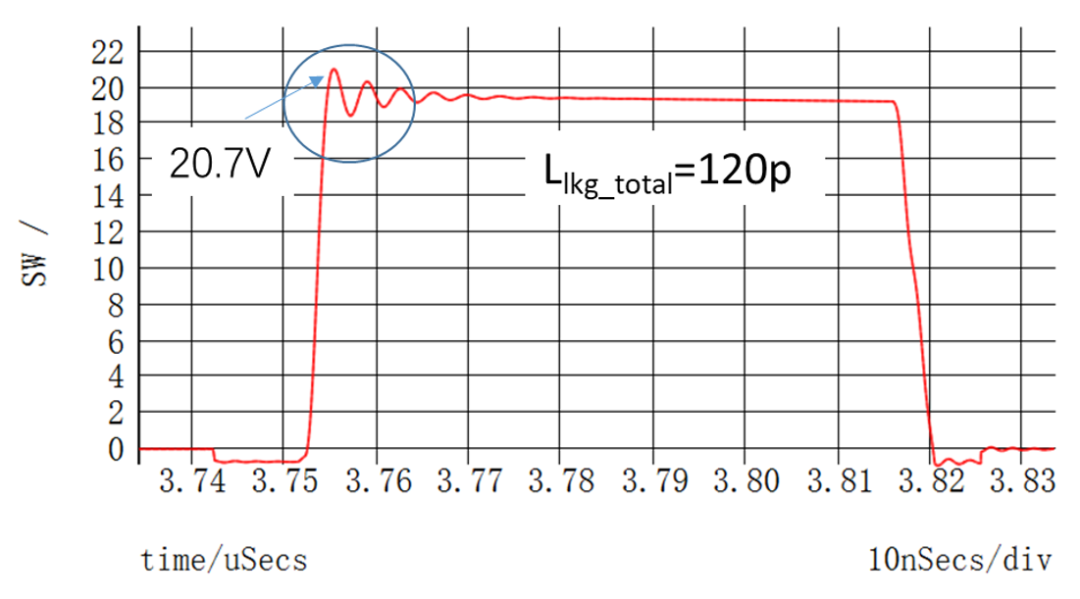

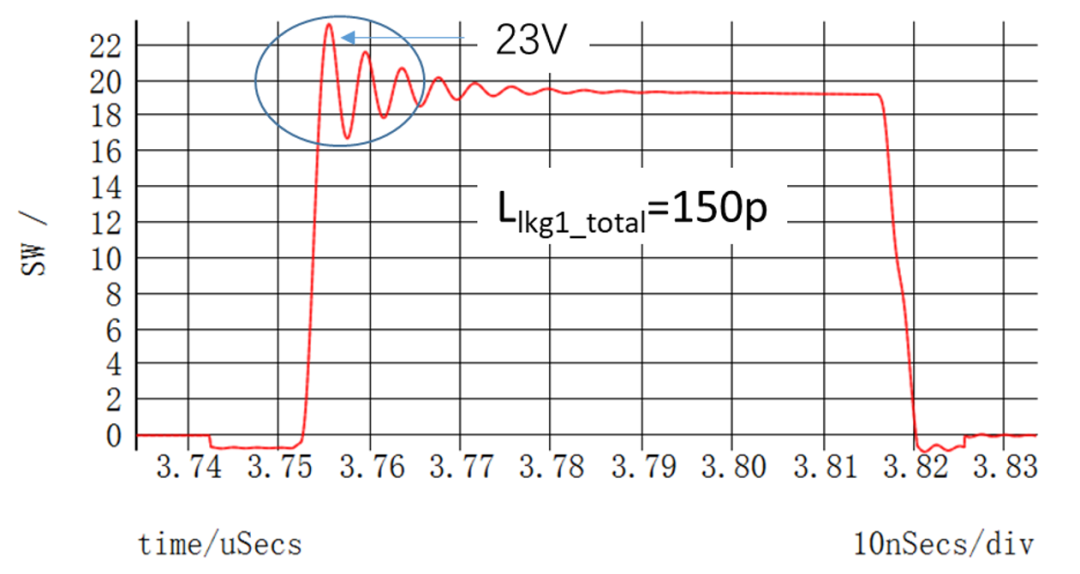

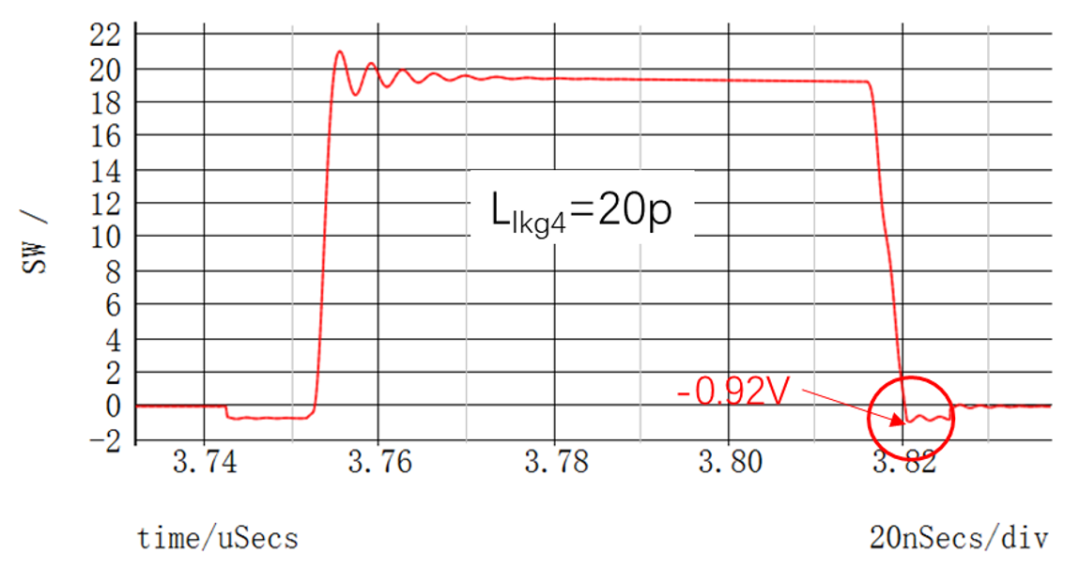

可以看到,寄生电感主要有PCB走线引起的Llkg1和Llkg2,以及MOS内部打线引起的Llkg3和Llkg4。这些寄生电感跟MOS本身的寄生电容形成LC谐振电路,当路径上的电流发生剧烈跳变时,发生振荡,并且形成很高的电压尖峰。

通过仿真对比,我们看到,总的寄生电感值Llkg_total影响正的电压尖峰,增大Llkg_total,正向电压尖峰也会变大。

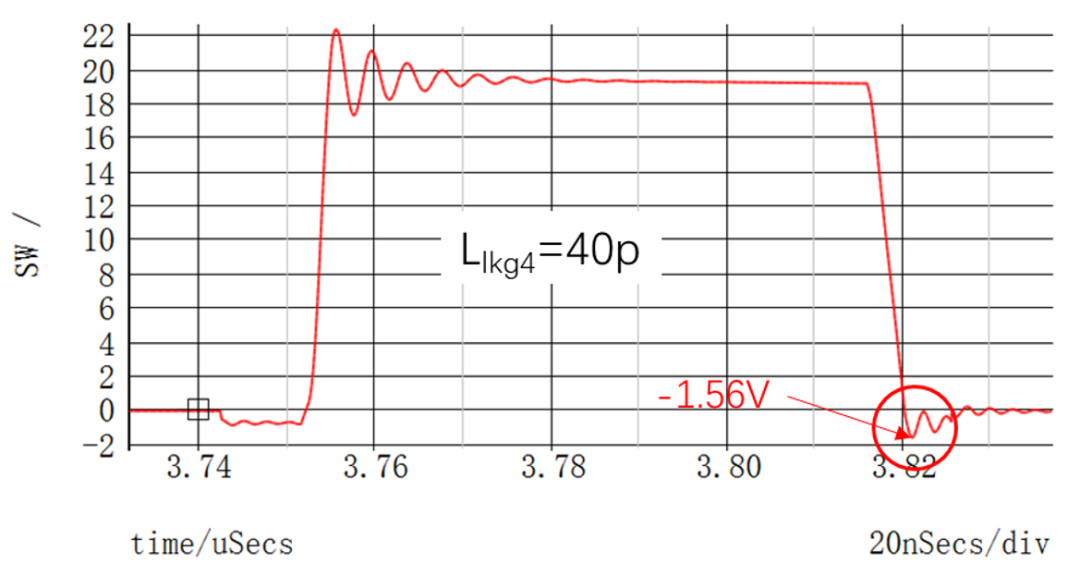

而下管到GND的路径上的寄生电感对负压影响比较大,增大这个寄生电感,负压也会变大。

产生振荡的原因我们已经了解了,那这个振荡会对电源系统造成什么影响呢?主要有如下几点:

振荡形成的正向尖峰电压和负压,可能会超过器件耐压,造成器件损坏;

振荡波形干扰MOS驱动信号,可能会导致上下管直通的风险

高频振荡造成强烈的EMI,影响其他器件工作

因此,为了系统能更稳定的工作,我们需要尽量减小开关波形的高频振荡。

BPSemi

- 如何改善高频振荡-

从前面的分析,我们可以看到,振荡的主要原因是寄生电感和快速的电流变化,因此改善方案也主要从这几个方面入手:

01

减小寄生电感

这个可以分为两个方面:PCB走线,MOS内部封装。

对于PCB走线,需要尽量减小输入电容VIN→上管→下管→GND的环路,并且下管的GND尽量多打过孔,以减小寄生电感。

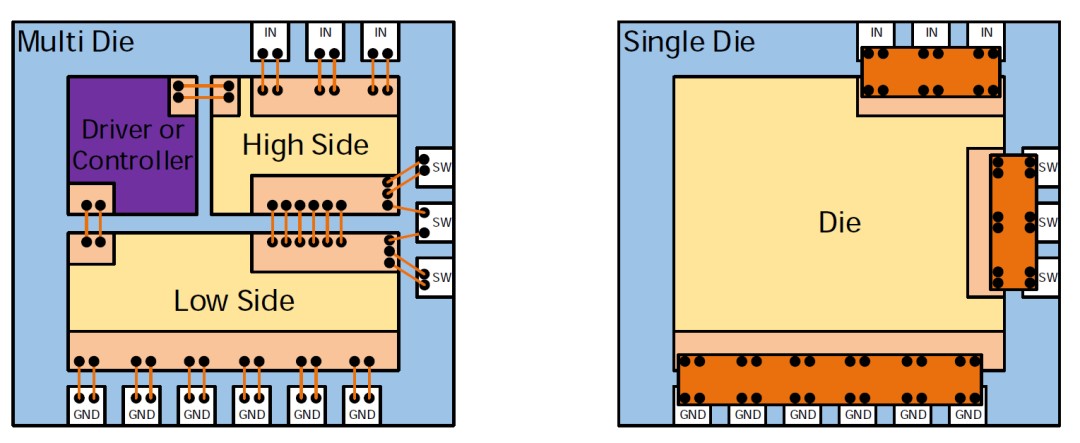

而对于MOS部分,则尽量选用集成方案,比如DrMOS,converter等。single die的DrMOS和converter,由于基本没有打线,寄生电感比multi die的更低。

晶丰明源提供的功率级方案(DrMOS,POL等)都是采用singledie的设计,因此可以获得更好的性能。

02

降低MOS导通和关断的速度

另外一个减小振荡的方法,则是通过降低MOS的开关速度,从而减小电流变化率(涉及到MOS的开关过程,此处不作详细描述,如有兴趣可以持续关注晶丰明源公众号)。

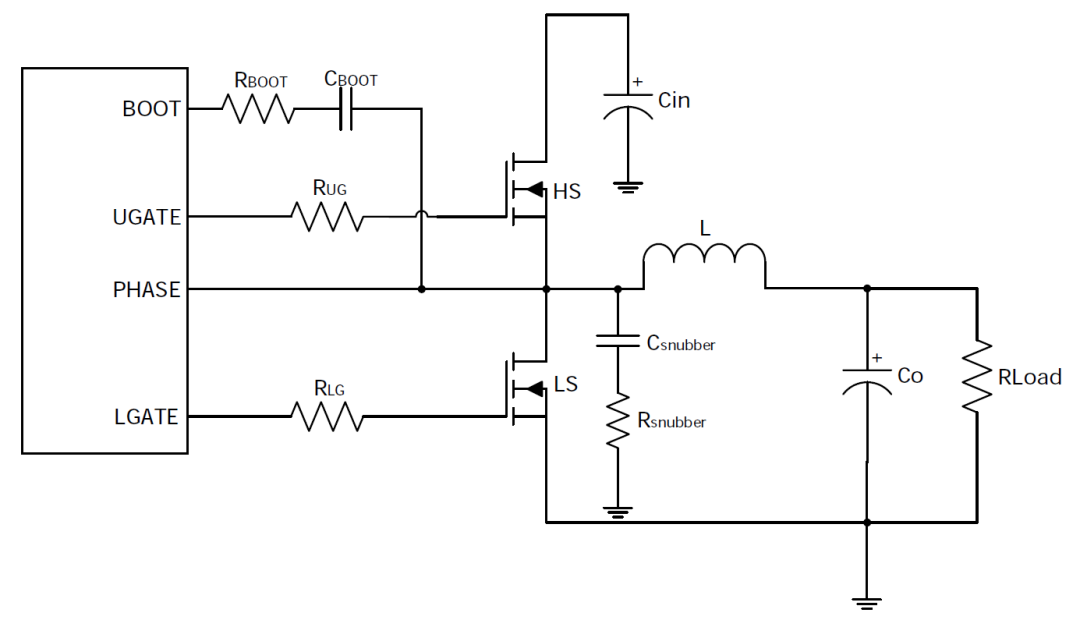

通常我们的原理图上都会增加BOOT电阻和驱动电阻,通过增大这两个电阻的阻值,可以有效降低MOS的开关速度。

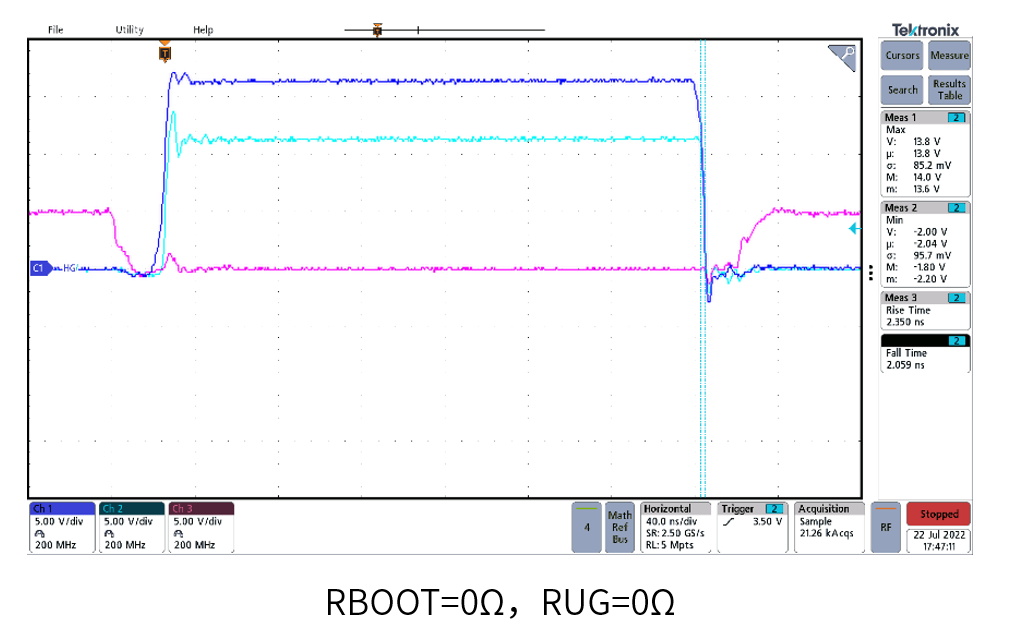

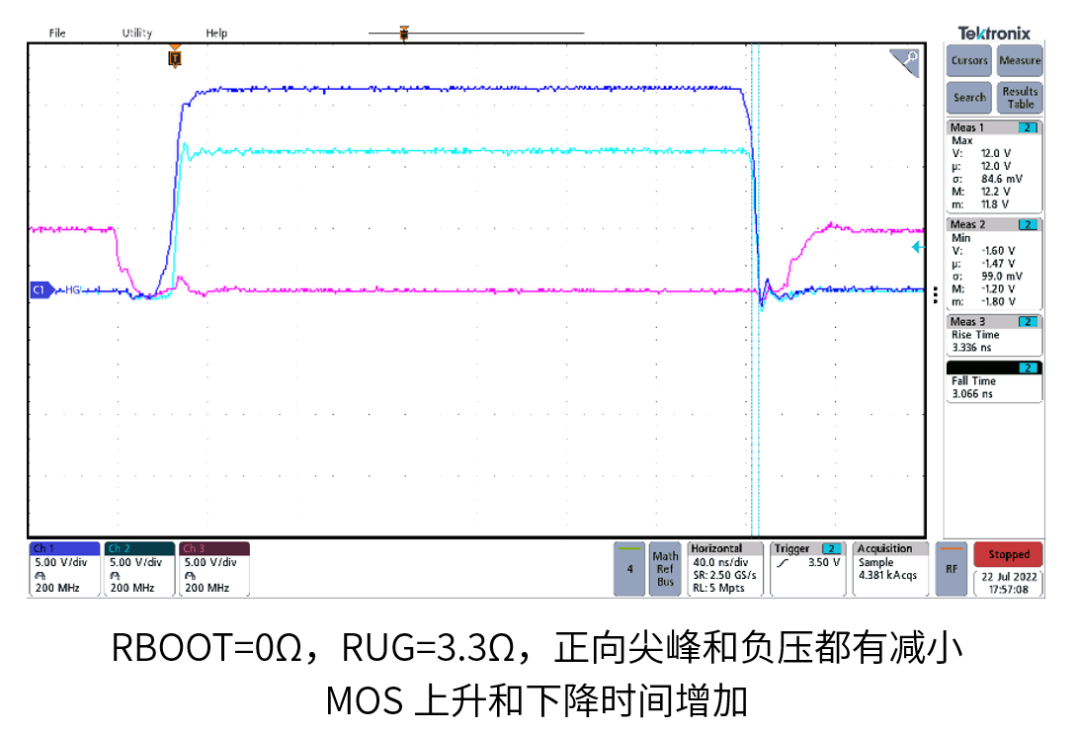

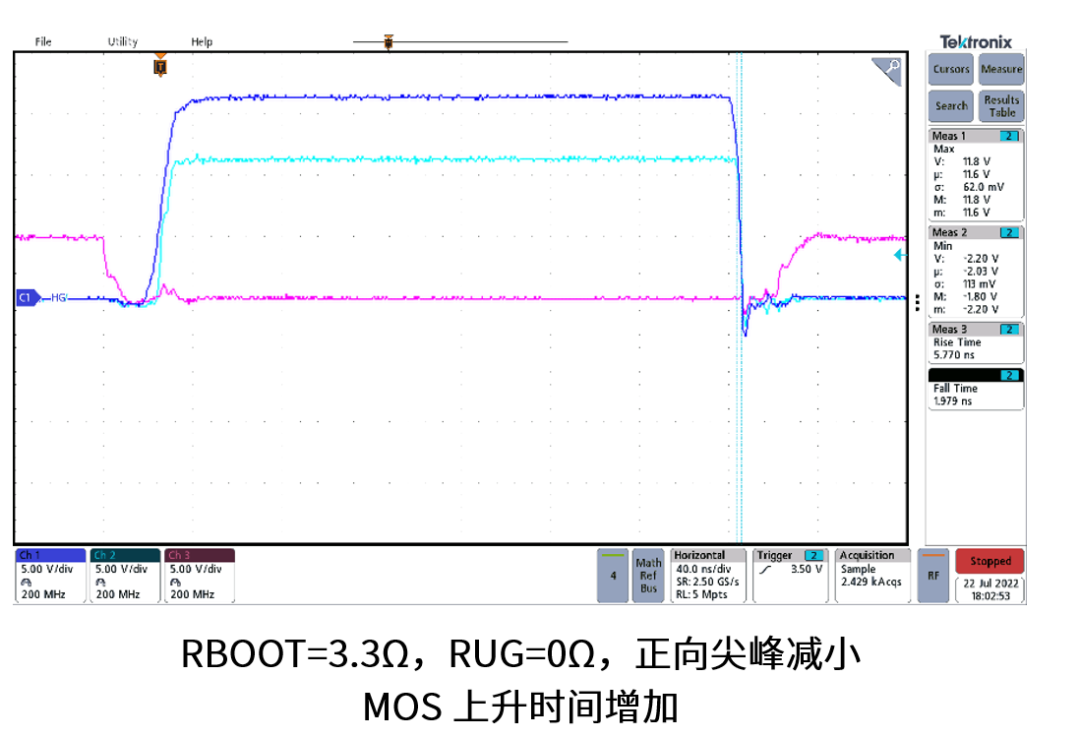

其中,增大BOOT电阻只对上管导通的速度有影响,对关断的速度没有影响;增大驱动电阻RUG,则同时影响上管的导通和关断速度,实际对比如下:

03

增加RC吸收电路

第三种方法,则是在SW增加对地的RC电路,吸收振荡能量。不过需要注意的是,RC接地尽量单独接到公共的地平面,避免下管接地引起的寄生电感影响效果。

RC的参数,电阻一般选择1~10Ω,电容在nF级,需要经过实测确认。

04

下管并联肖特基二极管

除了降低MOS开关速度,还有个办法可以减小电流尖峰:在下管并联一颗肖特基二极管。肖特基二极管的反向恢复特性比普通二极管好(一般MOS内部寄生的二极管是普通二极管),因此可以有效降低反向恢复电流。同理,肖特基二极管的地也尽量单独接到功率地。

BPSemi

- 总结-

降低开关波形高频振荡的方法总结如下:

优化PCB布局和走线,尽可能减小输入电容和MOS的电流环路

选用集成MOS方案,最好是single die

增加MOS驱动电阻和BOOT电阻

增加RC snubber

下管并联肖特基二极管

其中增加驱动电阻和snubber会造成效率下降,需要取舍;下管并联肖特基二极管还可以提高效率,但是会增加成本和PCB空间,因此最好是layout优化和采用single die集成方案。

晶丰明源DCDC,超过100位行业顶尖精英的强大团队,构建研发、运营、销售的完整产业链条,拥有数字控制IP、大电流设计IP、BCD工艺、封装等核心技术。高标准可靠性实验室,具备高温老化、高加速应力、温度循环等多种可靠性鉴定和可靠性监控能力,每一款量产产品,都经过严苛的测试,确保产品的稳定可靠。我们志在追赶国际巨头的技术优势,跻身计算电源的重磅玩家。

-

全桥DC-DC开关电源参考设计2025-05-23 387

-

DC-DC开关电源的效率优化2022-09-20 7104

-

.基本DC-DC变换器开关电源学习笔记2021-10-29 3399

-

开关电源(DC-DC)与LDO电源的区别---原理2021-10-21 1416

-

车载DC-DC开关电源的设计2021-09-22 1606

-

基于PID控制的DC-DC升压开关电源设计2021-08-04 1385

-

ADP1828低压DC-DC开关电源2021-05-18 1243

-

DC-DC变换的开关电源电路有什么功能?2019-10-25 2523

-

DC-DC开关电源设计2019-03-19 2753

-

如何分析与优化设计DC-DC 开关电源EMI问题2019-01-10 9538

-

DC-DC可调开关电源设计与仿真研究2017-03-28 8103

-

DC-DC开关电源2016-03-17 7117

-

开关电源技术专题-DC/DC 开关电源技术应用方案集锦2014-12-12 3752

-

DC-DC变换的开关电源电路图2009-05-13 2324

全部0条评论

快来发表一下你的评论吧 !