ATE PCB 的快速转向和高质量

今日头条

描述

“负载板”是几年前半导体行业用于自动测试设备 (ATE) PCB的术语。然而,近年来,它们在半导体行业中被称为“设备接口板 (DIB)”或“处理器接口板 (HIB)”。芯片制造商在订购测试板时需要快速周转和高质量评估他们新生产的和高度先进的产品,无论品牌如何。这超出了前几代测试板的要求。

这是因为芯片现在的制造速度比几年前要快得多。芯片制造商热衷于尽快测试他们的产品,因为他们正在以更快的速度生产它们。制造时间框架过去是两到三个月,但今天它们接近六到八周。芯片制造商要求尽快使用 ATE PCB 板来测试他们的新芯片,他们不希望价值数百万美元的芯片闲置。

ATE PCB 供应商有两到三个月的时间来交付这些测试板。然而,他们现在有六到八周的时间来完成芯片制造商所需的 ATE PCB。ATE PCB 供应商可能会通过包含其他服务来提高报价。例如,当 Naprotek 等电子制造服务 (EMS) 供应商除了提供 ATM 测试板之外,还提供晶圆测试和检查、处理、切割和半导体封装时,芯片制造商会获得奖励。

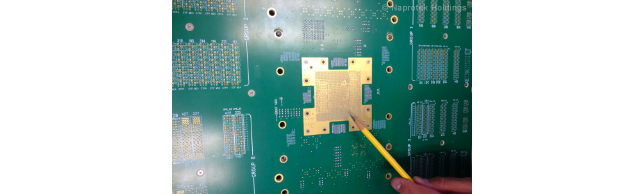

为了提供高质量的 ATE PCB(图 1),需要设计知识和智能设计方法。

这包括对与这些大型电路板的设计相关的布局和布线有精细的接触和精确的了解,以及了解与缩小球栅阵列 (BGA) 封装、显着减小 BGA 球之间的间距相关的所有细微差别,以及对与这些大型电路板的设计相关的布局和布线有精细的接触和精确的了解。

图 1:ATE PCB 可以有 30 到 50 层,远超传统印刷电路板。

质量和准确性

精心设计且准确的 ATE PCB 是各种设计方法、政策和程序的结果。例如,必须确保旁路电容器的放置和电压限制的存在。

由于设计人员现在正在构建 30 到 50 层板,因此存在远远超出与标准多层板相连的其他板。高质量的 ATE 测试板是通过专注的设计程序创建的,并遵守严格的制造标准。

否则,测试板结果的准确性将受到影响。例如,失败率高的一个可能不准确。当你这样做时,你会扔掉体面的筹码和很多钱。因此,这就是质量发挥作用的地方。

以下是经验丰富的 ATE PCB 设计师为确保质量和准确性而采取的一些初步措施。首先,他们必须评估当今的 ATE PCB 中大量装载 BGA 的事实。随着这种设备封装尺寸的不断缩小,这种封装技术已经变得充满活力。不仅 BGA 在缩小,BGA 球之间的引脚间距也在缩小。

五年前,BGA 间距为 1.0 或 0.8 毫米 (mm)。今天,它在 0.25 到 0.3 毫米之间。引脚间距的显着减小转化为 PCB 布局期间具有挑战性的设计约束。因此,更紧密的间距和更小的 BGA 是经验丰富的 ATE PCB 设计人员必须考虑的一个方面。

还要考虑走线宽度变得更窄。两到三年前,走线宽度是七到八密耳。今天,它们已经缩小到三到四密耳。

鉴于这些技术进步,ATE PCB 设计人员必须有足够的经验来确定正确的布局和布线。例如,设计人员正在使用 0.3mm 间距的 BGA。BGA 不能以非常宽的走线扇出的布线。相反,必须使用 3 到 4 mil 的走线。以前的技术是,当走线从 BGA 引出时,它们会以不同的宽度引出。走线出来后,设计师会增加宽度。

但以今天的 BGA 产生的 2.5 或 300 万条迹线为例。设计人员无法将该迹线大幅增加到七或八密耳。结果将是相当大的信号损失或基于变化的宽度的速度或阻抗的变化。因此,精明的设计人员在进行布线和选择差分对宽度或高速走线时需要考虑到这一点。

差分对需要特定的叠层。这些差分对是根据芯片制造商的要求设计的。制造 ATE 板时,制造车间需要确保差分对正确阻抗匹配,并且这些差分对的容差为 5%。

例如,如果差分对匹配 100 欧姆 (Ω) 阻抗,则设计人员允许 5% 的容差,这意味着容差将介于 95 和 105 Ω 之间。如果差分对未根据 ATE PCB 设计人员提供给制造商的阻抗正确匹配,则芯片测试结果将无法达到要求的准确度。

专注于 DUT

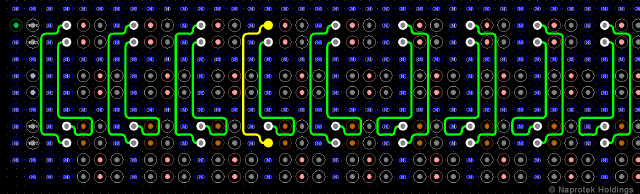

最重要的是,相当多的设计注意力集中在 ATE PCB 的被测设备或 DUT 区域,如图 2所示。在确保设计的早期阶段是正确的之后,设计师会仔细关注三个主要的设计考虑因素——高速走线、曲线布线和长度匹配。

图 2:相当多的设计注意力集中在 ATE PCB 的 DUT 区域。

芯片制造商为高速迹线提供数据。这通常在原理图或规格表中。它包括设计中的高速走线数量,并指定串行/解串器 (SerDes)、环回和带电容器的 SerDes。如图 3所示,环回走线往返于 DUT 的引脚,通常是 BGA 封装。这些走线通常彼此靠近布线,并且长度大致相等,以使它们发挥最佳功能。

图 3:环回走线往返于 DUT 的引脚,通常是 BGA 封装。

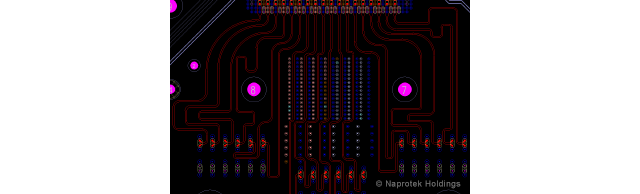

图 4显示了 SerDes 路由。对于高速 SerDes 走线,过孔图案放置在靠近插座的位置,以便走线从 BGA 到过孔,然后再从过孔到 BGA 引脚。高速信号从BGA管脚传输到via pattern,然后再从via pattern到不同的BGA管脚,分别进行信号的传输和接收。

图 4:对于高速 SerDes 走线,过孔图案放置在靠近插座的位置,以便走线从 BGA 到过孔,然后再从过孔到 BGA 引脚

第三种高速走线涉及使用电容器布线 SerDes。走线在两个电容器的两个引脚上终止。然后,迹线再次路由回 BGA 引脚。

较小值和较小的电容器放置在 BGA 上,因为它们具有更快的响应时间。它们被放置在顶部并靠近 BGA 引脚,使它们能够非常快速地启动它们的功能。传统上,将 0201 电容器放置在靠近插座引脚并放置在插座引脚上时,可以使信号传输保持高速。

大会时

质量和精度随后会随着设计进入 PCB 组装车间。 一些领先的 EMS 供应商为芯片制造商提供所谓的以质量为目的的工厂。例如,Naprotek 在其装配线上在整个 ATE 测试板流程中具有几个不同的质量和检查阶段。所有的 PCB,包括 ATE 测试板,都是按照最高的 IPC Class 3 质量标准组装和制造的。

对于编号为 10 或以下的少量电路板,整个过程中的检查阶段包括焊膏检查、首件质量控制 (FA QC) 和表面贴装质量控制 (SMT QC)。第一篇是指最初生产的板,也称为“金板”。

第一步是在板上印刷焊膏并进行焊膏检查以确保焊料沉积足够。然后,一旦将元件放置在未回流焊的板上,它就会经历 FACC,它会检查元件的极性和值。第三,一旦FFCC通过,板子就会进行回流。完成后,第一个文章板将进行 SMT QC。此时,进行 100% 的目视检查以确定焊点质量并检查缺陷。

对于超过 10 块的高数量板,例如 15 或 20 块,质量和检验阶段实际上与少量测试板相同。但是,在 SMT QC 之后还包括另一个检查阶段。这称为自动光学检测或 AOI。在这个阶段,生成了一个 AOI 程序。然后,根据该 AOI 程序检查所有从 SMT 出来的电路板。当电路板从 SMT 转移到 THT(通孔技术)时,所有电路板都经过 TH 加载和选择性焊接。一旦所有的 THT 组件都焊接好后,就会对 TH 组件进行 X 射线检测,以确定桶填充和空洞百分比。配置文件规范在每个流程步骤都进行了调整,以在板上获得最佳结果。

及时向外看

正如我们在这里所说,支持高质量和高精度 ATE PCB 的技术正在迅速发展。鉴于 BGA 封装继续变得更小,有一个时间点,可能需要两到三年,届时将需要引入微电子设计和组装,以创建混合 SMT 和基于微电子的测试板。芯片制造商对倒装芯片和多层引线键合等技术并不陌生,这些技术在微电子组装中变得越来越普遍。因此,被指派执行测试职责的半导体工程管理人员需要与其 ATE PCB 供应商合作,以充分了解他们如何在未来的芯片测试板上取得成功。

审核编辑 黄昊宇

-

protel输出高质量gerber2011-12-12 26136

-

高质量C++、C编程指南2012-08-06 5065

-

高质量C&C++2012-08-16 2719

-

高质量C++&C 编程指南2012-08-19 2484

-

原版PIC实战项目-C(高质量PDF版本)2013-07-10 13677

-

高质量C语言编程2013-07-22 13821

-

编写高质量C语言代码2013-07-31 4696

-

林锐《高质量C语言编程》2013-08-17 2440

-

高质量C++与C编程指南2014-03-09 5419

-

高质量编程2016-02-27 7141

-

【下载】高质量干货-22本高质量EMC电磁兼容性设计资料2020-03-20 5835

-

请问怎么才能设计出高质量的印制线路板?2021-04-23 1504

-

高质量PCB设计理论2009-04-15 1253

-

2019年我国制造企业如何转向高质量发展2019-01-04 1101

-

高质量PCB设计要考虑的因素2020-10-16 2349

全部0条评论

快来发表一下你的评论吧 !