解锁数据中心的系统级节能

电子说

描述

全球大部分 IP 流量都经过数据中心,不断增长的数据处理、存储和传输量正在推动对数据中心服务的需求快速增长。提供这些服务需要能源,随着服务器数量的增长以及这些服务器切换到新的高性能、耗电的处理器,能源需求有可能快速增长。因此,数据中心运营商正在寻找方法来提高处理能力,同时保持尽可能低的功耗。

为了满足这一要求,系统架构师和设计人员在设计处理器电源方案时需要考虑整体系统效率。解决这一挑战的一种方法是提高数据中心机架的功率密度,这可以通过对用于转换和调节直流电压的电源管理 IC (PMIC) 技术采用新方法来帮助实现。

提高效率的动力

几乎每件电子设备中都有一个 DC/DC 转换阶段,实际上,这会损失一些能量。在便携式设备中,这会降低电池寿命和产生过多的热量,而在交流输入设备中,这也意味着增加公用事业能源供应的额外美元成本,从而对环境产生更大的影响。产生的额外热量需要额外的冷却装置,如果不能有效消散,可能会降低产品的可靠性。

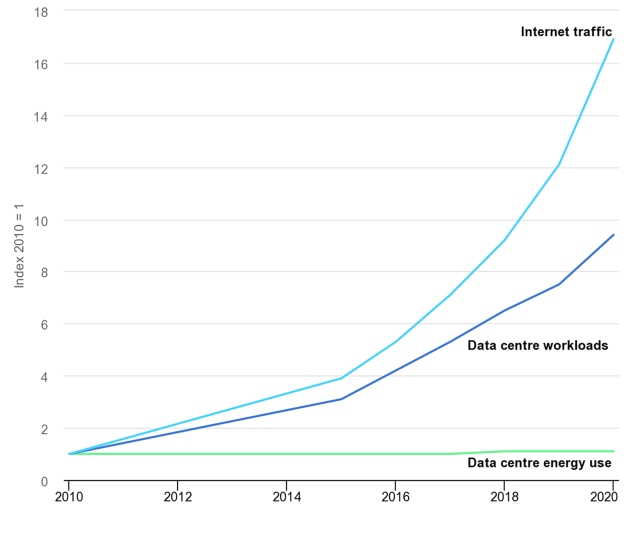

因此,有各种动机来提高 DC/DC 转换效率,尤其是在数据中心,据 IEA 报告称,数据中心消耗了全球约 1% 的能源供应,或 2020 年消耗了 200-250 TWh,可能还会使用另外 100 TWh用于加密货币挖掘。与此同时,数据传输网络在同一时期消耗了 260-340 TWh。1尽管互联网流量以每年约 30% 的速度增长,但由于电力转换效率的提高,这些能源消耗数据在过去 10 年中保持相对平稳(图 1)。

图 1:2010-2020 年互联网流量、数据中心工作负载和数据中心能源使用的全球趋势

然而,情况正在发生变化:最好的超大规模数据中心现在的整体电力使用效率约为 1.1,这意味着 IT 设备每消耗 10 千瓦时,系统供应和冷却仅损失 1 千瓦时。虽然未来功率转换效率会逐步提高,特别是随着宽带隙半导体使用的增加,但随着数据中心升级到最佳实践,进一步的全球收益受到限制。因此,在未来几年,能源需求将开始更直接地随着数据吞吐量而扩大。这给已经面临严重空间限制并需要将更多处理能力(因此,更高的散热量)打包到每个机架中的系统设计人员提出了一个问题。如果功率转换元件也需要增加空间,

DC/DC 功率密度越来越受到关注

因此,在给定体积内测量功率转换器的输出正成为一个重要的设计问题。如果可以提高功率密度,那么可以在不成比例地增加转换器尺寸的情况下增加机架功能。由于电源管理是提高功率密度的关键,因此提高执行工作的 PMIC 的性能已成为一个越来越重要的目标。当涉及到高效率和高功率密度时,提供端负载电压的 DC/DC 转换器是一个焦点。此处的任何损耗都会在电源系统中向上游传播,因为在总线转换器和 AC/DC 以及功率因数校正阶段会进一步损耗能量。同时,这些负载点 (PoL) 转换器还需要尽可能靠近其负载以避免电压下降。由于现代处理器在大电流下需要低于 1V 的电源轨,公差已经很紧了。如果事情还不够困难,负载 IC 需要在其周围的 PCB 中为数据和地址总线提供空间,并且需要高性能冷却,从而为电源转换器留下很小的空间。

因此,PoL 转换器需要最大化功率并最小化尺寸。当开关稳压器从固有损耗的线性类型中接管时,可以看到一条清晰的路径,以接近零损耗;半导体开关在关闭时不会消耗任何能量,而在开启时几乎不会消耗,随着技术的进步和设备并联,即使这种损耗也会减少。虽然半导体效率有所提高,但实际上无源元件已成为尺寸的限制,因此也限制了功率密度。大多数开关稳压器都需要一个电感器和输入/输出电容器,这些电容器的尺寸往往会随着所需功率而增大,而随着开关频率而减小。出于这个原因,更高的频率可以更好地减少占位面积,但随后半导体动态损耗开始增加,从而损害效率。此外,在较高的开关速率下,电感器磁芯损耗和电容器寄生损耗会显着增加。因此,PoL 转换器必须以折衷的频率运行,通常最多不超过几兆赫兹。

诱人的是,在非常高的频率下,必要的电感可以非常低,以至于不需要有损耗的磁芯,并且在减小的环路直径中只需要几匝——这可以在 PCB 跟踪的小区域内实现。最新的电容器技术还导致高频所需的低值进一步小型化。剩下的问题是半导体开关损耗将效率降低到一个不可行的值。现在,Empower Semiconductor 开发的一种新的集成稳压器 (IVR) 技术改变了这种情况。3

功率密度突破

新的 IVR 技术通过使用获得专利的、可数字配置的多相谐振开关方法解决了开关损耗挑战,该方法可最大限度地减少导致开关转换时耗散的电压和电流重叠。基于具有嵌入式硅电容器的先进 CMOS 几何结构,这允许在低数百兆赫范围内运行,并且在整个负载范围内具有几乎平坦的高效率。器件的效率峰值为 91%,其输入电压为 1.8V,可编程输出电压范围为 0.5V 至 1.2V,额定电流为 10A 连续电流,15A 峰值电流。所有这些都是在具有 5 × 5-mm PCB 占位面积和仅 0.75 mm 轮廓的倒装芯片芯片级封装 (FcCSP) 中实现的。全额定性能不需要分立的外部元件,与形成在主板铜跟踪中的无芯电感器,通常在 IVR 封装下方。采用 8 × 10-mm LGA 封装的部件具有集成电感器。与竞争部件相比,所实现的 FcCSP 芯片占位面积减少了 10 倍,这意味着它可以安装在更靠近负载的位置,甚至可以直接安装在 SoC 基板上。

其他优势

一个设计经验法则是,开关电源控制环路的带宽不应大于开关频率的大约五分之一到十分之一,以避免不稳定。这导致在亚和低兆赫范围内看到的典型开关频率的环路响应时间为数百微秒。输出电流压摆率也受到低频所需的大输出电感的限制。Empower 设计以非常低的电感值在如此高的频率下切换,使得环路响应约为 500 ns。此时电流可以从 0 A 转换到 10 A,电压偏移小于 15 mV,而之前的 PoL 模块技术约为 50 mV。无需额外的外部电容器即可实现这一性能。

由于该设计允许负载阶跃的最小电压瞬变,并且非常小,以至于它可以安装在非常靠近最终负载的地方,并且电压降很小,因此可以将输出标称电压设置为比以前更低,因为所需的电压开销更少。这可能会节省负载的能量。

超快速动态电压缩放

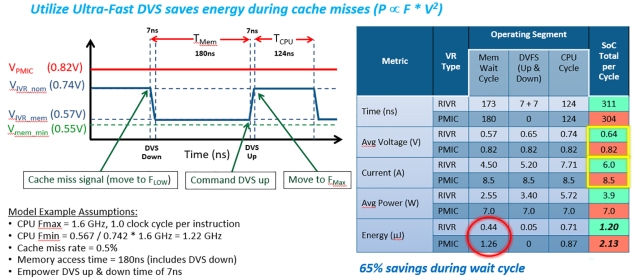

快速控制环路还允许非常快速的动态电压缩放 (DVS),其中负载(通常是处理器)可以通过数字接口请求动态改变轨道电压,以最大限度地降低整体功耗。

例如,在等待缓存数据时,可以放下铁轨以减少耗散。图 3 显示了 Empower 部件在标称电压 (V IVR nom ) 和节能电压 (V IVR mem ) 之间的转换时间为 7 ns,从而在时钟继续进行的同时将每个等待周期的能耗降低了 65%。具有 DVS 功能的前几代 PoL 转换器比 Empower 部件慢约 1,000 倍,并且反应不够快,无法利用这一点。V PMIC是老一代 PoL 转换器所需的电压,设置得更高以允许可能的电压偏移与负载瞬变,并且在 180 ns 等待周期内无法通过 DVS 做出反应。

图 3:Empower 的 IVR 可以在 7 ns 内从 V IVR nom转换到 V IVR mem。

实际实施显示显着减少了占用空间

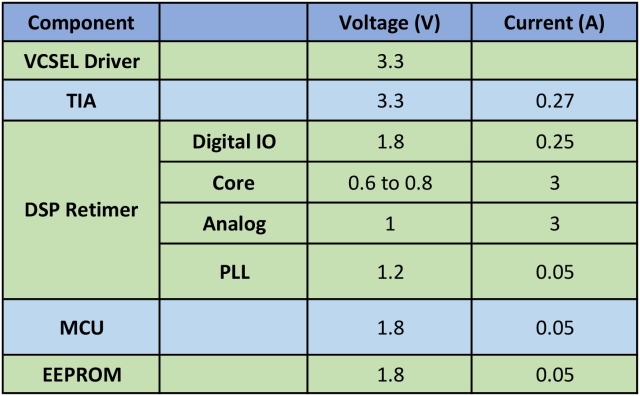

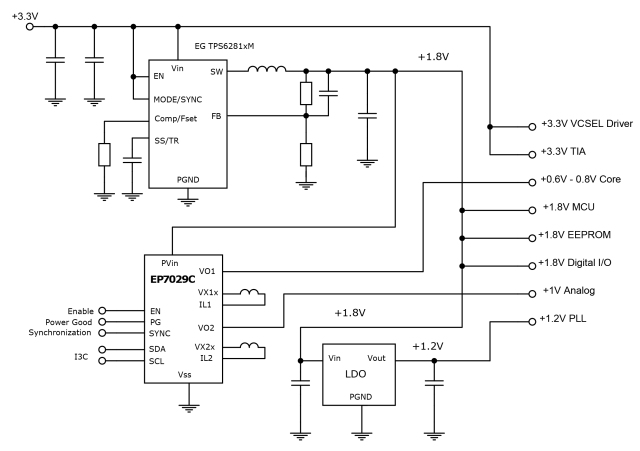

Empower IVR 部件在 1.8V 标称输入下运行,因此需要在系统级别与竞争 PoL 进行比较才有意义。例如,考虑图 4 中描述的 DSP 芯片电源树。

图 4:典型的 DSP 电源树

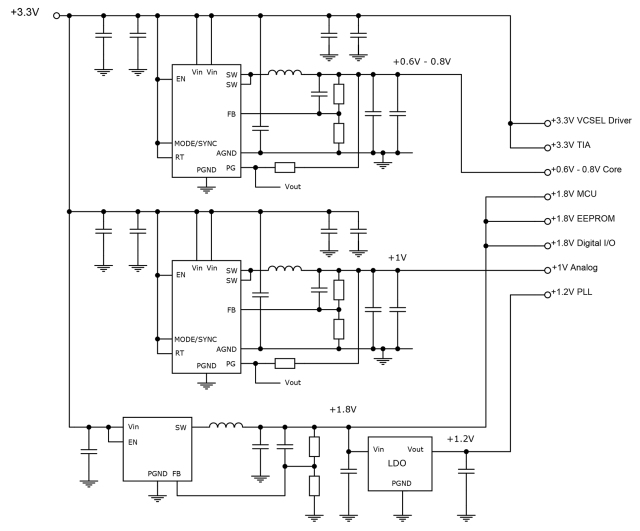

图 5 显示了满足此要求的典型电源实现方案。它使用 36 个分立元件并占用约 360 mm 2的电路板空间。但是,当使用 Empower 部件实现时,图 6 中的原理图结果是,在 155-mm 2的电路板区域中只有 14 个分立元件。

图 5:图 4 的电源树,使用现有 PoL 技术实现

图 6:图 4 的电源树,使用 Empower 的 EP7029C IVR 实现

尽管尺寸很小,但 Empower IVR 包括全面的功能——提供使能输入和电源良好输出以及提供功能遥测的 I 3 C 数字接口,以及根据需要动态编程输出电压的能力。演示板带有用于设置和监控的 GUI。这些部件还具有针对外部故障和过热的全面保护。Empower IVR 提供单路、双路和三路独立稳压输出,并采用 FcCSP 和 LGA 封装样式。

概括

我们已经看到 DC/DC 转换器如何需要在紧凑的电子设备中具有更高的功率密度,例如现代数据中心使用的机架。过去,通过提高开关频率和减小分立元件的尺寸来实现这一点通常意味着半导体效率必须受到影响。因此,操作通常仅限于使用常用部件的几兆赫兹。

然而,现在,集成稳压器的可用性正在帮助解决这个问题,方法是在非常高的开关频率下保持高效率,并逐步提高功率密度。这些 IVR 将高度集成与快速瞬态响应和行业领先的 DVS 性能相结合,可满足现代高端处理要求的需求,同时提高整体系统效率。

审核编辑:郭婷

-

数据中心机房冷冻水空调系统的组成和节能设计2023-11-20 10557

-

iCooling,数据中心AI系统级节能专家2023-10-28 1503

-

浅析数据中心能耗现状与节能方向的研究2023-02-24 1927

-

数据中心机房节能运行现状与问题分析2022-02-18 3776

-

数据中心供配电系统的节能设计及监控产品选型2022-01-04 1438

-

什么是数据中心2021-09-15 2301

-

典型的数据中心供电系统组成部分2021-09-10 3240

-

数据中心是什么2021-07-12 2112

-

数据中心太耗电怎么办2021-06-30 1745

-

未来数据中心与光模块发展假设2020-08-07 2991

-

国际数据中心及云计算产业展览会2018-09-12 1999

-

飞速(FS)数据中心级交换机为什么受欢迎?2017-10-16 3957

-

数据中心子系统的组成2011-11-11 5825

-

基于预测的数据中心应用服务节能调度系统2011-09-21 592

全部0条评论

快来发表一下你的评论吧 !