富昌电子SiC设计分享(四):SiC MOSFET Desat设计注意事项

移动通信

314人已加入

描述

富昌电子(Future Electronics)一直致力于以专业的技术服务,为客户打造个性化的解决方案,进而缩短产品的设计周期、加快行业发展的步伐。在第三代半导体的实际应用领域,富昌电子结合自身的技术、项目经验积累,着笔SiC相关设计的系列文章,希望能给到大家一定的参考,并期待与您进一步的交流。

作为系列文章的第四篇,本文主要针对SiC MOSFET 短路Desat 保护设计做一些探讨。

1. 什么是Desat

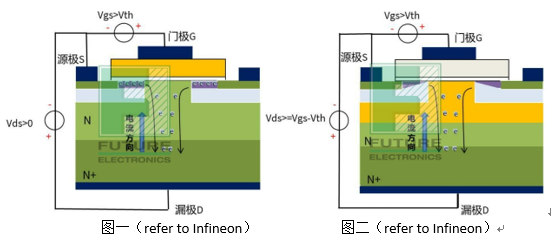

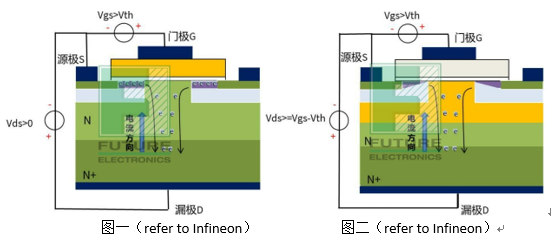

Desat保护是功率MOSFET和IGBT保护中很重要的概念, 下面我们用图一所示是一个简化的MOS剖面图,以此来阐述退饱和发生的原因。栅极施加一个大于阈值的正压VGS,则栅极氧化层下方会形成导电沟道,这时如果给漏极D施加正压VDS,则源极中的电子便会在电场的作用下源源不断地从漏极D流向源极S,这样电流便形成了,这时电流随DS电压的增长而线性增长。随着DS电压的增大,使得栅极和硅表面的电压差很小而不能维持硅表面的强反型,沟道出现夹断现象,电流不再随DS电压的增加而成比例增长,而进入退饱和状态(如图二)。

在实际应用 中,退饱和现象一般发生在器件短路时,这时Vds电压上升到母线电压,电流一般是额定电流的几倍。功率异常增大,结温急剧上升,不及时关断器件就有可能烧毁器件。多数MOSFET电流短路承受能力差而造成热损坏,而SiC MOSFET电流的短路能力更差。那么针对SiC MOSFET的Desat保护设计就变得尤为重要了。

2. 如何进行Desat的设计

SiC MOSFET电路通常用传感器进行在线电流检测,进行精确的过电流保护。而Desat保护被视为第二级保护措施。在有些特殊故障情况,例如桥式直通或逆变器在滤波器前输出端对地短路等,在线电流传感器无法检测到这类故障,Desat保护就成为保护功率器件重要的措施。

设计中,主要的考虑是Desat保护阈值的设定,一般应设置为保守值,以避免过早触发。下面就通过onsemi的SiC MOSFET NTH4L020N120SC1为例,来论述下如何设计这个保护阈值。

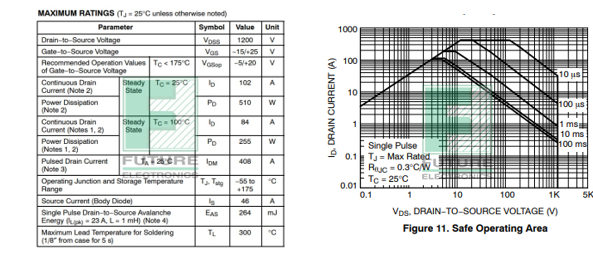

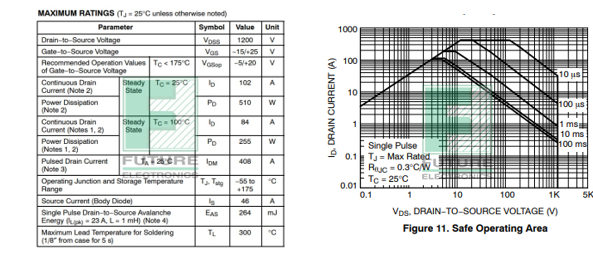

SiC MOSFET datasheet提供“最大漏极脉冲电流”(10us单脉冲)如图一。该电流约为器件在 125 °C时额定连续电流的 4 倍左右(onsemi NVH4L020N120SC1) 如图二。在额定连续电流和最大漏极脉冲电流之间选择过流保护值。过流保护阈值的计算应使用 125 °C 或 150 °C 时的 RDS_ON。传导电流是 DESAT 引脚提供的电流。二极管压降具有负温度系数。保守计算,可以将 25 °C 时二极管 的正向电压用于过流保护阈值的计算。

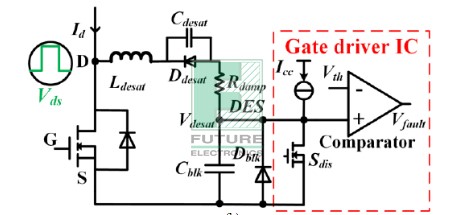

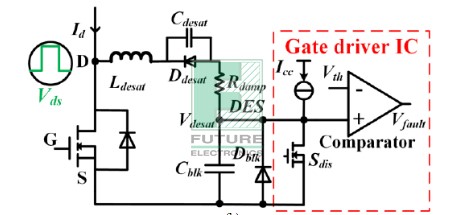

如图三所示, 设置限流值的时候,可以用公式 Ilimit = (Vth – Rdamp* IDESAT – VFD)/ Rdson 来计算, 其中 Rdamp 为调压电阻,VFD为高压二极管的正向压降,Rdson为 SiC MOSFET 估算结 温下的导通电阻。 当发生短路或过流时,SiC MOSFET 漏极电流将会增加 到一个很高的值,并且器件的 Vds 将会升高到很高的值。钳位DESAT 引脚通过内电流源给消隐电容 Cblk 充电到更高的电压。当电压达到过流保护阈值时,OUT 和/FAULT 均被拉低。通过选择不同的消隐电容,可以设置DESAT 保护电消隐时间。消隐时间可以公式计算: Teblk = Cblk ∙Vth / IDESAT。 不同的应用通常需要不同的关断时间。优化的关断时间可以最大化地发挥系统的短路 能力,同时限制 Vds 和 bus 电压上的振荡。

图三

3. Desat 保护设计注意事项:

a. SiC mosfet 的高dv/dt 是引起噪声和desat误触发主要原因。在高的Vds dv/dt 作用下,高压阻断二极管 D寄生电容 Cdesat 引 起的电压耦合会显著抬高或降低阳极电压 。 阳极电压变化又会将 消隐电容 Cblk充电或放电到一个非预期值,并导致误触发或 desat 保护延迟。由于 SiC MOSFET 的高开关速度,这个问题变得更加严重。为了钳制 Vdsat 电压的上升幅度,使用一个 稳压二极管。为了最大程度地降低 Cdesat 的影响,使用低结电容的二极管电压阻断非常必要。

b. 与高压阻断二极管串联的寄生电感Ldesat也是必须考虑的因素,过高的Ldesat 会与二极管寄生电容Cdesat谐振,会影响Vdesat震荡的最大值的变化。从而影响desat触发的准确性。降低Ldesat值也是尤为重要。

c. 要具有稳定和快速的短路保护,上管驱动器和下管驱动器都应该具有desat保护。半桥的短路情况主要有两种情况。一种情况是一个开关管已经导通情况下,开通另一个开关管;另一种情况是在一个开关管短路的情况下,开通另一个开关管。对于第二种情况,比第一种情况的延迟时间长得多,是工程师必须考虑的极端因素。

总结:

SiC mosfet Desat保护得到越来越多工程师的重视,以上是SiC mosfet Desat保护设计基本思路。由于各个原厂的SiC mosfet 驱动的Desat保护参数会有不同,具体产品应用会有调整,如需要进一步交流请联系富昌电子技术方案中心。

(链接: https://biaodan100.com/web/formview/6286e84a75a03c5d1e0da67b)

查看该系列其他文章,请扫码访问:

关键字: 碳化硅,SiC,SiC MOSFET,驱动设计,Desat,新能源汽车,储能,富昌电子

参考文献:

【1】 AN1306: Driving SiC MOSFET Switches Using the Si828x Isolated Gate Driver

【2】 Understanding the Short Circuit Protection for Silicon Carbide MOSFETs

【3】 Comprehensive Analysis and Improvement Methods of Noise Immunity of Desat Protection Circuitry for High Voltage SiC MOSFETs with High dv/dt

【4】 TND6237/D- SiC MOSFETs: Gate Drive Optimization

打开APP阅读更多精彩内容

作为系列文章的第四篇,本文主要针对SiC MOSFET 短路Desat 保护设计做一些探讨。

1. 什么是Desat

Desat保护是功率MOSFET和IGBT保护中很重要的概念, 下面我们用图一所示是一个简化的MOS剖面图,以此来阐述退饱和发生的原因。栅极施加一个大于阈值的正压VGS,则栅极氧化层下方会形成导电沟道,这时如果给漏极D施加正压VDS,则源极中的电子便会在电场的作用下源源不断地从漏极D流向源极S,这样电流便形成了,这时电流随DS电压的增长而线性增长。随着DS电压的增大,使得栅极和硅表面的电压差很小而不能维持硅表面的强反型,沟道出现夹断现象,电流不再随DS电压的增加而成比例增长,而进入退饱和状态(如图二)。

在实际应用 中,退饱和现象一般发生在器件短路时,这时Vds电压上升到母线电压,电流一般是额定电流的几倍。功率异常增大,结温急剧上升,不及时关断器件就有可能烧毁器件。多数MOSFET电流短路承受能力差而造成热损坏,而SiC MOSFET电流的短路能力更差。那么针对SiC MOSFET的Desat保护设计就变得尤为重要了。

2. 如何进行Desat的设计

SiC MOSFET电路通常用传感器进行在线电流检测,进行精确的过电流保护。而Desat保护被视为第二级保护措施。在有些特殊故障情况,例如桥式直通或逆变器在滤波器前输出端对地短路等,在线电流传感器无法检测到这类故障,Desat保护就成为保护功率器件重要的措施。

设计中,主要的考虑是Desat保护阈值的设定,一般应设置为保守值,以避免过早触发。下面就通过onsemi的SiC MOSFET NTH4L020N120SC1为例,来论述下如何设计这个保护阈值。

SiC MOSFET datasheet提供“最大漏极脉冲电流”(10us单脉冲)如图一。该电流约为器件在 125 °C时额定连续电流的 4 倍左右(onsemi NVH4L020N120SC1) 如图二。在额定连续电流和最大漏极脉冲电流之间选择过流保护值。过流保护阈值的计算应使用 125 °C 或 150 °C 时的 RDS_ON。传导电流是 DESAT 引脚提供的电流。二极管压降具有负温度系数。保守计算,可以将 25 °C 时二极管 的正向电压用于过流保护阈值的计算。

图一, NTH4L020N120SC1 , onsemi 图二, NTH4L020N120SC1 , onsemi

如图三所示, 设置限流值的时候,可以用公式 Ilimit = (Vth – Rdamp* IDESAT – VFD)/ Rdson 来计算, 其中 Rdamp 为调压电阻,VFD为高压二极管的正向压降,Rdson为 SiC MOSFET 估算结 温下的导通电阻。 当发生短路或过流时,SiC MOSFET 漏极电流将会增加 到一个很高的值,并且器件的 Vds 将会升高到很高的值。钳位DESAT 引脚通过内电流源给消隐电容 Cblk 充电到更高的电压。当电压达到过流保护阈值时,OUT 和/FAULT 均被拉低。通过选择不同的消隐电容,可以设置DESAT 保护电消隐时间。消隐时间可以公式计算: Teblk = Cblk ∙Vth / IDESAT。 不同的应用通常需要不同的关断时间。优化的关断时间可以最大化地发挥系统的短路 能力,同时限制 Vds 和 bus 电压上的振荡。

图三

a. SiC mosfet 的高dv/dt 是引起噪声和desat误触发主要原因。在高的Vds dv/dt 作用下,高压阻断二极管 D寄生电容 Cdesat 引 起的电压耦合会显著抬高或降低阳极电压 。 阳极电压变化又会将 消隐电容 Cblk充电或放电到一个非预期值,并导致误触发或 desat 保护延迟。由于 SiC MOSFET 的高开关速度,这个问题变得更加严重。为了钳制 Vdsat 电压的上升幅度,使用一个 稳压二极管。为了最大程度地降低 Cdesat 的影响,使用低结电容的二极管电压阻断非常必要。

b. 与高压阻断二极管串联的寄生电感Ldesat也是必须考虑的因素,过高的Ldesat 会与二极管寄生电容Cdesat谐振,会影响Vdesat震荡的最大值的变化。从而影响desat触发的准确性。降低Ldesat值也是尤为重要。

c. 要具有稳定和快速的短路保护,上管驱动器和下管驱动器都应该具有desat保护。半桥的短路情况主要有两种情况。一种情况是一个开关管已经导通情况下,开通另一个开关管;另一种情况是在一个开关管短路的情况下,开通另一个开关管。对于第二种情况,比第一种情况的延迟时间长得多,是工程师必须考虑的极端因素。

总结:

SiC mosfet Desat保护得到越来越多工程师的重视,以上是SiC mosfet Desat保护设计基本思路。由于各个原厂的SiC mosfet 驱动的Desat保护参数会有不同,具体产品应用会有调整,如需要进一步交流请联系富昌电子技术方案中心。

(链接: https://biaodan100.com/web/formview/6286e84a75a03c5d1e0da67b)

查看该系列其他文章,请扫码访问:

关键字: 碳化硅,SiC,SiC MOSFET,驱动设计,Desat,新能源汽车,储能,富昌电子

参考文献:

【1】 AN1306: Driving SiC MOSFET Switches Using the Si828x Isolated Gate Driver

【2】 Understanding the Short Circuit Protection for Silicon Carbide MOSFETs

【3】 Comprehensive Analysis and Improvement Methods of Noise Immunity of Desat Protection Circuitry for High Voltage SiC MOSFETs with High dv/dt

【4】 TND6237/D- SiC MOSFETs: Gate Drive Optimization

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

富昌电子SiC设计分享(二):碳化硅器件驱动设计之寄生导通问题探讨2022-06-16 110117

-

富昌电子SiC设计分享(三):SiC MOSFET 和Si MOSFET寄生电容在高频电源中的损耗对比2022-07-07 3233

-

SiC MOSFET并联运行实现静态均流的基本要求和注意事项2025-05-23 2154

-

富昌电子SiC设计分享(一):SiC MOSFET驱动电压的分析及探讨2022-05-30 8921

-

关于SiC MOSFET短路Desat保护设计2022-07-30 4825

-

SiC MOSFET驱动电路设计注意事项2025-04-24 2812

-

富昌电子SiC设计分享(五):SiC MOSFET 相关应用中的EMI改善方案2022-08-30 1821

-

富昌电子SiC设计分享(六):ESS 储能系统中SiC器件的应用2022-09-28 1868

-

为何使用 SiC MOSFET2017-12-18 6045

-

SiC-MOSFET的应用实例2018-11-27 6072

-

SiC-MOSFET与Si-MOSFET的区别2018-11-30 11061

-

SiC功率器件SiC-MOSFET的特点2019-05-07 5705

-

浅析SiC-MOSFET2019-09-17 6425

-

测量SiC MOSFET栅-源电压时的注意事项2022-09-20 20044

-

SiC外延生长技术的生产过程及注意事项2024-11-14 2798

全部0条评论

快来发表一下你的评论吧 !