如何在VHDL中实现一个简单的寄存器

存储技术

描述

寄存器是设备中用于存储数据的常见电子元件。这些是最小的数据保存元素,用于存储 CPU 正在处理的操作数或指令。有不同类型的寄存器,即指令寄存器、程序寄存器、ALU 寄存器、通用寄存器等。它们在可以存储的位数上有所不同,具体取决于系统的配置。在本教程中,我们将学习如何在 VHDL 中实现一个简单的寄存器。

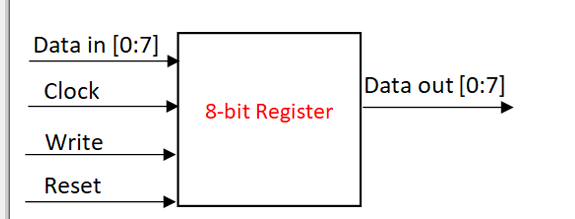

寄存器:寄存器是顺序存储器存储设备。在这里,术语顺序是指“它是一个时钟电路”,这意味着它是由时钟控制的。这些寄存器的大小因系统而异(有些可能是 8 位,有些可能是 4 位)。除此之外,寄存器还有一个数据输入和数据输出端口。还可以使用用于擦除寄存器内容的复位引脚和用于将数据写入寄存器的写信号。因此,典型的寄存器将具有时钟、写入、复位、数据输入和数据输出端口。下面给出了 8 位寄存器的示意图。

由于它是一个时钟电路,因此只有在时钟有效(clock=”1”)且写入信号有效(write=”1”)时才会加载数据。当复位信号为高电平时(reset=”1”),存储的数据将被擦除,分配到“00000000”。

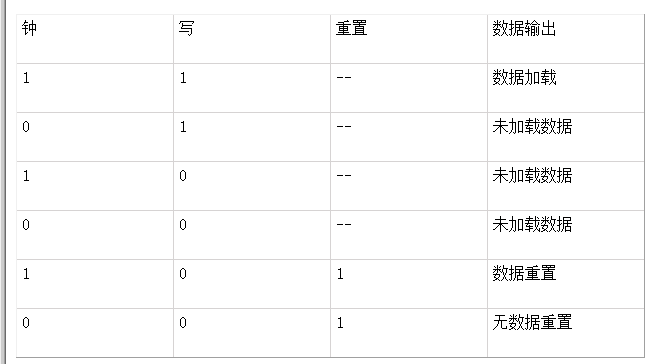

下面给出了发生的有关时钟、写入和复位的事件。

现在我们了解了寄存器的基础知识,我们将了解如何在 VHDL 中实现它们。

如何在 VHDL 中实现寄存器?

首先,我将给出寄存器的完整代码,我们将把它们分解成更小的片段以便更好地理解。

寄存器的 VHDL 代码

图书馆 IEEE;

使用 IEEE.std_logic_1164.all;

实体 reg_a 是

端口 ( signalrega_input :in std_logic_vector(7 downto 0) ;

信号令:在 std_logic 中;

信号复位:在 std_logic 中;

信号 clk:在 std_logic 中;

信号 rega_output: out std_logic_vector(7 downto 0)

);

结束 reg_a;

reg_a 的架构 sim 是

开始

进程(clk)是

开始

如果上升沿(clk)那么

如果(令状='1')那么

雷加输出<=雷加输入;

elsif(reset='1') 然后

rega_output<="00000000";

万一;

万一;

结束进程;

结束模拟;

首先,导入库,使用标签“reg_a”声明实体,并声明数据输入、数据输出、时钟、写入和复位信号。

图书馆 IEEE; 使用 IEEE.std_logic_1164.all; 实体 reg_a 是 端口 ( signalrega_input :in std_logic_vector(7 downto 0) ; 信号令:在 std_logic 中; 信号复位:在 std_logic 中; 信号 clk:在 std_logic 中; 信号 rega_output: out std_logic_vector(7 downto 0) ); 结束 reg_a;

之后,我们用与实体标签“reg_a”关联的标签“sim”声明了架构。

Process(clk):由于整个电路依赖于时钟的功能,我们必须对时钟进行处理。

ifrising_edge(clk) then: “rising_edge(clk)” 表示时钟信号为“1”的点。因此,只有当时钟信号为“1”时,它才会传递到下一个“if”条件。

给出了有关写入和复位的“if”条件。因此,如果写入信号为“1”,则将加载数据。如果复位信号为“1”,则数据将被复位为“0000000”。

注意:当reset=1时,永远记得设置write=0,只有这样数据才会被重置。

reg_a 的架构 sim 是

开始

进程(clk)是

开始

如果上升沿(clk)那么

如果(令状='1')那么

雷加输出<=雷加输入;

elsif(reset='1') 然后

rega_output<="00000000";

万一;

万一;

结束进程;

结束模拟;

只需将此代码复制粘贴到 ModelSim 中,然后编译和仿真即可。编译和仿真过程请参考“使用ModelSim实现基本逻辑门”。

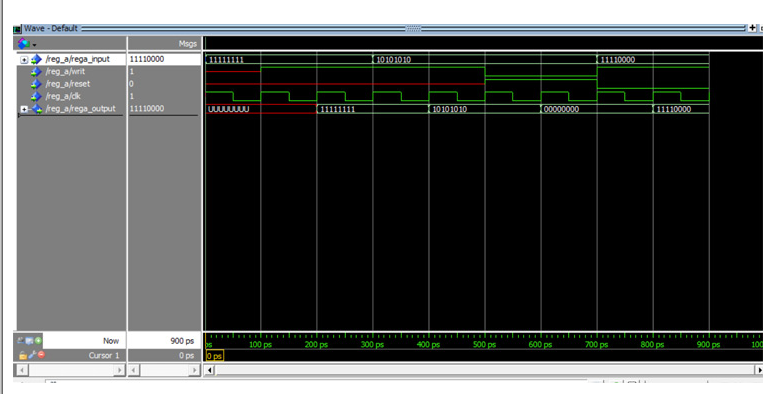

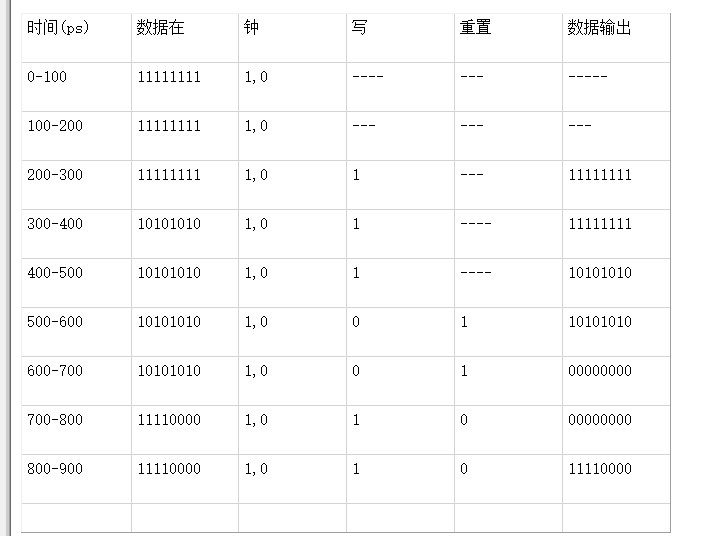

我刚刚编译并仿真了代码,得到如下波形。

只需沿着波形移动光标,我们可以看到只有时钟和写信号都为1时数据才会被存储。‘U’代表未定义。此外,由于它是一个时序电路,更新内容会有一些最小延迟,但它会在下一个正时钟周期内更新。

代码

图书馆 IEEE;

使用 IEEE.std_logic_1164.all;

实体 reg_a 是

端口(信号 rega_input :in std_logic_vector(7 downto 0) ;

信号写:在 std_logic 中;

信号复位:在 std_logic 中;

信号 clk:在 std_logic 中;

信号 rega_output:out std_logic_vector(7 downto 0)

);

结束 reg_a;

reg_a 的架构 sim 是

begin

process(clk) is

begin

ifrising_edge(clk) then

if(writ=‘1’) then

rega_output《=rega_input;

elsif(reset=‘1’) 然后

rega_output《=“00000000”;

万一;

万一;

结束进程;

结束模拟;

-

寄存器寻址的实现方式2024-07-12 2511

-

如何在shell中操作寄存器2023-09-26 2128

-

如何使用ALU,RAM,寄存器打造一个CPU 32023-01-30 2144

-

解析CPU中的寄存器2022-09-19 5250

-

五个广泛使用的特殊寄存器2022-06-08 5852

-

GPIO寄存器2021-12-08 1402

-

如何在C代码中插入寄存器?2021-02-02 4010

-

寄存器的特性和四大种类2020-06-19 20778

-

如何在SPI寄存器中配置一个值?2020-03-18 1353

-

使用VHDL实现移位寄存器的资料和工程文件免费下载2019-08-09 1087

-

如何在项目中使用移位寄存器2019-07-15 2175

-

一文解析Matlab如何实现移位寄存器2018-04-26 18060

-

8位移位寄存器vhdl代码2017-12-22 17611

-

寄存器与移位寄存器2010-03-12 986

全部0条评论

快来发表一下你的评论吧 !