VDD波形传递了什么“密码”

描述

大家单片机玩得很溜了,平时也很少去关注VDD波形,整机测试无异常就完事了。也确实,芯片技术发展多年,芯片厂家对芯片可靠性也做足了功夫,VDD上的波动一般不影响单片机工作。但是,作为一个细心、负责的电子工程师,日常开发工作中,还是应该多了解一下自己设计的单片机系统,其VDD波形究竟如何。如果有异常的波动,应该找出原因并评估风险,有些比较严重的掉电或波动,应该通过改进电路来保证整机可靠性。

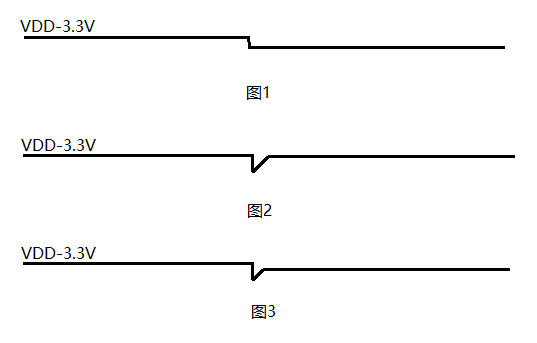

下面举三个VDD波动的例子。如下三图所示(图2、图3中的下凹为us级)大家可以试试判断VDD上发生了什么事情,VDD波形传递了什么“密码”。

图1中,VDD电平被拉低,通常是VDD供电域中,某个(或某些)模块或电路开启运行且功耗很大,即整个VDD域的整体需求电流增加,而VDD前端的LDO或电源输出能力有限(内阻较大),最终看到VDD电平下降(大家可用电阻分压模型来理解下)。

图2中,VDD电平被拉低几十~几百us然后恢复原电平值。通常是VDD供电域中,某个(或某些)模块或电路接入或开启,而这个模块或电路上有大电容,在接入或开启的瞬间,大电容相当于短路到地,电流很大,VDD电平被拉下;但这个模块或电路工作时的功耗并不高,VDD前端的LDO或电源输出能够应付,所以VDD电平随后恢复到原值。

图3中,VDD电平被拉低几十~几百us然后恢复不到原电平值。通常是VDD供电域中,某个(或某些)模块或电路接入或开启,而这个模块或电路上有大电容,在接入或开启的瞬间,大电容相当于短路到地,电流很大,VDD电平被拉下;某个(或某些)模块或电路工作时的功耗很高,即整个VDD域的整体需求电流增加,而VDD前端的LDO或电源输出能力有限(内阻较大),最终看到VDD电平比之前有所下降。

以上只是举例说明VDD波形上的变化其实提供了很多关键信息,这些信息可让大家更了解自己的电路,指导我们如何改进电路,如何提高可靠性。

下次大家抓取到VDD上的波形,不妨多分析多思考VDD的“密码”。

-

LSE的波形幅值范围是多少?2025-03-12 639

-

上电缓慢或有阶梯?如何判断上电波形是否满足MCU要求2024-02-19 3040

-

光耦的工作原理 光耦的CTR概念 光耦的传递时延2023-03-17 13767

-

卫士通大力推动密码科普宣传向网络延伸、向民众传递2022-09-15 2038

-

利用ADC量测VDD电压2022-06-30 784

-

VCC、VDD、VSS2021-12-01 1599

-

VCC、VDD、VSS的区别2021-03-18 2256

-

Labview生产者消费者模式—仅成功传递了一次数据怎么办2020-11-19 3892

-

斜率的传递函数:电流模式的传递函数和各模式的总结2018-11-30 3062

-

电路原理图中VCC,VDD,VEE,VSS有什么区别2016-08-22 112801

-

Labview之信号传递后波形2016-04-19 604

-

labview波形传递(新手)2016-03-17 2331

-

VCC、VDD、VEE、VSS的区别2011-09-05 353274

-

密码技术,密码技术原理是什么?2010-03-20 1511

全部0条评论

快来发表一下你的评论吧 !