【RT-Thread学习笔记】RISC-V汇编基础三大块知识

【RT-Thread学习笔记】RISC-V汇编基础三大块知识

描述

1 前言

玩嵌入式的,或多或少都接触ARM。

但是近些年随着科技的发展,CPU的架构家族中,新增了一个叫RISC-V的家伙。

RISC-V(读作“RISC-FIVE”)是基于精简指令集计算(RISC)原理建立的开放指令集架构(ISA),V表示为第五代RISC(精简指令集计算机),表示此前已经四代RISC处理器原型芯片。每一代RISC处理器都是在同一人带领下完成,那就是加州大学伯克利分校的David A. Patterson教授。与大多数ISA相反,RISC-V ISA可以免费地用于所有希望的设备中,允许任何人设计、制造和销售RISC-V芯片和软件。它虽然不是第一个开源的的指令集(ISA),但它很重要,因为它第一个被设计成可以根据具体场景可以选择适合的指令集的指令集架构。基于RISC-V指令集架构可以设计服务器CPU,家用电器cpu,工控cpu和用在比指头小的传感器中的cpu。

更多详细介绍,请参考百度百科,RISC-V简介.

2 RISC-V知识图谱

本文先列个大纲,后续有时间再补充。

3 RISC-V汇编基础三大块

这里整理了RISC-V汇编中非常基础的三大块知识,了解了这三大块内容基本可以看懂甚至编译一些简单的汇编程序。

3.1 寻址方式

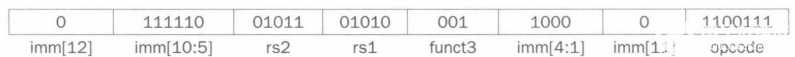

RISC-V分支指令寻址,在之前的B类型指令就是其中之一。 这种格式可以表示从-4096到4094的分支地址,以2的倍数表示。B型格式包括一个7位操作码、一个3位功能码、两个5位的寄存器操作数( rs1和 rs2)和一个12位地址立即数。该地址使用特殊的编码方式,简化了数据通路设计,但使组装变得复杂。下面这条指令

-

bne x10,x11,2000 // if x10 != xll,go to location 2000 = 0111 1101 0000

其中条件分支的操作码是11001112,而bne 的funct3码是0012 RISC-V的无条件跳转–链接指令(jal),是分支寻址的另一种方法,也是唯一使用J型格式的指令。该指令由一个7位操作码、一个5位目标寄存器操作数(rd)和一个20位地址立即数组成。链接地址,即jal之后的指令的地址,被写入rd 中。

如果程序的地址必须适合这个20位字段,则意味着没有程序可能大于220,所以另一种方法是指定一个与分支地址偏移量相加的寄存器,这样就允许程序大到264,并且仍然能够使用条件分支指令,以便分支指令可以按如下来计算:

程序计数器=寄存器内容+分支地址偏移量 这样就允许程序大到2^64,并且仍然能够使用条件分支指令

立即数寻址,操作数是指令本身的常量。 寄存器寻址,操作数在寄存器中。 基址或偏移寻址,操作数于内存中,其地址是寄存器和指令中的常量之和。 PC相对寻址,分支地址是PC和指令中常量之和。 注: 加载和存储对字节、半字、字或双字的访问有不同的版本。

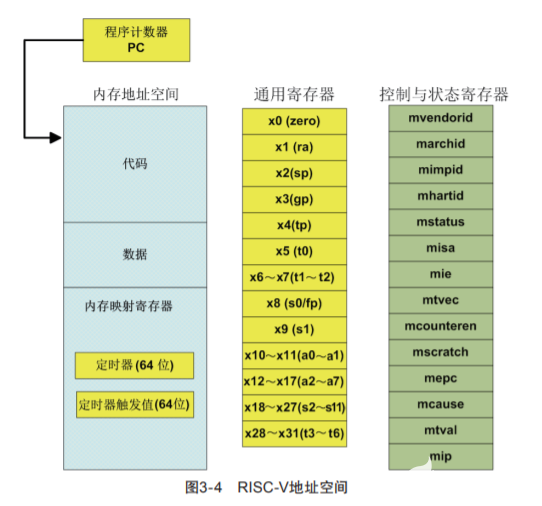

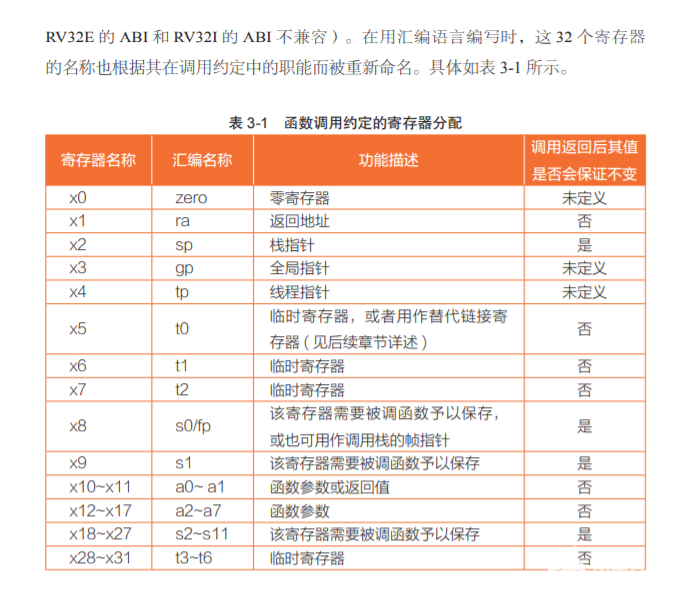

3.2 寄存器的用途

3.2.1 RISC-V的寄存器列表

3.2.2 RISC-V寄存器在汇编代码中使用

3.3 汇编指令

RISC-V有六种基本指令格式:

- R 类型指令,用于寄存器-寄存器操作

- I 型指令,用于短立即数和访存 load 操作

- S 型指令,用于访存 store 操作

- B 类型指令,用于条件跳转操作

- U 型指令,用于长立即数

- J 型指令,用于无条件跳转

4 更多分享

欢迎关注我的github仓库01workstation,日常分享一些开发笔记和项目实战,欢迎指正问题。

同时也非常欢迎关注我的CSDN主页和专栏:

【CSDN主页:架构师李肯】

【RT-Thread主页:架构师李肯】

【C/C++语言编程专栏】

【GCC专栏】

【信息安全专栏】

【RT-Thread开发笔记】

【freeRTOS开发笔记】

【BLE蓝牙开发笔记】

【ARM开发笔记】

【RISC-V开发笔记】

有问题的话,可以跟我讨论,知无不答,谢谢大家。

5 参考链接

- RISC-V 生态架构浅析

- RISC-V寄存器

- RISC-V指令

以上参考资料,由本人整理,但来源于网络,侵删!

审核编辑:汤梓红

-

RISC-V 和RT-Thread有什么区别2024-02-05 1621

-

RT-Thread开发者大会RISC-V分论坛动手实践指南2023-12-22 2631

-

【RT-Thread学习笔记】80x86汇编基础的三大块知识2022-07-30 3347

-

RT-Thread全球技术大会:RISC-V指令集开源软件生态介绍2022-05-27 1858

-

RT-Thread 内核学习笔记 - 理解defunct僵尸线程2022-01-25 953

-

RT-Thread Nano入门学习笔记2021-11-26 1403

-

沁恒(WCH)和RT-Thread达成合作,共建RISC-V应用生态2021-09-18 3725

-

火热报名中!RT-Thread X RISC-V创新应用大赛2021-09-14 3735

-

risc-v峰会亮点 RT-Thread对RISC-V的支持2021-06-23 8416

-

RT-Thread Studio(对芯来科技RISC-V处理器内核开发的全面支持2020-11-14 3261

全部0条评论

快来发表一下你的评论吧 !