泰克PCIe Gen 5 Tx一致性测试解决方案

电子说

描述

由于5G和IoT互联设备及相关高带宽要求预计将大幅度攀升,所以数据中心运营商需要迁移到带宽更高的网络,其中的带宽要超过当前通常使用的100GB以太网(100GE)。迁移到下一代400GE网络要求更快速的内存和更高速的串行总线通信。除了把以太网接口升级到400GE,服务器还需要采用速度更高的串行扩展总线接口和内存。

PCIe (PCI Express)扩展总线现在正迁移到最新标准化的PCIe 5.0,也称为PCIe Gen 5。与此同时,DDR(双倍数据速率)内存也正从DDR 4.0迁移到DDR≈5.0。PCIe Gen 5规范是PCI-SIG开发的PCIe 4.0标准的快速晋升增强版本。PCI-SIG是一家标准机构,规定了所有PCIe规范。随着PCIe 5.0插件机电(CEM)规范的最终确定,PCIe 5.0标准最近完成并于2021年6月发布,这是2019年发布的现有PCIe 5.0基本(硅)规范的姊妹篇。

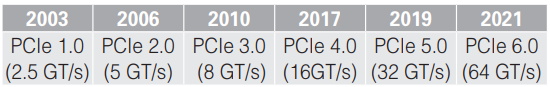

PCIe标准演进,传输速度翻番

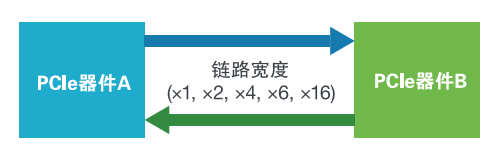

最初的并行PCI总线于1992年问世,旨在扩展个人电脑的功能,允许添加显卡和网卡及许多其他外设。PCIe是一种高速串行总线,旨在代替PCI及其他现有的传统接口,如PCI-X (PCI eXtended)和AGP(加速图形端口)。PCIe不仅吞吐量高,而且体积小,链路宽度可以在×1路、×2路、×4路、×8路、×16路间扩充。PCIe基于根复数(系统/主机)与端点(插件)之间的点到点总线拓扑,支持基于包的全双工通信。

PCIe双工链路通信

PCIe 1.0标准在2003年问世,提供了2.5G传送/秒(2.5GT/s)的速率。PCIe目前提供2.5GT/s~32GT/s的速率。PCIe 5.0把PCIe 4.0传送速率翻了一番,从16GT/s提高到32GT/s,但没有提供任何新增功能,因为当时的目标是在最短的时间内提供额外的速度。

目前发布的所有PCIe标准都采用非归零(NRZ)信令。但是,PCI-SIG目前正在开发PCIe Gen 6规范,将再次把传送速率翻一番,达到64GT/s,将从NRZ信令迁移出去。而Gen 6第六代规范将采用PAM-4信令,以及低时延FEC(前向纠错)技术来改善数据完整性。

所有PCIe标准都必须向下兼容,也就是说,PCIe 5.0 (32GT/s最大数据速率)还必须支持2.5GT/s、5GT/s、8GT/s、16GT/s及32GT/s。

PCIe规范时间线

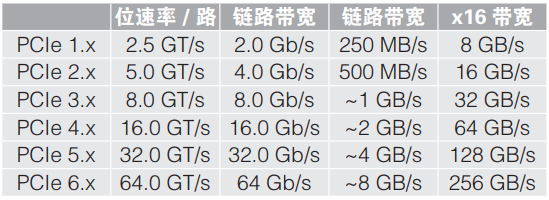

PCIe通路和链路速度

PCIe一致性测试,面临特定挑战

PCI-SIG是非专有PCI技术标准和相关规范的开发者,PCIe现在已经成为服务器事实上的标准。PCI-SIG规定了PCI规范,以支持要求的I/O功能,同时向下兼容以前的规范。为了能够在整个行业内采用PCI技术,PCI-SIG同时支持互操作能力和一致性测试,包括实现一致性必须执行及通过的测试。

PCI-SIG允许会员针对其他会员产品和测试套件进行互操作能力测试,参加测试的产品要么通过测试,要么未通过测试。为了通过正式的一致性测试,产品必须通过至少80%的互操作能力测试,并通过所有标准性的一致性测试。

PCIe 5.0面临特定的挑战。PCIe 4.0的最大数据速率是16GT/s,是PCIe上一代的速度加强规范,经验证实现起来要比以前的标准更难。在PCIe 5.0中,计算机PCIe通道和主板都面临着明显的挑战,因为要处理32GT/s数据速率。除了在较低数据速率遇到的挑战外,PCIe 5.0设备预计还会遇到明显的信号完整性挑战。泰克拥有针对所有数据速率(Tx、Rx和PLL带宽)的PCI-SIG批准的测试套件。

泰克PCIe Gen 5 Tx一致性测试解决方案

泰克是PCI-SIG的主要贡献者,为PCIe 4.0和5.0物理层测试规范做出了重大贡献,为确定PCIe 6.0 Tx/Rx测量方法做了大量探寻道路式的试验。泰克还在PCIe标准开发和实现过程中在一致性和互操作能力测试方面发挥了关键作用。

PCIe5.0发射机测试,适当的测试设备和自动化软件至关重要

在开发PCIe Gen 5发射机器件时,不管是在基本(芯片)级还是在CEM(系统和插件)级,都将要求芯片级验证(通常由PHYIP公司执行)和预一致性测试,然后才能把器件提交给PCI-SIG进行正式的一致性测试。因此,获得适当的测试设备及相关自动化软件至关重要。

PCIe一致性测试包括:

电气测试-评估平台、插件发射机(Tx)和接收机(Rx)特点

配置测试-评估PCIe器件中的配置空间

链路协议测试-评估器件的链路级协议特点

交易协议测试-评估器件的交易级协议特点

平台BIOS测试-评估BIOS识别和配置PCIe器件的能力

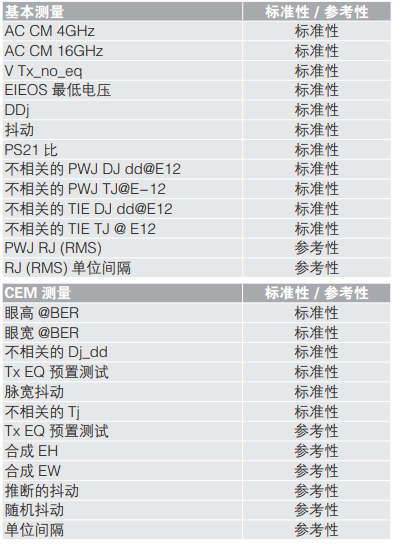

在电气测试方面,它分成两套测量,一套是基本级,一套是CEM级。这些测试又分为标准性测试和参考性测试:

PCIe基本和CEM一致性测量

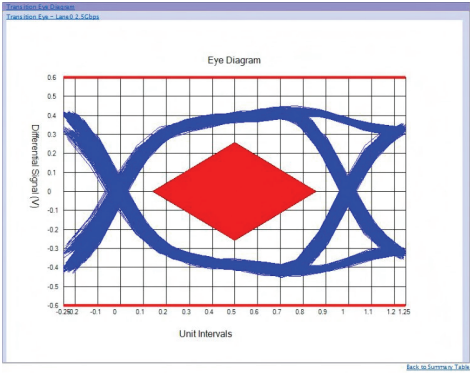

眼图

这两类测量都要求高带宽实时示波器,要能够捕获数据波形。然后采用后处理技术,进行基本规范和CEM规范中要求的相应的电压和定时测量。不相关抖动考查在去除包和通道码间干扰(ISI)后系统固有的抖动。除了抖动外,示波器还要进行眼高和眼宽测量。基本规范中规定了大量的“一致性测试码型”。推荐使用包含多次发生的整个一致性测试码型的波形记录,来构建代表性眼图。

在器件的基本Tx测试中,规范规定直接在发射机的引脚上进行测量。如果不能直接接入,那么测试点应尽可能靠近器件引脚。如果用户很好地了解S参数,那么通过物理复现通道或仿真,可以反嵌任何接续通道损耗。从4.0规范开始,描述了另一种反嵌技术,在波形后处理过程中,对不相关抖动测量应用CTLE(连续时间线性均衡),可以有效消除直到引脚的ISI。

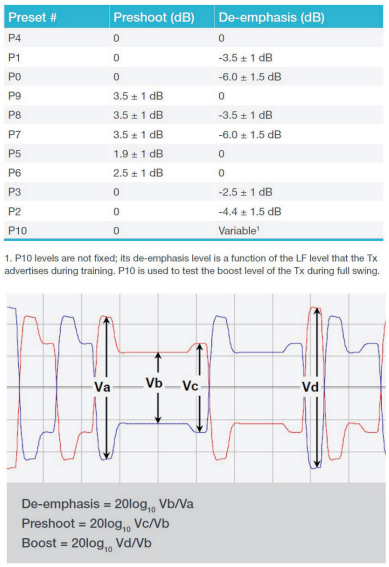

Tx均衡器预置

提交PCI-SIG认证的任何PCIe 5.0产品,都必须使用规定的Tx均衡器设置预置成功地通过一致性测试,支持速度从2.5GT/s直到32GT/s。这些预置用来均衡码流内部的频率相关衰减差引起的码间干扰,改善了信号完整性。每个预置都是下冲(光标前)和去加重(光标后)的特定组合。

目前有各种特定实现方案,让DUT发射机扫描通过各种数据速率和TxEQ预置。但是,基本规范规定了一种常用的方法,其中向接收机的通路0传送一个100MHz时钟突发。这可以采用任意函数发生器(AFG)自动实现。

对最大速率为32GT/s的PCIe链路,基本时钟(Refclks)存在着新的验证挑战。基本规范已经与数据速率成比例扩大抖动极限,但Gen 5不成比例地把极限下降到150fs。这种高频抖动测量要求正确应用公共时钟传送功能,并考虑最坏情况传送延迟。这一最新版规范还把测量从基本级规范(芯片级)推高到是CEM规范要求(外表级),必需满足一致性测试。

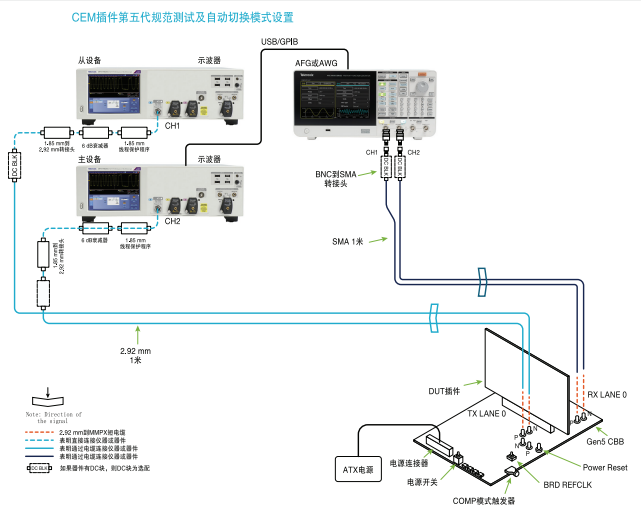

CEM插件PCIe 5.0一致性测试及自动预置切换

泰克PCIe解决方案,让一致性测试更有信心

示波器带宽和采样率要求。对基本Tx测试,每条PCIe 5.0通路以16GHz速率运行(因为两个比特可以在一个周期中发送),三阶谐波达到48GHz。由于在三阶谐波以上没有太有效的信号信息,所以PCIe 5.0基本Tx测试只需50GHz带宽的实时示波器。对CEM Tx测试,要在最坏情况通道的末端附近进行测量,减少了高频内容,要求33GHz的带宽。为确保充足的波形后处理(SigTest),要求每个单位间隔最少4个点,CEM允许最多2xsinx/x插补,所以最低采样率要达到128GS/s。

自动一致性测试。在一致性测试中,手动执行分析既耗时又容易出错。为节省时间,最好使用自动化软件,其不仅可以减少工作量,还可以加快一致性测试速度。对电气验证,PCI-SIG提供了SigTest离线分析软件,使用示波器采集的数据执行分析。自动化软件还控制被测器件(DUT),使用任意函数发生器作为码型源,让DUT自动通过一致性测试所需的各种速度、去加重和预置。

一轮完整的一致性测试要求在不同的DUT设置下每条通路采集多个波形。这个波形集合将按需要分析的通路数(最多16条)提高。软件要能够管理和存储分析及未来参考要求的数据,这对任何一致性测试解决方案来说都是一个重要指标。自动化软件还可以调节示波器水平和垂直设置及采集度。除了配置和分析外,还可以使用自动化软件管理采集的多个波形。

自动化软件可以选择数据速率、电压摆幅、预置和要执行的测试。它还可以提供选项,嵌入包参数模型,反嵌电缆、测试夹具或到达规范规定的目标测试点所需的其他元素。来自软件的分析结果通常可以汇编成PDF或HTML格式的报告,可以包括通过/未通过测试摘要、眼图、设置配置和用户备注。

通过使用泰克DPO70000SX系列示波器和AFG31252任意函数发生器,PCIExpressGen1/2/3/4/5解决方案可以在基本级(芯片)和CEM级(系统和插件)自动进行发射机验证和一致性测试。

TekExpressPCIe5.0Tx自动软件功能:

使DUT自主步进通过不同的速度、码型和Tx EQ预置

在进行测量前,在发射机上检验信号是否正确

执行通道和包嵌入和反嵌

支持SigTest和SigTest Phoenix各版软件和模板文件

使用Silicon Labs. “PCIe时钟抖动工具”和泰克DPOJET软件进行100MHz参考时钟抖动和信号完整性测量

在历史上,当新一代PCIe器件进入一致性测试时,很大一部分器件在进行PHY和链路训练一致性测试时,会在第一次互操作能力讲习会中通不过测试。在PCI-SIG讲习会前,确保完善的示波器、AFG、BERT(用于Rx测试)和自动化软件解决方案到位至关重要。泰克PCIe测试和调试Tx、Refclk和Rx解决方案可以在互操作能力测试前引导您完成一致性测试和调试,确保您的设计满怀信心地满足PCI-SIG PCIe标准要求。

审核编辑:汤梓红

-

串行ATA一致性测试速查资料2008-11-26 4429

-

泰克推出SFF 8431 SFP+自动一致性测试和调试解决方案2011-12-24 4368

-

电源测量小贴士(八):电源线一致性测试2016-09-06 4458

-

MIPI一致性测试2019-09-26 3638

-

PCIe 2.0/PCIe 3.0验证、调试和一致性测试解决2010-06-29 1262

-

泰克为SAS一致性测试推出全自动测试支持2010-02-21 1571

-

泰克推出DisplayPort一致性测试的全自动化解决方案2011-11-17 1368

-

泰克演示最新的HDMI 1.4a一致性测试解决方案2012-03-27 1350

-

RFID协议一致性测试系统设计(三)2012-03-28 1674

-

泰克公司推出全自动Thunderbolt发射端一致性测试解决方案2012-07-03 1530

-

泰克推出业界最完整、最灵活的自动PCI Express 3.0 Tx、Rx测试套件2012-11-07 2150

-

泰克公司推出针对MHL 2.1的先进分析与一致性测试解决方案2013-07-17 1869

-

泰克公司推出首个针对QSFP+产品的一致性测试和调试解决方案2013-07-25 1651

-

泰克推出HDMI 2.0自动一致性测试与调试解决方案2014-02-11 1733

-

泰克推出HDMI 2.0一致性测试及调试解决方案2014-06-18 2060

全部0条评论

快来发表一下你的评论吧 !