基于蜂鸟E203 RISC-V处理器内核的SoC设计

FPGA/ASIC技术

描述

杯赛题目:基于蜂鸟E203 RISC-V处理器内核的SoC设计

参赛要求:研究生组/本科生组

赛题内容:

基于芯来科技的开源蜂鸟E203 Demo SoC进行扩展,在限定的可编程逻辑平台上构建面向专用应用领域(譬如人工智能、信息安全、工业控制等)的SoC,进而完成一定实际应用。要求在所搭建的SoC中实现专门的硬件加速器以提高系统整体性能,所实现的系统具有创新性、实用性以及市场应用前景。

团队介绍

参赛单位:电子科技大学

队伍名称:第N队

指导老师:路志刚

参赛队员:朱俊宛、罗扬、岳修立

总决赛奖项:三等奖

1. 项目简介

随着信息化和数字化社会的发展,人们对信息安全和保密的重要性认识不断提高,信息加密算法也在不断的发展进步之中。SM4密码算法是国家密码管理局正式的《祖冲之序列密码算法》等6项密码行业标准之一。本项目基于开源E203处理器在FPGA开发板上对国产密码算法SM4算法进行实现和优化,并实现了对字符串的加密与解密。

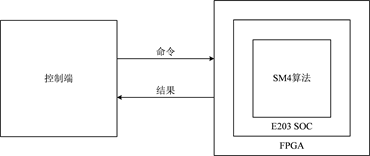

1.1 系统框架

系统控制端通过串口通信FPGA开发板发送命令:操作类型(加密解密)、操作数据(明文密文)、密钥。FPGA上的E203 SoC接收来自控制端的命令并运行硬件加速后的SM4算法程序进行处理,处理后的结果通过串口通信返回给控制端,如下图所示。

1.2 SM4算法原理

1.2.1 概述

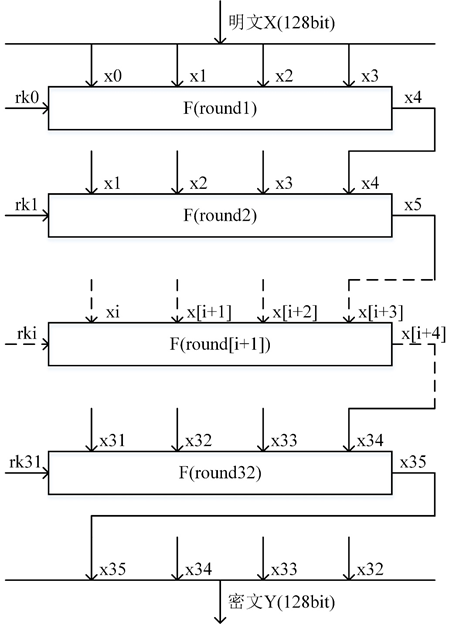

SM4算法是一种分组密码算法。其分组长度为128bit,密钥长度也为128bit。加密算法与密钥扩展算法均采用32轮非线性迭代结构,以字(32位)为单位进行加密运算,每一次迭代运算均为一轮变换函数F。SM4算法加/解密算法的结构相同,只是使用轮密钥相反,其中解密轮密钥是加密轮密钥的逆序。

SM4算法的整体结构如图:

1.2.2 轮函数

整体的加密函数F为:

x(i+4)=F(x(i),x(i+1),x(i+2),x(i+3),rk(i))=x(i)⨁T(x(i+1)⨁x(i+1)⨁x(i+2)⨁x(i+3)⨁rk(i))

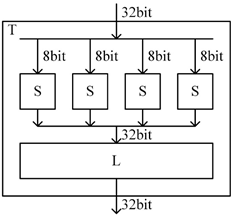

其中T为一个合成置换,由非线性变换S和线性变换L复合而成,如下图。

非线性变换S由具有256个固定的8bit数据的S盒构成,S盒的数据均采用16进制。输入的8bit数据作为S盒中地址的索引,地址中所包含的8bit数据即为S盒的输出。非线性变换S函数表达式可以表示为:

B=(b1,b2,b3,b4)=S(A)=(sbox(a1),sbox(a2),sbox(a2),sbox(a2))

线性变换L的公式如下:

C=L(B)=B⨁(B≪2)⨁(B≪10)⨁(B≪18)⨁(B≪24)

其中B为非线性变换得到的字。

1.2.3 轮密钥

已知加密密钥:MK=(MK0,MK1,MK2,MK3),系统参数:FK=(FK0,FK1,FK2,FK3) ,固定参数:CK=(CK0,CK1,⋯⋯,CK31) 。

轮密钥rki即为密钥扩展的结果,由加密密钥扩展生成,过程如下:

首先:

(K(0),K(1),K(2),K(3))=(MK0⨁FK0,MK1⨁FK1,MK2⨁FK2,MK3⨁FK3)

然后对于i=0,1,⋯⋯,31:

rk(i)=K(i+4)=K(i)⨁T'(K(i+1)⨁K(i+1)⨁K(i+2)⨁K(i+3)⨁CK(i))

其中变换T'与轮函数的T变换基本相同,只是将其中的线性变换L改为:

L'(B)=B⨁(B≪13)⨁(B≪23)

1.3 协处理器加速设计

1.3.1 软硬件功能划分

硬件功能:利用协处理器实现SM4算法中的密钥拓展过程与加解密过程。

软件功能:调用协处理器实现密钥拓展过程与加解密过程,并对过程进行控制。

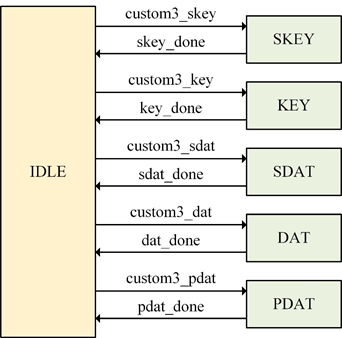

1.3.2 状态转换

根据SM4算法原理及软硬件功能划分,六个状态,分别为初始状态(IDLE)、密钥加载状态(SKEY)、密钥拓展状态(KEY)、输入加载状态(SDAT)、加解密运算状态(DAT)、输出返回状态(PDAT)。

当有相应的指令标识位置1时,状态机将从初始状态进入相应的指令状态。当相应的状态完成标识位置1后,状态机将从相应的指令执行状态进入初始状态。状态转换单元示意图如下。

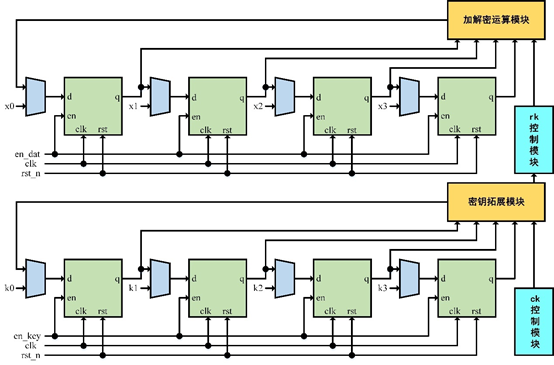

1.3.3 数据运算

数据运算部分主要是在根据协处理器当前的状态进行相应的运算操作以实现SM4算法。数据运算单元示意图如下。

1. 当处于密钥加载状态(SKEY)时,协处理器会将CPU送过来的与系统参数FK异或过的初始密钥k0、k1、k2、k3加载到下方4个寄存器中。

2. 当处于密钥拓展状态(KEY)时,k0、k1、k2、k3会进行32轮非线性迭代运算,在迭代过程中生成k4-k35,即轮密钥rk0-rk31,并存储到rk控制模块之中。

3. 当处于输入加载状态(SDAT)时,协处理器会将CPU送过来的初始输入x0、x1、x2、x3加载到上方4个寄存器中。

4. 当处于加解密运算状态(DAT)时,x0、x1、x2、x3会进行32轮非线性迭代运算,会根据此时源操作数1的值决定轮密钥rki的使用顺序,为0对应于加密操作,为1对应于解密操作。迭代过程完成后将得到x31、x32、x33、x34,即运算结果。

5. 当处于输出返回状态(PDAT)时,协处理器会通过结果反馈通道nice_rsp_rdat将运算结果返回给CPU。

2. 仿真与测试

2.1 功能仿真

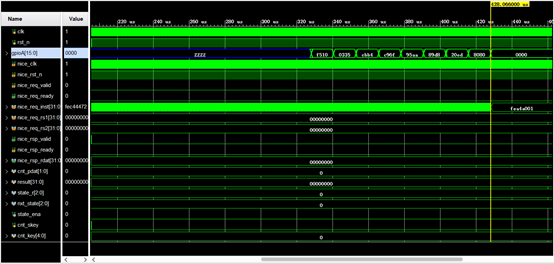

2.1.1 SM4算法纯软件实现功能仿真

vivado仿真波形:

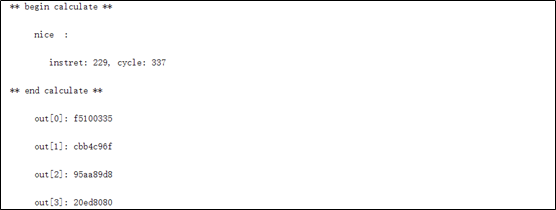

Tcl控制台结果:

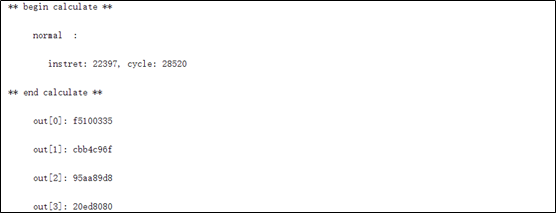

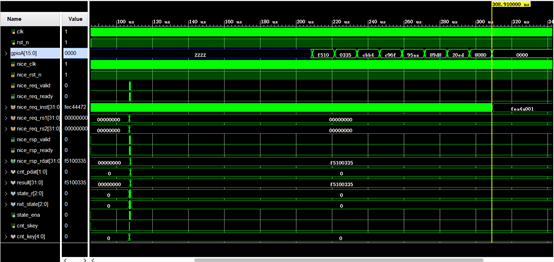

2.1.2 SM4算法协处理器加速实现功能仿真

vivado仿真波形:

Tcl控制台结果:

2.1.3 协处理器加速效果

对比两次仿真结果得到,协处理器对SM4算法的加速效果为:28520 / 337 = 84.6(倍)

2.2 整体测试

整体测试的实物连接如图

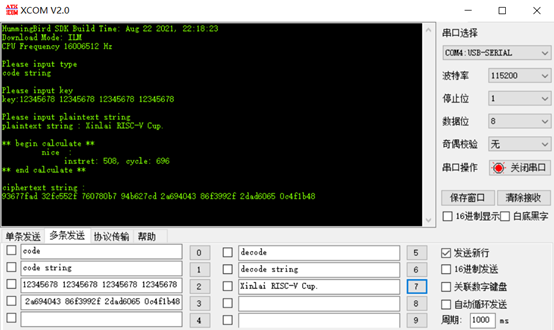

2.2.1 字符串加密

对字符串“Xinlai RISC-V Cup”进行加密,密钥为:0x1234578 1234578 1234578 1234578。结果如图。

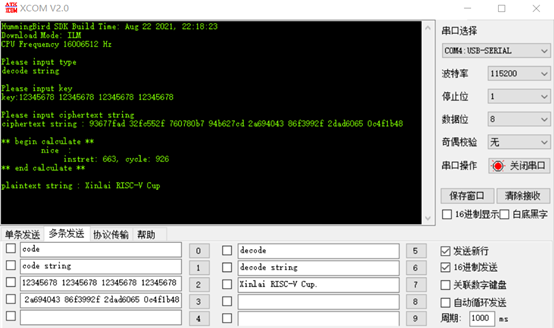

2.2.2 字符串解密

将加密得到的密文 0x93677fad 32fc552f 760780b7 94b627cd 2a694043 86f3992f 2dad6065 0c4f1b48 进行解密操作,结果如图。得到解密结果为:“Xinlai RISC-V Cup”。验证了加密结果的正确性,完成了对字符串的加密解密,实现系统的预设功能。

3. 参赛体会

3.1 参赛感受

在三个多月的学习与实践之中,经过VERLIOG的学习、VIVADO的使用、FPGA开发板的学习、RISK_V的学习、E203 SoC的移植、SM4算法的学习、协处理器的学习与应用等过程,基本完成了基于E203 处理器内核的SM4算法硬件加速。从一个刚开始学习的小白,一步步摸索前进。在不断遇到问题,解决问题的过程中,加深了对集成电路行业的理解,提升我们的软件设计能力。

集创赛作为全国性的顶尖赛事,汇集了来自全国各地各高校的优秀大学生。让我们在比赛过程中能够与如此多优秀的同龄人同台竞技,相互交流,极大拓展了自己的视野与能力。非常感谢集创赛赛事组委会的工作人员和老师们的组织与付出,让我们有机会参与到这样一个充分展示风采的平台。

3.2 后续计划

1.加入其他算法(例如SM3算法)进行交互,进一步提升其加密效果。

2.对输入,输出及控制系统进行进一步的优化与拓展,使用上位机来传输数据流和控制。

审核编辑 :李倩

-

开源RISC-V处理器(蜂鸟E203)学习(一)修改仿真环境(vcs2018+verdi2018)2025-10-31 285

-

利用蜂鸟E203搭建SoC【1】——AXI总线的配置与板级验证2025-10-30 274

-

RISC-V 蜂鸟E203平台搭建2025-10-28 274

-

在Ubuntu 虚拟机中使用verilator对蜂鸟E203内核进行仿真2025-10-27 333

-

如何对蜂鸟e203内核乘除法器进行优化2025-10-24 263

-

蜂鸟E203内核优化方法2025-10-21 249

-

利用vcs+verdi仿真工具蜂鸟E200系列处理器仿真分析2022-11-17 4434

-

简化E203处理器的结构设计2022-09-27 1881

-

开源Hummingbirdv2 E203 RISC-V处理器内核和SoC项目2022-03-17 1597

-

RISC-V嵌入式开发的特点有哪些2021-11-08 2367

全部0条评论

快来发表一下你的评论吧 !