I2C总线如何在IC之间提供有效的串行链路

接口/总线/驱动

描述

若在印刷电路板(PC 板)上使用并行总线来实现集成电路间的通信和控制,这样做不太符合实际。即便是 8 位处理器,仅数据方面就要使用 16 条线,而地址总线需要的线数还要更多。如果一条共享的通信总线上需要使用多个 IC,那就更成问题了。这是因为空间不够用,无法满足所有这些 PC 板走线。解决办法是使用内部集成电路 (I2C) 总线等串行通信总线来链接 IC。这种双线串行总线可用于解决该问题。

本文将介绍 I2C 总线的起源,及其如何在 IC 之间提供有效的串行链路。然后,本文将讨论 I2C 总线的物理实现方式、协议结构,以及这种无处不在的通信总线的常见应用。其中将使用 Microchip Technology 的 I2C 接口和解决方案示例进行演示。此外,本文还将讨论 I2C 与系统管理总线 (SMBus) 的异同。

什么是 I2C 总线?

在 1980 年代早期,I2C 总线由 Phillips Semiconductors(现为 NXP Semiconductors)开发。这是一种简单的双向双线总线,可在一块共用 PC 板上实现集成电路的有效通信和控制。最早的总线规格于 1992 年完成,随后即成为行业公认标准,并且 50 多家 IC 制造商的元器件中都提供该标准。这种大规模的部署允许采用一种系统方法进行设计,可以轻松地将 IC 纳入 I2C 总线结构中,而无需进行定制设计。其他几种专用总线(例如 SMBus 和电源管理总线 (PMBus))以及另外一些总线均采用该基本架构。

I2C 总线是一种可寻址总线,因此可以链接多个 IC 和传感器;7 位或 10 位地址字段允许主控器件向选定器件发送消息。最初,I2C 的最大时钟速度为 100 千赫兹 (kHz),但是经过多年的发展,更高速的工作模式已将这一限制推高至 3.4 兆赫兹 (MHz)。

I2C 总线使用两条线,即指定为串行数据线路 (SDA) 和串行时钟线路 (SCL)。SDA 和 SCL 是开漏/集电极双向线路,并通过电流源或上拉电阻连接到正电源总线。该总线可以连接多个器件,最大数量受总线电容限制。主控器件控制着总线,总线上的每个器件都有唯一的地址。主控器件可以通过总线收发数据(图 1)。I2C 支持多主控操作,其冲突检测和仲裁功能可防止两个或更多主控器件同时启动数据传输。不过,本文将重点介绍单主控配置。

图 1:Microchip Technology 的演示印刷电路板原理图,该电路板实现了 I2C 总线并连接到五个不同的器件。主控器件位于板外,通过连接器 P1 连接。SCL 和 SDA 线路用绿色框出,两个上拉电阻器用蓝色圈出。(图片来源:Microchip Technology)

图 1 显示了 Microchip Technology 的 PKSERIAL-I2C1 I2C 演示板原理图。该演示板使用五种不同的器件来实现 I2C 总线,包括 EEPROM、温度传感器、12 位模数转换器 (ADC)、10 位数模转换器 (DAC) 和 8 位串行转并行转换器。主控器件不在板上,而是通过连接器 P1 连接。SDA 和 SCL 总线线路以绿色框出,上拉电阻器以蓝色圈出。

SDA 和 SCL 电平一般为正电源电压的固定百分比,通常表示为 VDD。对于逻辑“1”(高)和逻辑“0”(低),参考电平分别设置为 VDD 的 70% 和 30%。

时钟信号以猝发模式出现,每个传输的数据位使用一个时钟。时钟处于高电平时,SDA 线路上的数据必须有效。只有在时钟处于低电平时,才能更改数据。

从设计人员的角度来看,由于 I2C 接口已集成到 IC 中而无需设计接口,因此新项目得以简化。每个器件只需直接连接到总线。在总线上可以添加或移除 IC,而不会影响其他电路(假设 IC 的总数不会超越电容极限)。简单的双线总线可最大程度地减少每个 IC 上的引脚数和印刷电路板上的走线数。

I2C 协议

该总线为 8 位导向协议,以字节为单位进行通信。如上所述,在现在所谓的标准模式中,最初的最大时钟速率为 100 kHz。如今,总线在快速模式下支持 400 千比特/秒 (Kb/s),在快速增强模式下支持高达 1 兆比特/秒 (Mb/s),在高速模式 (Hs-Mode) 下支持高达 3.4 Mb/s。

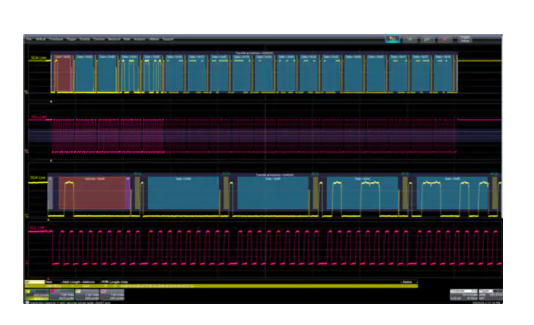

通过图示总线上的典型传输,可以很好地说明 I2C 协议(图 2)。屏幕图像的来源是 Teledyne LeCroy 的示波器,其包含低速串行数据触发器和解码选件 WS4KHD-EMB TD。该示波器选件可以触发和解码多达 19 个低速串行数据接口,其中就包括 I2C。

图 2:典型的 I2C 数据包含有一个起始位、地址字段、应答位、17 个各自拥有 ACK 位的数据字节和最后的一个停止位。每个字段均由带色码的叠加层标识。上方(黄色)迹线是整个 SDA 数据包,下方是 SCL 时钟(红色)。第三和第四迹线是两个信号的水平扩展视图。(图片来源:Digi-Key Electronics)

该示波器可以在特定的串行事件触发,包括起始、停止、丢失应答 (ACK)、地址、数据、地址加数据、帧长和 EEPROM 数据传输。串行数据标准的协议组件由带色码的叠加层标识。每个协议字段都以二进制、十六进制或 ASCII 解码,并且所选代码显示在叠加层内。

SDA 信号显示为黄色迹线,而 SCL 信号显示为红色迹线。灰色的叠加框指示起始和停止功能。砖红色叠加层标记地址数据,蓝色字段为数据包数据,橄榄色叠加框标记 ACK 功能。

顶部迹线显示了从起始到停止的整个 I2C SDA 数据包。紧靠下方是相应的 SCL 信号。再向下第三条迹线是 SDA 信号的时间扩展缩放迹线,其下方是同步 SCL 信号。

在数据传输之间总线空闲时,SDA 和 SCL 线均处于高电平状态。SCL 信号包括以时钟速率发出的九个猝发脉冲,每个传输的数据位使用一个,还有一个用于 ACK 位。

所有总线事务都由一个主控器件生成的起始位开始,该位在缩放的 SDA 轨迹中显示为灰色叠加框。主控器件在 SCL 线处于高电平状态时将 SDA 线拉低,即表示起始信号。一旦主控器件发出起始位后,总线就即视为处于繁忙状态。主控器件可以发出多次起始信号,这种情况下的后续起始信号通常称为重新起始。

所有数据传输的长度均为 8 位(一个字节),每个后跟一个 ACK 位。位传输顺序是先传输最高有效位 (MSB)。每个字节传输必须得到应答。如果从器件处于繁忙状态,而无法接收或发送数据,则可以将 SCL 线拉低。这将迫使主空器件进入等待状态,直到从器件释放 SCL 线。

当发送器件在第九个应答时钟脉冲之前释放 SDA 线后,即会形成 ACK 位。如果接收器件已接收到数据字节,则会将 SDA 线拉低。在图 2 的 SDA 放大视图中,紧靠第九个时钟脉冲之前有一个窄峰,这表示 SDA 线经释放返回到高电平状态。接收器件拉低 SDA 线以产生 ACK 信号,该信号由橄榄色叠加框作为符号标记。如果接收器件未在第九个时钟脉冲之前将 SDA 线拉低,则是一个非应答 (NACK) 响应。如果发生 NACK,则主控器件可以生成停止信号并中止传输,也可以发出重复起始信号以重试。

在起始条件之后,即会发出从器件地址。这由砖红色叠加框表示。地址格式可能有两种:7 位或 10 位,其中最常见的是 7 位地址。起始后的前 7 位代表地址数据。第 8 位指示数据方向:读或写。SDA 线处于低电平表示写入,而此时 SDA 线处于高电平,表示读取操作。10 位寻址使用起始条件后的前两个字节。I2C 为内部功能保留了多个地址。解码地址数据以二进制、十六进制或 ASCII 格式显示在地址叠加框中。

蓝色的叠加字段标记数据传输。每个为八位长,后跟一个 ACK/NACK 响应。I2C 数据包中的数据字节数不受限制,但是图 2 包含 17 个字节。解码后的数据(例如地址解码)显示在数据叠加框中。数据流之后是在数据传输结束时主控器件生成的一个停止位,由顶部数据迹线中的灰色叠加框表示。当 SCL 线处于高电平状态时,该停止位是 SDA 线从低到高的跳变。在发出停止信号后,总线再次空闲。

显示屏底部的表格汇总了有关数据包的所有信息,包括自触发以来的时间、地址长度、地址,读或写操作、数据包长度,以及数据内容的摘要。该表中的条目数与示波器获取的 I2C 数据包数相匹配,后者在本例中仅为一行。

如果发生协议错误,则由协议叠加框后面的亮红色框表示。

I2C 器件

I2C 总线的最大优势之一是,有大量的器件已将该总线纳入自己的设计中。Microchip Technologies 演示板提供了一些 IC 类型的示例,这些 IC 包含 I2C 总线或其衍生品之一,如 SMBus。

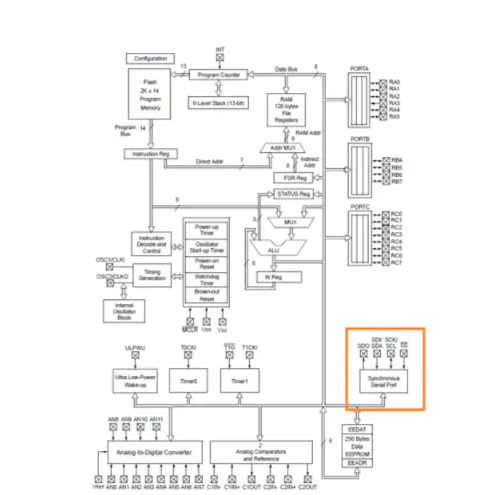

Microchip Technology 的 PIC16F677 是一款 8 位微控制器,其在许多嵌入式设计中均有采用。该产品实施了一个同步串口,经过适当控制后,可通过串行外设接口 (SPI) 或 I2C 与其他控制器或外设进行通信(图 3)。

图 3:Microchip Technology 的 PIC16F677 是一款 8 位微控制器,其包含一个同步串口(橙色框出),可编程为 SPI 或 I2C 总线。(图片来源:Microchip Technology)

这款微控制器支持使用 7 位或 10 位寻址的 I2C 主模式和从模式。该器件将 SCK/SCL 引脚用于 I2C SCL 时钟信号,将 SDI/SDA 引脚用于数据信号。

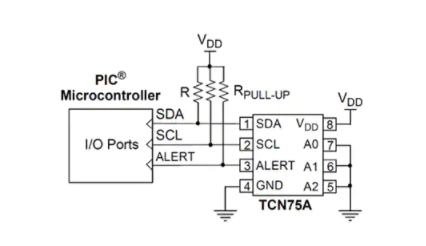

这两个引脚连接到 I2C 总线上的 SCL 和 SDA 线,以实现与其他器件的通信。常见的连接是连接至基于 I2C 的传感器,例如 Microchip Technology 的 TCN75AVOA713 双线串行温度传感器(图 4)。

图 4:Microchip Technology 的 TCN75A 温度传感器直接连接至 PIC16F677 微控制器以传输温度数据。(图片来源:Microchip Technology)

此温度传感器能够进行串行通信,因此功能方面得以增强。内置的用户可编程寄存器可用于设置温度测量分辨率、节能关机模式,甚至可设置警报输出,以在温度范围超出预设限值时发出提醒。

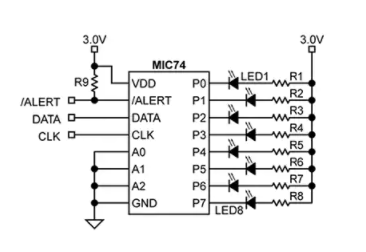

此外,还有许多器件可以解码 I2C 串行数据流并将其分解为并行数据。这里介绍一下 Microchip Technology 的 MIC74YQS-TR 双线 I/O 扩展器和风扇控制器(图 5)。

图 5:Microchip Technology 的 MIC74YQS-TR I/O 扩展器将串行数据流转换至八根独立的并行 I/O 线。(图片来源:Microchip Technology)

该 IC 是完全可编程的 I/O 扩展器,提供八根独立的 I/O 线。这些 I/O 线可以单独编程为输入或输出。图 5 显示了 MIC74YQS-TR 在串行总线的控制下驱动八个 LED。这与图 1 中 I2C 演示板上 MCO23008 的用法相似。MIC74YQS-TR 与电源稳压器结合使用,也可以使用其四个最高有效位来实现风扇电机的速度控制。

SMBus 和 I2C

I/O 扩展器的串行输入是专为 SMBus 设计,但也与 I2C 总线兼容。SMBus 规格基于 I2C,由 Intel 和 Duracell 于 1994 年定义。主要区别在于标准模式 I2C 逻辑电平相对于 VDD 变化,而 SMBus 的逻辑电平则是固定不变。在大多数情况下,当 VDD 介于 3 伏和 5 伏之间时,经验表明这不是问题。

另一个区别是 SMBus 的时钟速率限制为 100 kHz 或更低,而 I2C 有几种模式支持更高的时钟速率。当涉及总线兼容性时,这会将最大时钟速率限制为 100 kHz 或 I2C 标准时钟模式。

因此,除了非常特殊的情况外,SMBus 和 I2C 都是兼容的。

总结

I2C 总线及其衍生品广泛应用于各种类型的数百种 IC,从而使它们在多层面设计和应用中易于连接。混合信号和模拟传感器经过耦合后,即可扩展基于微控制器的嵌入式系统范围。所有这些都通过一个简单的双线串行数字接口实现。

-

I2C总线通信原理 如何设计I2C总线电路2025-01-31 1967

-

I2C总线信号与测试案例(一)2023-11-20 3705

-

I2C串行总线组成及工作原理2023-11-16 519

-

I2C总线原理详解2023-10-18 3900

-

I2C串行总线协议是什么?I2C总线有哪些优点?2023-09-12 2847

-

I2C串行总线的组成及工作原理的详细资料说明2019-07-31 1443

-

互联IC总线(I2C2017-10-11 1082

-

互联IC总线(I2C)2016-01-13 921

-

基于CPLD的I2C总线接口设计2011-02-12 1261

-

基于I2C总线的EEPROM驱动程序2010-12-07 694

-

I2C总线详解2010-06-30 4135

-

I2C总线2009-11-03 690

-

I2C总线的工作原理与应用2009-03-02 5194

-

i2c总线介绍2008-08-13 1127

全部0条评论

快来发表一下你的评论吧 !