模拟设计的笔试面试题目

描述

据说今年的秋招已经开始了,作者君自己之前找工作的时候,记录下来了一些比较基本的笔试面试题目,分享给大家,希望能帮大家巩固所学的基本知识。

(因为懒,不想visio画图,请大家忍耐一下有些潦草的字迹,谢谢啦)

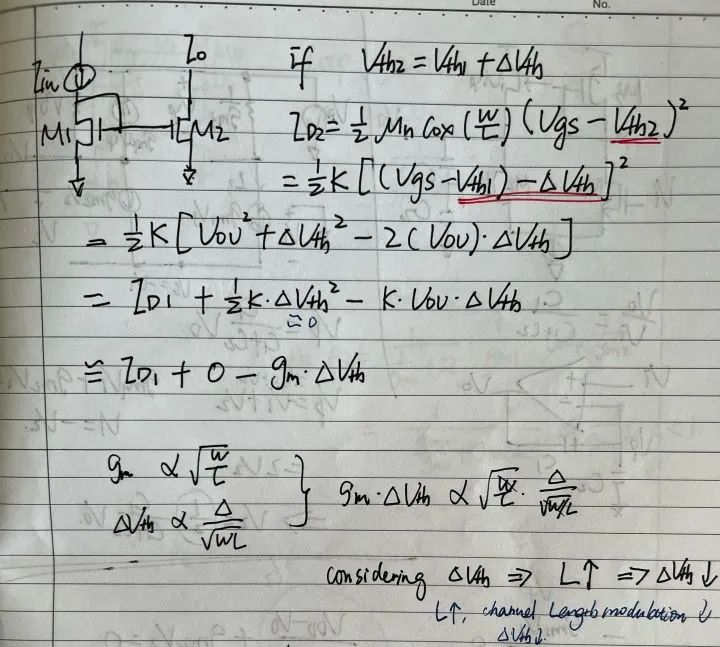

电流镜的设计考量

这道题主要是考察电流镜的设计考量。

假如图中的两个管子M1和M2之间有mismatch,比如Vth有偏差(偏差是一定有的,特别是当L的取值比较小的时候,越是明显),如果先忽略掉Vds的影响,需要重视什么变量呢?

按照上面的计算,Id1和Id2之间的差别约等于gm×ΔVth . 又因为gm 与宽长比的平方根正相关,而ΔVth 的公式里面,长宽的乘积的平方根是在分母位置,分子的Δ 是一个跟工艺参数有关的量(我们动不了),所以两者相乘起来,gm×ΔVth 的值和Δ/L 正相关。

因此,如果想要减少电流镜的offset,我们特别需要注意的地方就是两个管子的L的取值。一般情况下,L取的比较大有利于减小offset。(当然了,电流一定的情况下,L要变大,W自然也要跟着变大,两者都变大了,有关的寄生电容也会变大……又是一个tradeoff的闭环-_-)

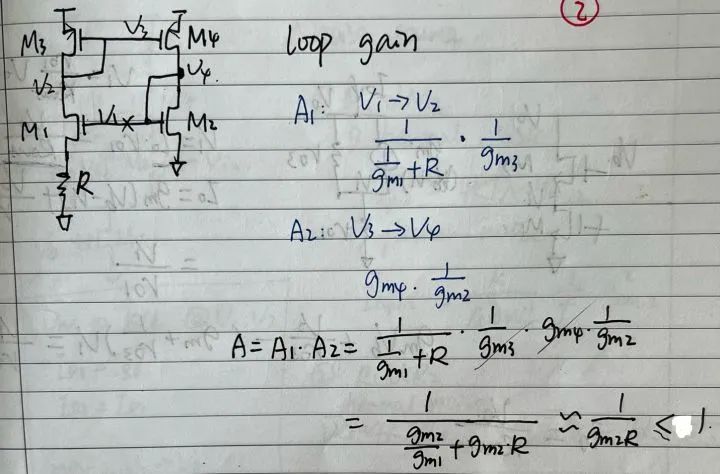

电流产生电路

这道题的考察其实类似bandgap了,问的就是下面那个R到底是应该在M1的下面,还是M2的下面。

如果在M1的gate和M2的gate之间断开,从V1开始看,经过M1,M3,到M4,M2,可以看出来,这个loop是个正反馈环路。(不知道大家还记不记得我之前提过的很个人的习惯:gate到drain是-,gate到source是+)

对于一个不想让它震荡起来的正反馈环路(请回忆一下巴特豪森定律),环路增益必须要小于1.

上面的图里,我计算了从V1到V2,V2=V3,V3到V4的增益。总的环路增益就是A1乘以A2,约等于 1/(gm2R) .如果R不是很小,这个A一般来说是小于1的。

PS:如果是典型的constant gm电路,可以让M1的W是M2的四倍,然后R约等于1/gm2 ,然后最后生成的电流大致上等于Vov/R. 比较典型的Vov等于两三百mV,选择合适的R,就能得到需要的电流。(Razavi的书里figure11.3,如果考虑body effect,Razavi建议把R放在PMOS上面)

大家可以试一下把R放在M2的source下面,可以算出来A大概是gm1⋅(1/gm2+R) .这个乘积一般是大于1的。

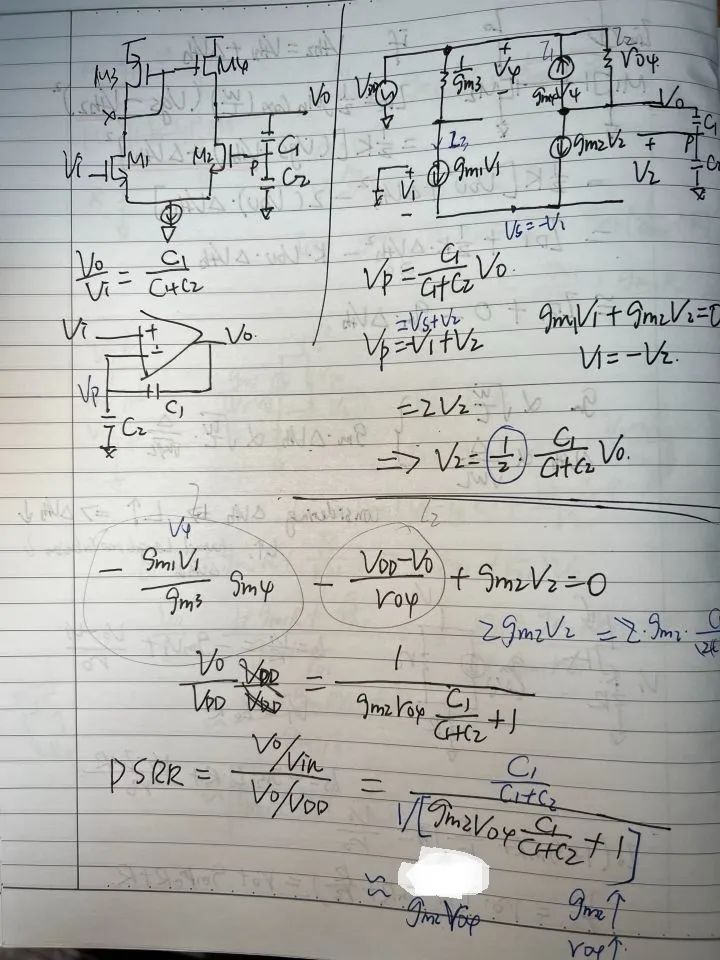

五管运放的PSRR计算

一个挂着C1和C2两个load的五管运放,计算它的PSRR.

首先画小信号模型,右上角那一块。

然后是Vo那里的KCL,得到Vo和VDD之间的关系。已知Vo和Vin的比值是电容分压,因此可以得到最后的PSRR值是跟gm2ro4 的乘积成正比。所以为了增大PSRR,就可以从这两个变量下手,增大gm2 (比如增大宽长比,增大偏置电流),增大ro4 (比如M3和M4的L增大),都可以达到目的。

这次的分享就是这三道题。还有一些就留着下次再说吧!读者们如果也有不错的题目分享,请留言!谢谢!

审核编辑:汤梓红

-

硬件工程师面试试题——IC设计基础篇2012-02-24 6006

-

FPGA笔试面试题目2012-08-07 9199

-

电子工程师_嵌入式工程师_单片机_笔试题目_面试题目2012-08-09 16354

-

java经典面试题深度解析2017-06-20 2640

-

视频教程:Java常见面试题目深度解析!2017-07-11 4072

-

C语言 经典面试题目2017-08-05 6031

-

FPGA历届面试题解答视频解答2019-05-07 2176

-

NLP的面试题目2020-05-21 2489

-

嵌入式软件工程师笔试面试的相关资料分享2021-12-24 3757

-

硬件工程师面试题目集合2011-07-11 3545

-

清华大学电机系面试题整理2016-02-25 1317

-

C语言经典面试题目2017-01-05 1034

-

广西电网招聘面试题目讲解2017-12-19 915

-

关于数组常见的面试题2022-08-17 2888

-

常见的嵌入式C语言面试题2023-07-18 1346

全部0条评论

快来发表一下你的评论吧 !