管脚约束问题导致生成bit时报错 如何在不重新Implentation情况下生成bit?

电子说

描述

在FPGA开发中,我们经常遇到因为管脚忘记约束,导致最后生成bit的时候报错。

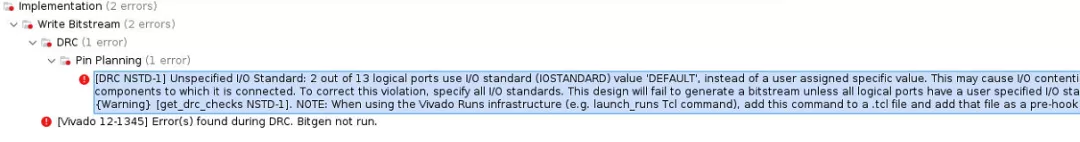

1.管脚电平未约束

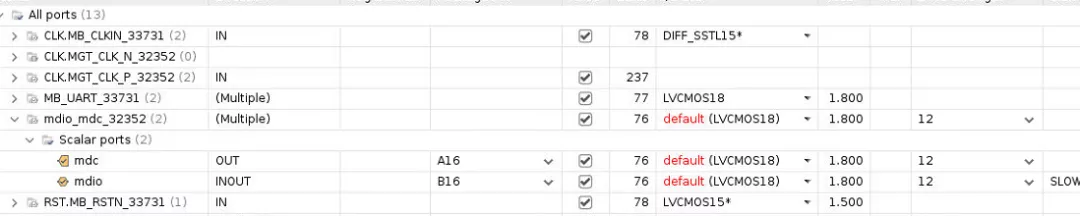

像上面这个图中,由于在约束中忘记指定mdc和mdio的电平,再经过了长时间的综合和实现后,最后的Generate Bitstream报错了。

这种情况下,如何才能不重新Implementation的情况下生成bit呢?

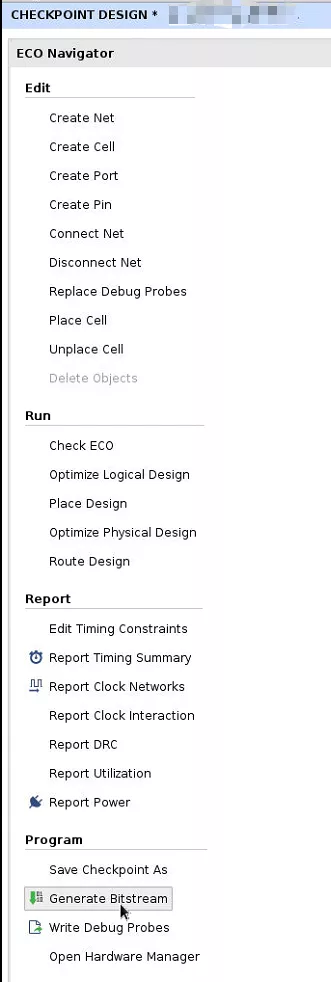

打开实现后的routed.dcp文件:

open_checkpoint ./Work/eth_demo.runs/impl_1/top_routed.dcp

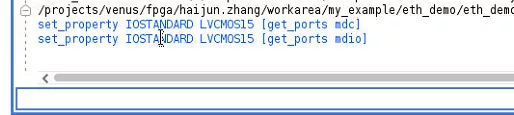

然后通过下面指令设置这两个管脚的电平:

set_property IOSTANDARD LVCMOS15 [get_ports mdc] set_property IOSTANDARD LVCMOS15 [get_ports mdio]

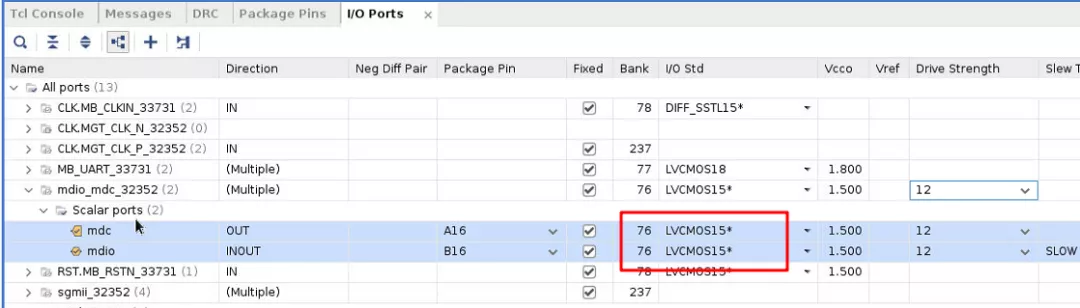

设置完成后,可以在I/O Ports窗口中看到这两个管脚的电平已经改了过来

然后再点左侧的生成bit:

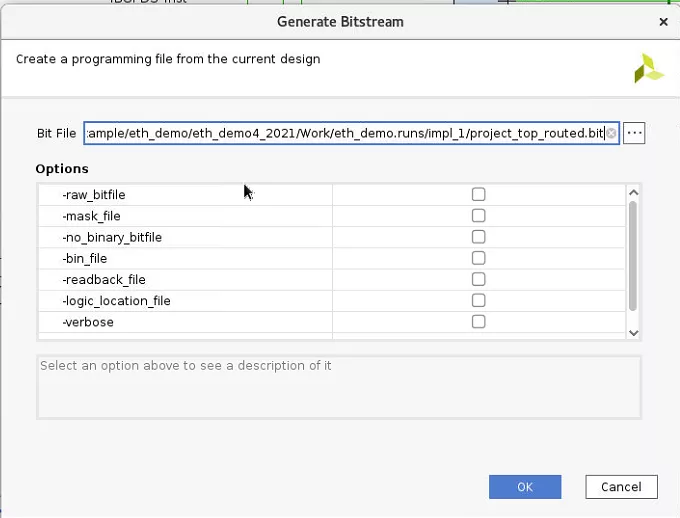

提示生成文件的位置和名字:

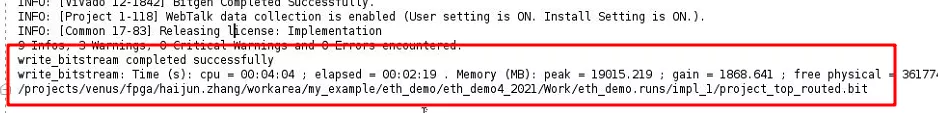

在正确生成后,可以看到tcl中提示write_bitstream completed successfully:

管脚电平修改后由于跟布局布线都没有关系,因此直接生成bit是可以的。

2.管脚位置未约束

如果是管脚位置未约束,那我们就不能在dcp中修改位置然后直接生成bit了,因为位置变了,布局布线也需要改变。如果这个管脚的功能的需要的,那我们只能重新Implementation,如果这个管脚功能是不需要的,

那如果这个管脚的功能我们可以先不用,就想把经过了长时间的Synthsis和Implentation后的工程生成bit文件。

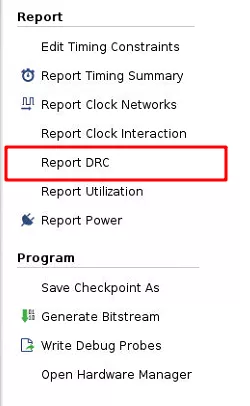

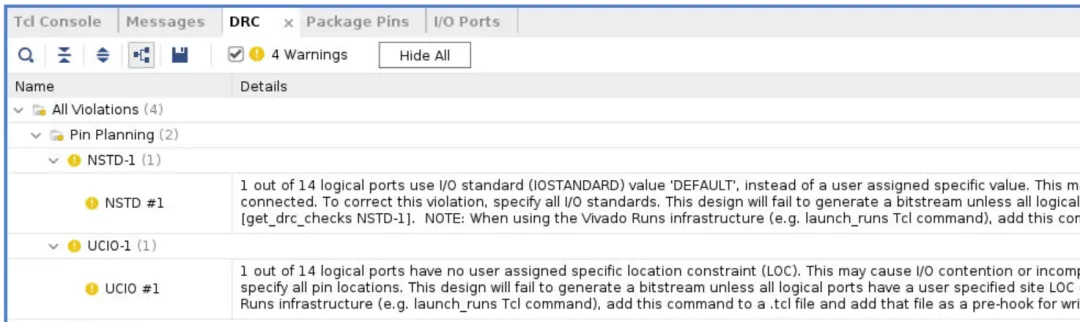

还是像上面一样,打开route.dcp文件,然后点击坐标的Report DRC

可以看到有两个问题,一个是NSTD-1,一个是UCIO-1

我们只需要把这两个DRC的问题设成warning,不让工具在生成bit的时候报错,也是可以生成bit的。执行tcl脚本如下:

set_property SEVERITY {Warning} [get_drc_checks UCIO-1]

set_property SEVERITY {Warning} [get_drc_checks NSTD-1]

然后再Generate Bitstream。

审核编辑:刘清

-

用ST MC Workbench生成代码时报错怎么解决?2024-04-11 320

-

用TouchGFX生成的工程,再使用STM32CubeMX生成MDK工程,下载时报错是怎么回事?2025-03-11 513

-

win10环境下使用vivado生成.bit与.mcs文件2025-10-27 433

-

使用LP Wizard制作Allegro插件封装,在批处理生成焊盘时报错2014-07-17 25325

-

ISE生成bit文件报错ERROR:PhysDesignRules:3682016-11-29 22070

-

如何优化ISE生成的bit文件2019-07-26 1450

-

怎么配置在EDK8.2中生成的.bit文件prom?2019-08-26 1263

-

请问如何在没有静态路由的情况下生成部分比特流?2020-06-04 1321

-

有没有人在启用FreeRTOS的情况下生成CubeMX项目呢?2022-12-27 465

-

请问env生成mdk5工程时报错怎么解决?2023-02-15 683

-

怎么去解决网页在线生成Bootloader时报错的问题?2023-02-17 772

-

mcs生成报错怎么解决?2023-08-12 1184

-

Vivado的安装生成bit文件及烧录FPGA的简要流程教程免费下载2019-06-18 2446

-

使用LabVIEW生成exe时报错的原因及其解决办法2022-09-16 8965

-

使用LabVIEW生成exe时报错如何解决2022-10-28 3934

全部0条评论

快来发表一下你的评论吧 !